## TLE4997A8D Grade1

Programmable Linear Dual Hall Sensor

# **Technical Product Description**

Revision 1.0, 2014-05-21

# Sense & Control

Edition 2014-05-21

Published by Infineon Technologies AG 81726 Munich, Germany © 2014 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

| Revision Histo  | ory                                              |  |

|-----------------|--------------------------------------------------|--|

| Page or Item    | Subjects (major changes since previous revision) |  |

| Revision 1.0, 2 | 2014-05-21                                       |  |

|                 |                                                  |  |

|                 |                                                  |  |

|                 |                                                  |  |

|                 |                                                  |  |

|                 |                                                  |  |

|                 |                                                  |  |

#### Trademarks of Infineon Technologies AG

AURIX $^{\text{TM}}$ , C166 $^{\text{TM}}$ , CanPAK $^{\text{TM}}$ , CIPOS $^{\text{TM}}$ , CIPURSE $^{\text{TM}}$ , EconoPACK $^{\text{TM}}$ , CoolMOS $^{\text{TM}}$ , CoolSET $^{\text{TM}}$ , CORECONTROL $^{\text{TM}}$ , CROSSAVE $^{\text{TM}}$ , DAVE $^{\text{TM}}$ , EasyPIM $^{\text{TM}}$ , EconoBRIDGE $^{\text{TM}}$ , EconoDUAL $^{\text{TM}}$ , EconoPIM $^{\text{TM}}$ , EiceDRIVER $^{\text{TM}}$ , eupec $^{\text{TM}}$ , FCOS $^{\text{TM}}$ , HITFET $^{\text{TM}}$ , HybridPACK $^{\text{TM}}$ , ISOFACE $^{\text{TM}}$ , IsoPACK $^{\text{TM}}$ , MIPAQ $^{\text{TM}}$ , ModSTACK $^{\text{TM}}$ , my-d $^{\text{TM}}$ , NovalithIC $^{\text{TM}}$ , OptiMOS $^{\text{TM}}$ , ORIGA $^{\text{TM}}$ , PRIMARION $^{\text{TM}}$ , PrimePACK $^{\text{TM}}$ , PrimeSTACK $^{\text{TM}}$ , PRO-SIL $^{\text{TM}}$ , PROFET $^{\text{TM}}$ , RASIC $^{\text{TM}}$ , ReverSave $^{\text{TM}}$ , SatrIC $^{\text{TM}}$ , SIEGET $^{\text{TM}}$ , SINDRION $^{\text{TM}}$ , SmartLEWIS $^{\text{TM}}$ , SOLID FLASH $^{\text{TM}}$ , TEMPFET $^{\text{TM}}$ , thinQ! $^{\text{TM}}$ , TRENCHSTOP $^{\text{TM}}$ , TriCore $^{\text{TM}}$ .

#### Other Trademarks

Advance Design System™ (ADS) of Agilent Technologies, AMBA™, ARM™, MULTI-ICE™, KEIL™, PRIMECELL™, REALVIEW™, THUMB™, µVision™ of ARM Limited, UK. AUTOSAR™ is licensed by AUTOSAR development partnership. Bluetooth™ of Bluetooth SIG Inc. CAT-iq™ of DECT Forum. COLOSSUS™, FirstGPS™ of Trimble Navigation Ltd. EMV™ of EMVCo, LLC (Visa Holdings Inc.). EPCOS™ of Epcos AG. FLEXGO™ of Microsoft Corporation. FlexRay™ is licensed by FlexRay Consortium. HYPERTERMINAL™ of Hilgraeve Incorporated. IEC™ of Commission Electrotechnique Internationale. IrDA™ of Infrared Data Association Corporation. ISO™ of INTERNATIONAL ORGANIZATION FOR STANDARDIZATION. MATLAB™ of MathWorks, Inc. MAXIM™ of Maxim Integrated Products, Inc. MICROTEC™, NUCLEUS™ of Mentor Graphics Corporation. Mifare™ of NXP. MIPI™ of MIPI Alliance, Inc. MIPS™ of MIPS Technologies, Inc., USA. muRata™ of MURATA MANUFACTURING CO., MICROWAVE OFFICE™ (MWO) of Applied Wave Research Inc., OmniVision™ of OmniVision Technologies, Inc. Openwave™ Openwave Systems Inc. RED HAT™ Red Hat, Inc. RFMD™ RF Micro Devices, Inc. SIRIUS™ of Sirius Satellite Radio Inc. SOLARIS™ of Sun Microsystems, Inc. SPANSION™ of Spansion LLC Ltd. Symbian™ of Symbian Software Limited. TAIYO YUDEN™ of Taiyo Yuden Co. TEAKLITE™ of CEVA, Inc. TEKTRONIX™ of Tektronix Inc. TOKO™ of TOKO KABUSHIKI KAISHA TA. UNIX™ of X/Open Company Limited. VERILOG™, PALLADIUM™ of Cadence Design Systems, Inc. VLYNQ™ of Texas Instruments Incorporated. VXWORKS™, WIND RIVER™ of WIND RIVER SYSTEMS, INC. ZETEX™ of Diodes Zetex Limited.

Last Trademarks Update 2011-02-24

#### **Table of Contents**

## **Table of Contents**

|                                             | Table of Contents                                                                                                                                                                               |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                             | List of Figures                                                                                                                                                                                 |

|                                             | List of Tables                                                                                                                                                                                  |

| <b>1</b><br>1.1<br>1.2<br>1.3               | Overview         7           Features         7           Target Applications         8           Pin Configuration         8                                                                   |

| <b>2</b><br>2.1<br>2.2<br>2.3<br>2.4<br>2.5 | General       9         Block Diagram       9         Functional Description       9         Principle of Operation       10         Further Notes       10         Transfer Functions       10 |

| 3                                           | Maximum Ratings 11                                                                                                                                                                              |

| 4                                           | Operating Range 12                                                                                                                                                                              |

| <b>5</b><br>5.1                             | Electrical, Thermal and Magnetic Parameters       13         Magnetic Field Direction Definition       14                                                                                       |

| 6                                           | Application Circuit                                                                                                                                                                             |

| <b>7</b><br>7.1<br>7.2                      | PG-TDSO-8-2 Package Outlines17Distance Chip to package17Moisture Sensitivity Level (MSL)17                                                                                                      |

| 8                                           | PG-TDSO-8-2 Package Marking                                                                                                                                                                     |

#### TLE4997A8D Grade1

## List of Figures

## **List of Figures**

| Figure 1-1 | SMD package PG-TDSO-8-2 for the TLE4997A8D Grade1                                   | . 7 |

|------------|-------------------------------------------------------------------------------------|-----|

| Figure 1-2 | Pin Configuration of PG-TDSO-8-2 package                                            | . 8 |

| Figure 2-1 | Block Diagram of the TLE4997A8D Grade1 with the ratiometric analog output interface | . 9 |

| Figure 2-2 | Examples of Operation                                                               | 10  |

| Figure 5-1 | Definition of magnetic field direction of the PG-TDSO-8-2                           | 14  |

| Figure 5-2 | Example of the dual die output signaling                                            | 15  |

| Figure 6-1 | Application Circuit                                                                 | 16  |

| Figure 7-1 | PG-TDSO-8-2 (PG-TDSO-Plastic Green Thin Dual Small Outline), Package Dimensions     | 17  |

| Figure 7-2 | Distance of chip surface to package surface                                         | 17  |

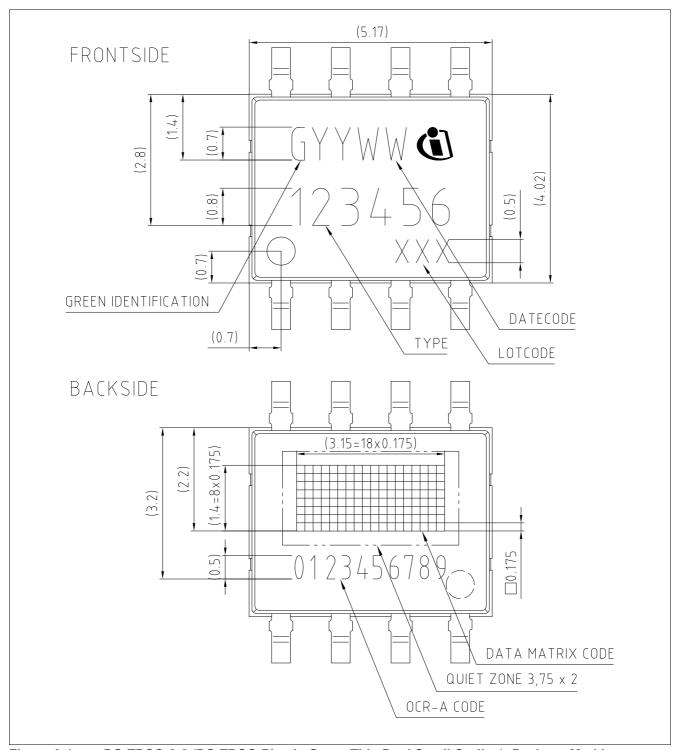

| Figure 8-1 | PG-TDSO-8-2 (PG-TDSO-Plastic Green Thin Dual Small Outline), Package Marking        | 18  |

#### TLE4997A8D Grade1

#### **List of Tables**

## **List of Tables**

| Table 1-1 | Ordering Information                            | 7  |

|-----------|-------------------------------------------------|----|

| Table 1-2 | TLE4997A8D Grade1 Pin Definitions and Functions | 8  |

| Table 3-1 | Absolute Maximum Ratings                        | 11 |

| Table 4-1 | Operating Range                                 | 12 |

| Table 4-2 | Exampe for Ambient Temperature Profile          | 12 |

| Table 5-1 | Electrical Characteristics                      | 13 |

| Table 5-2 | Magnetic Characteristics                        | 14 |

Overview

#### 1 Overview

| Characteristic                  | Supply Voltage | Supply Current | Sensitivity Range         | Interface                       | Temperature    |

|---------------------------------|----------------|----------------|---------------------------|---------------------------------|----------------|

| Programmable Linear Hall Sensor | 4.5~5.5 V      | 7.5 mA         | ±50mT<br>±100mT<br>±200mT | Analog<br>Ratiometric<br>Output | -40°C to 125°C |

Figure 1-1 SMD package PG-TDSO-8-2 for the TLE4997A8D Grade1

#### 1.1 Features

- The TLE4997A8D Grade1 provides an integration of two individual programmable Linear Hall sensor IC's with ratiometric analog output signal in one package.

- 20-bit Digital Signal Processing (DSP)

- · Digital temperature compensation

- 12-bit overall resolution

- Operating automotive temperature range -40°C to 125°C

- Low drift of output signal over temperature and lifetime

- Programmable parameters stored in EEPROM with single-bit error correction:

- Magnetic range and sensitivity (gain), polarity of the output slope

- Offset

- Bandwidth

- Clamping levels

- Customer temperature compensation coefficients for all common magnets

- Memory lock

- Re-programmable until memory lock

- Supply voltage 4.5-5.5 V (4-7 V extended range)

- Operation between -200 mT and +200 mT within three ranges

- · Reverse-polarity and overvoltage protection for all pins

- · Output short-circuit protection

- On-board diagnostics (wire breakage detection, EEPROM error, overvoltage)

- · Digital readout of internal temperature and magnetic field values in calibration mode

- Programming and operation of multiple sensors with common power supply

- Two-point calibration of magnetic transfer function

- Precise calibration without iteration steps

- High immunity against EMC and ESD

#### Table 1-1 Ordering Information

| Product Name      | Marking | Ordering Code | Package     |

|-------------------|---------|---------------|-------------|

| TLE4997A8D Grade1 | -       | -             | PG-TDSO-8-2 |

Overview

### 1.2 Target Applications

- Robust replacement of potentiometers: No mechanical abrasion, resistant to humidity, temperature, pollution and vibration

- Linear and angular position sensing in automotive and industrial applications with highest accuracy requirements

- · Suited for ASIL applications such as pedal position, throttle position and steering torque sensing

- High-current sensing e.g. for battery management or motor control

#### 1.3 Pin Configuration

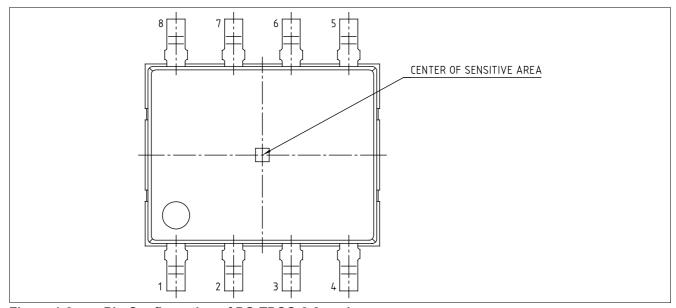

Figure 1-2 shows the location of the Hall elements in the chip pin configuration of the package.

Figure 1-2 Pin Configuration of PG-TDSO-8-2 package

Table 1-2 TLE4997A8D Grade1 Pin Definitions and Functions

| Pin No. | Symbol   | Function                                            |

|---------|----------|-----------------------------------------------------|

| 1       | n/c      | not connected (connection to GND is recommended)    |

| 2       | $V_{DD}$ | Supply voltage / programming interface (top die)    |

| 3       | GND      | Ground (top die)                                    |

| 4       | OUT      | Output / programming interface (top die)            |

| 5       | OUT      | Output / programming interface (bottom die)         |

| 6       | GND      | Ground (bottom die)                                 |

| 7       | $V_{DD}$ | Supply voltage / programming interface (bottom die) |

| 8       | n/c      | not connected (connection to GND is recommended)    |

General

#### 2 General

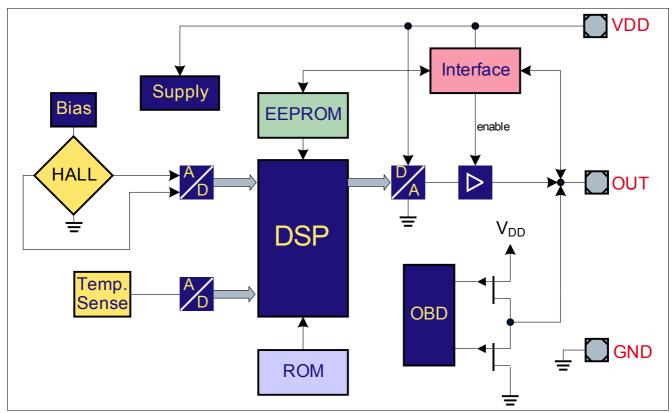

#### 2.1 Block Diagram

Figure 2-1 shows is a simplified block diagram.

Figure 2-1 Block Diagram of the TLE4997A8D Grade1 with the ratiometric analog output interface

#### 2.2 Functional Description

The linear Hall IC TLE4997A8D Grade1 has been designed specifically to meet the requirements of highly accurate angle and position detection, as well as for current measurement applications.

The sensor provides a ratiometric analog output voltage, which is ideally suited to Analog-to-Digital (A/D) conversion with the supply voltage as a reference.

The IC is produced in BiCMOS technology with high voltage capability and also provides reverse polarity protection.

Digital signal processing using a 16-bit DSP architecture together with digital temperature and analog stress compensation guarantees excellent stability over the whole temperature range and life time.

The minimum overall resolution is 12 bits. Nevertheless, some internal stages work with resolutions up to 20 bits.

General

#### 2.3 Principle of Operation

- · A magnetic flux is measured by a Hall-effect cell

- The output signal from the Hall-effect cell is converted from analog to digital signals

- · The chopped Hall-effect cell and continuous-time A/D conversion ensure a very low and stable magnetic offset

- A programmable low-pass filter to reduce noise

- The temperature is measured and A/D converted

- Temperature compensation is done digitally using a second-order function

- · Digital processing of the output value is based on zero field and sensitivity value

- The output value range can be clamped by digital limiters

- · The final output value is D/A converted

- The output voltage is proportional to the supply voltage (ratiometric DAC)

- An On-Board-Diagnostics (OBD) circuit connects the output to V<sub>DD</sub> or GND in case of errors

#### 2.4 Further Notes

Product qualification is based on "AEC Q100 Rev. G" (Automotive Electronics Council - Stress test qualification for integrated circuits).

#### 2.5 Transfer Functions

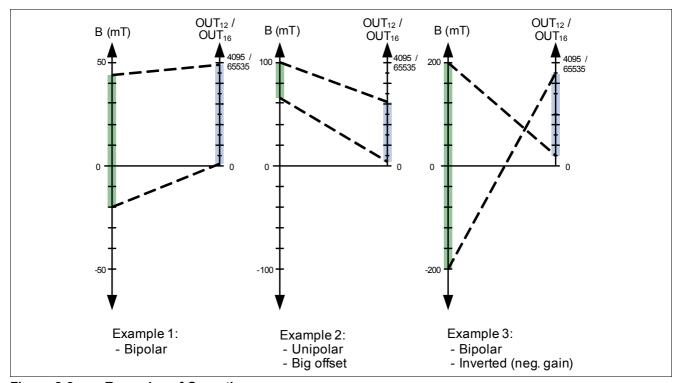

The examples in **Figure 2-2** show how different magnetic field ranges can be mapped to the desired output value ranges.

- · Polarity Mode:

- Bipolar: Magnetic fields can be measured in both orientations. The limit points do not necessarily have to be symmetrical around the zero field point

- Unipolar: Only north- or south-oriented magnetic fields are measured

- Inversion: Both gain can be set to positive values, negative values or positive/negative values.

Figure 2-2 Examples of Operation

**Maximum Ratings**

## 3 Maximum Ratings

Table 3-1 Absolute Maximum Ratings

| Parameter                                                       | Symbol             |                   | Values Unit Note / T | Note / Test Condition |    |                                                                      |

|-----------------------------------------------------------------|--------------------|-------------------|----------------------|-----------------------|----|----------------------------------------------------------------------|

|                                                                 |                    | Min.              | Тур.                 | Max.                  |    |                                                                      |

| Junction temperature                                            | TJ                 | - 40              | _                    | 140 <sup>1)</sup>     | °C | Grade 1                                                              |

| Voltage on $V_{DD}$ pin with respect to ground ( $V_{SS}$ )     | V <sub>DD</sub>    | -20 <sup>2)</sup> | _                    | 203)                  | V  | <sup>4)</sup> R <sub>THja</sub> ≤ 150 K/W                            |

| Supply current @ overvoltage                                    | I <sub>DDov</sub>  | _                 | _                    | 52                    | mA |                                                                      |

| Supply current @ reverse voltage                                | I <sub>DDrev</sub> | -75               | _                    | _                     | mA |                                                                      |

| Voltage on output pin with respect to ground (V <sub>SS</sub> ) | V <sub>OUTov</sub> | -16 <sup>5)</sup> | _                    | 16 <sup>3)</sup>      | V  | $R_{THja} \le 150 \text{ K/W}$<br>$V_{OUT} \text{ may be } > V_{DD}$ |

| Magnetic field                                                  | B <sub>MAX</sub>   | -                 | _                    | 1                     | Т  |                                                                      |

| ESD protection                                                  | V <sub>ESD</sub>   | -                 |                      | +/- 2                 | kV | According HBM<br>JESD22-A114-B <sup>6)</sup>                         |

<sup>1)</sup> For limited time of 96 h. Depends on customer temperature lifetime cycles. Please ask for support by Infineon.

<sup>2)</sup> max 24 h @ -40°C ≤ Ta < 30°C max 10 min. @ 30°C ≤ Ta < 80°C max 30 sec. @ 80°C ≤ Ta < 125°C

<sup>3)</sup> max. 24 h @  $T_J$  < 80°C.

<sup>4)</sup> Guaranteed by laboratory characterization, tested at ±18V.

<sup>5)</sup> Max. 1 ms @  $T_J$  < 30°C; -8.5 V for 100 h @  $T_J$  < 80°C.

<sup>6) 100</sup> pF and 1.5 k $\Omega$

**Operating Range**

## 4 Operating Range

The following operating conditions must not be exceeded in order to ensure correct operation of the TLE4997A8D Grade1. All parameters described in the following sections refer to these operating conditions if applicable or unless otherwise indicated.

Table 4-1 Operating Range

| Parameter                          | Symbol           | Values                 |      |      | Unit | Note / Test Condition            |

|------------------------------------|------------------|------------------------|------|------|------|----------------------------------|

|                                    |                  | Min.                   | Тур. | Max. |      |                                  |

| Supply voltage                     | $V_{DD}$         | 4.5                    | _    | 5.5  | V    |                                  |

|                                    |                  | <b>4</b> <sup>1)</sup> | _    | 7    | V    | Extended range                   |

| Output current                     | I <sub>OUT</sub> | -1                     | _    | 1    | mA   | 2)                               |

| Load resistance                    | R <sub>L</sub>   | 10                     | _    | _    | kΩ   | Pull-down to GND                 |

|                                    |                  | 10                     | _    | _    |      | Pull-up to V <sub>DD</sub>       |

| Load capacitance                   | C <sub>L</sub>   | 0                      | _    | 210  | nF   |                                  |

| Junction temperature <sup>3)</sup> | T <sub>J</sub>   | - 40                   | _    | 140  | °C   | Example for profil see Table 4-2 |

<sup>1)</sup> May have reduced EMC robustness.

Note: Keeping signal levels within the limits described in this table ensures operation without overload conditions.

Table 4-2 Example for Ambient Temperature Profile 1)

| Temperature /°C | Active Lifetime / h |

|-----------------|---------------------|

| -40°C<20°C      | 100                 |

| 20°C <60°C      | 600                 |

| 60°C <90°C      | 8000                |

| 90°C <110°C     | 2000                |

| 110°C <125°C    | 1000                |

| 125°C           | 300                 |

<sup>1)</sup> This lifetime statement is an anticipation based on an extrapolation of Infineon's qualification test results.

<sup>2)</sup> For  $V_{OUT}$  within the range of 5% ... 95% of  $V_{DD}$ .

<sup>3)</sup>  $R_{THja} \le 150 \text{ K/W}.$

**Electrical, Thermal and Magnetic Parameters**

### 5 Electrical, Thermal and Magnetic Parameters

Table 5-1 Electrical Characteristics

| Parameter                                    | Symbol             | Values |      |          | Unit                 | Note / Test Condition                                  |  |

|----------------------------------------------|--------------------|--------|------|----------|----------------------|--------------------------------------------------------|--|

|                                              |                    | Min.   | Тур. | Max.     |                      |                                                        |  |

| Output voltage range                         | V <sub>OUT</sub>   | 5<br>6 | _    | 95<br>94 | % of V <sub>DD</sub> | for $T_A \le 120^{\circ}C$<br>for $T_A > 120^{\circ}C$ |  |

| Supply current                               | I <sub>DD</sub>    | 3      | 7.5  | 10       | mA                   | 1)                                                     |  |

| Output current @ OUT shorted to supply lines | I <sub>OUTsh</sub> | -30    | _    | 30       | mA                   | for operating supply voltage range only                |  |

| Zero field voltage                           | $V_{ZERO}$         | -100   | _    | 100      | %                    | of V <sub>DD</sub> <sup>2)</sup>                       |  |

| Zero field voltage drift                     | $\Delta V_{ZERO}$  | -10    | _    | 10       | mV                   | In lifetime <sup>3)</sup>                              |  |

|                                              |                    | -10    | _    | 10       | mV                   | error band over temp. <sup>3)</sup>                    |  |

| Ratiometry error                             | E <sub>RAT</sub>   | -0.25  | _    | 0.25     | %                    | of V <sub>DD</sub> <sup>4)5)</sup>                     |  |

| Thermal resistance                           | R <sub>thJA</sub>  | _      | 150  | _        | K/W                  | junction to air                                        |  |

| PG-TDSO-8-2                                  | R <sub>thJC</sub>  | _      | 85   | _        | K/W                  | junction to case                                       |  |

| Power-on time <sup>6)</sup>                  | t <sub>Pon</sub>   | _      | _    | 1        | ms                   | $\Delta V_{OUT} \le \pm 5\%$ of $V_{DD}$               |  |

|                                              |                    |        | _    | 10       |                      | $\Delta V_{OUT} \le \pm 1\%$ of $V_{DD}$               |  |

| Power-on reset level                         | $V_{\rm DDpon}$    | 2      | _    | 4        | V                    |                                                        |  |

| Output DAC quantization                      | $\Delta V_{OUT}$   |        | 1.22 |          | mV                   | @ V <sub>DD</sub> = 5 V                                |  |

| Output DAC resolution                        | _                  |        | 12   |          | bit                  |                                                        |  |

| Output DAC bandwidth                         | f <sub>DAC</sub>   | _      | 3.2  | _        | kHz                  | interpolation filter                                   |  |

| Differential non-linearity                   | DNL                | -1     | _    | 1        | LSB                  | of output DAC                                          |  |

| Output noise (rms)                           | V <sub>noise</sub> | _      | _    | 3        | mV                   | 7)                                                     |  |

| Signal delay                                 | t <sub>SD</sub>    | _      | _    | 250      | μs                   | @ 100 Hz <sup>8)</sup>                                 |  |

- 1) Also in extended  $V_{DD}$  range. For  $V_{OUT}$  within the range of 5%... 95% of  $V_{DD}$ ,  $I_{OUT}$ = 0mA.

- 2) Programmable in steps of 1.22 mV (@  $V_{DD}$  = 5 V).

- 3) For Sensitivity S ≤ 25 mV/mT. For higher sensitivities the magnetic offset drift is dominant. This means that for the pre calibrated (typical) 60mV/mT sensitivity the typical output drift might be given due to the allowed magnetic offset tolerance up to ±0.4mT x 60 mV/mT = ±24 mV.

- 5) For the maximum error in the extended voltage range

- 6) Response time to set up output data at power on when a constant field is applied. The first value given has a ±5% error, the second value has a ±1% error.

- 7) 100 mT range, sensitivity 60 mV/mT, internal LP filter 244 Hz, B = 0 mT, T = 25 °C.

- 8) A sinusoidal magnetic field is applied,  $V_{OUT}$  shows amplitude of 20% of  $V_{DD}$ , no LP filter is selected.

Note: Take care of possible voltage drops on the  $V_{DD}$  and  $V_{OUT}$  line degrading the result. Ideally, both values are acquired and their ratio is calculated to gain the highest accuracy. This method should be used especially during calibration.

#### **Electrical, Thermal and Magnetic Parameters**

#### **Magnetic Parameters**

Table 5-2 Magnetic Characteristics

| Parameter                               | Symbol          |       | Values             |      |       | Note / Test Condition                |  |

|-----------------------------------------|-----------------|-------|--------------------|------|-------|--------------------------------------|--|

|                                         |                 | Min.  | Тур.               | Max. |       |                                      |  |

| Sensitivity                             | S <sup>1)</sup> | ±12.5 | _                  | ±300 | mV/mT | programmable <sup>2)</sup>           |  |

| Sensitivity error band over temperature | S <sub>E</sub>  | -2    |                    | 2    | %     | 3)                                   |  |

| Magnetic field range                    | MFR             | ±50   | ±100 <sup>4)</sup> | ±200 | mT    | programmable <sup>5)</sup>           |  |

| Integral nonlinearity                   | INL             | _     | _                  | ±15  | mV    | $= \pm 0.3\% \text{ of V}_{DD}^{6)}$ |  |

| Magnetic offset                         | B <sub>OS</sub> | _     | ±100               | ±400 | μТ    | 7)8)9)                               |  |

| Magnetic offset drift                   | $\Delta B_{OS}$ | _     | ±1                 | ±5   | μT/°C | error band <sup>8)</sup>             |  |

- 1) Defined as  $\Delta V_{OUT} / \Delta B$ , @  $V_{DD} = 5 \text{ V}$  and  $T_{J} = 25 ^{\circ}\text{C}$ .

- 2) Programmable in steps of 0.024%.

- 3) Residual sensitivity error band over temperature when using minimum 2 temperatures. Valid for 0h in dry state only. Dry is defined after following baking process: 60minutes at T=125°C.

- 4) This range is also used for temperature and offset pre-calibration of the IC.

- 5) Depending on offset and gain settings, the output may already be saturated at lower fields.

- 6) INL =  $V_{OUT}$   $V_{OUT}$ , Ise with  $V_{OUT}$ , Ise = least square error fit of  $V_{OUT}$ . Valid in the range (5% of  $V_{DD}$ ) <  $V_{OUT}$  < (95% of  $V_{DD}$ ) for TJ ≤ 105°C

- 7) In operating temperature range and over lifetime.

- 8) For Sensitivity S > 25 mV / mT. For lower sensitivities, the zero field voltage drift is dominant.

- 9) Measured at ±100 mT range.

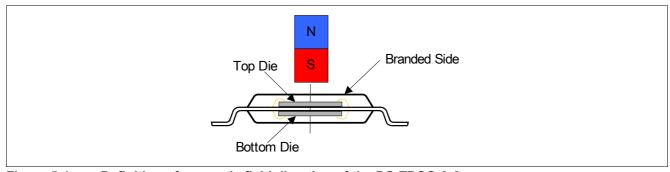

#### 5.1 Magnetic Field Direction Definition

Figure 5-1 Definition of magnetic field direction of the PG-TDSO-8-2

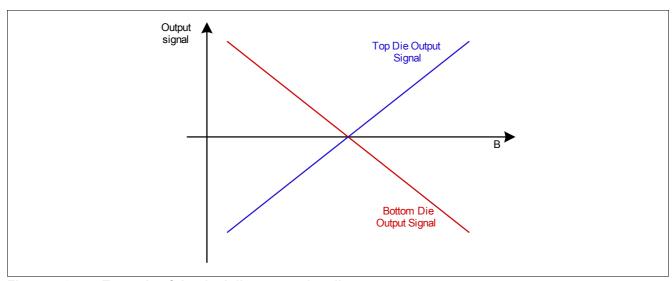

Without reconfiguration the bottom die measures the inverted field value of the top die. This leads to a characteristics as shown in **Figure 5-2**.

#### **Electrical, Thermal and Magnetic Parameters**

Figure 5-2 Example of the dual die output signaling

**Application Circuit**

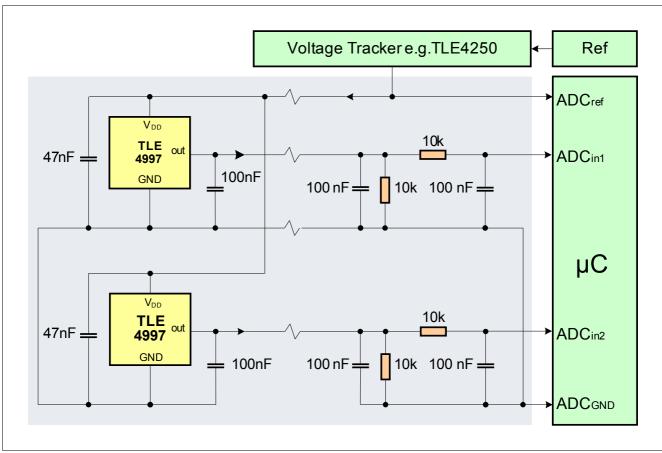

## 6 Application Circuit

shows the connection of two Linear Hall sensors to a micro controller.

Figure 6-1 Application Circuit

Note: For calibration and programming, the interface has to be connected directly to the OUT pin.

**PG-TDSO-8-2 Package Outlines**

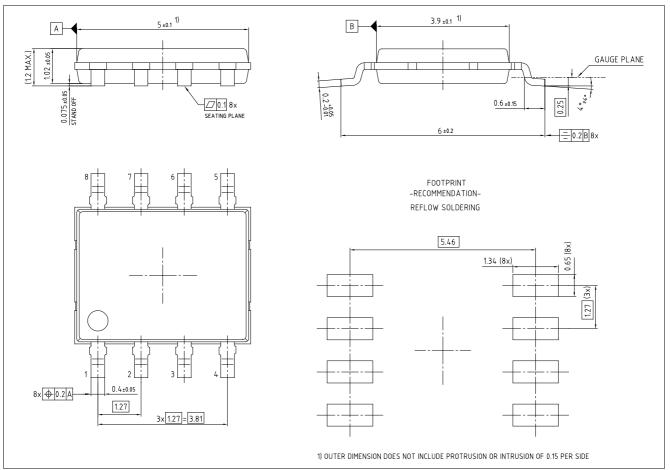

## 7 PG-TDSO-8-2 Package Outlines

Figure 7-1 PG-TDSO-8-2 (PG-TDSO-Plastic Green Thin Dual Small Outline), Package Dimensions

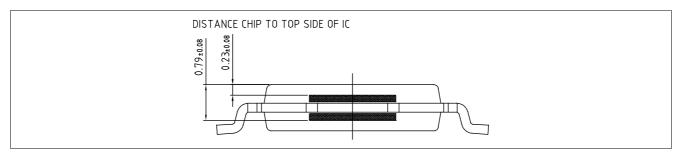

#### 7.1 Distance Chip to package

Figure 7-2 shows the distance of the chip surface to the PG-TDSO-8-2 surface.

Figure 7-2 Distance of chip surface to package surface

#### 7.2 Moisture Sensitivity Level (MSL)

The PG-TDSO-8-2 fulfills the MSL level 3 according to IPC/JEDEC J-STD-033B.1.

PG-TDSO-8-2 Package Marking

## 8 PG-TDSO-8-2 Package Marking

Figure 8-1 PG-TDSO-8-2 (PG-TDSO-Plastic Green Thin Dual Small Outline), Package Marking

w w w .in fineon.com