PN结隔离(JI)栅极驱动器

用于IGBT和MOSFET的PN结隔离(JI)高压电平转换栅极驱动器

英飞凌p-n结隔离(JI)技术是一项成熟、可靠和行业标准级的MOS/CMOS制造工艺。英飞凌专有的HVIC

和抗闩锁CMOS技术可打造出坚固的单片式构造。先进的制造工艺可面向特定的电机控制和开关电源应用,打造出性价比最佳的单片式高压和低压电路结构。

JI电平转换高压栅极驱动器IC系列提供过流保护、关断、故障报告、使能、运算放大器(OPAMP)、DESAT、可编程死区时间、击穿保护、独立的灌电流和拉电流输出、低欠压闭锁 (UVLO) (5V)、自激振荡等功能。

我们提供通过工业和汽车认证的p-n结隔离 (JI) 栅极驱动器 IC 。

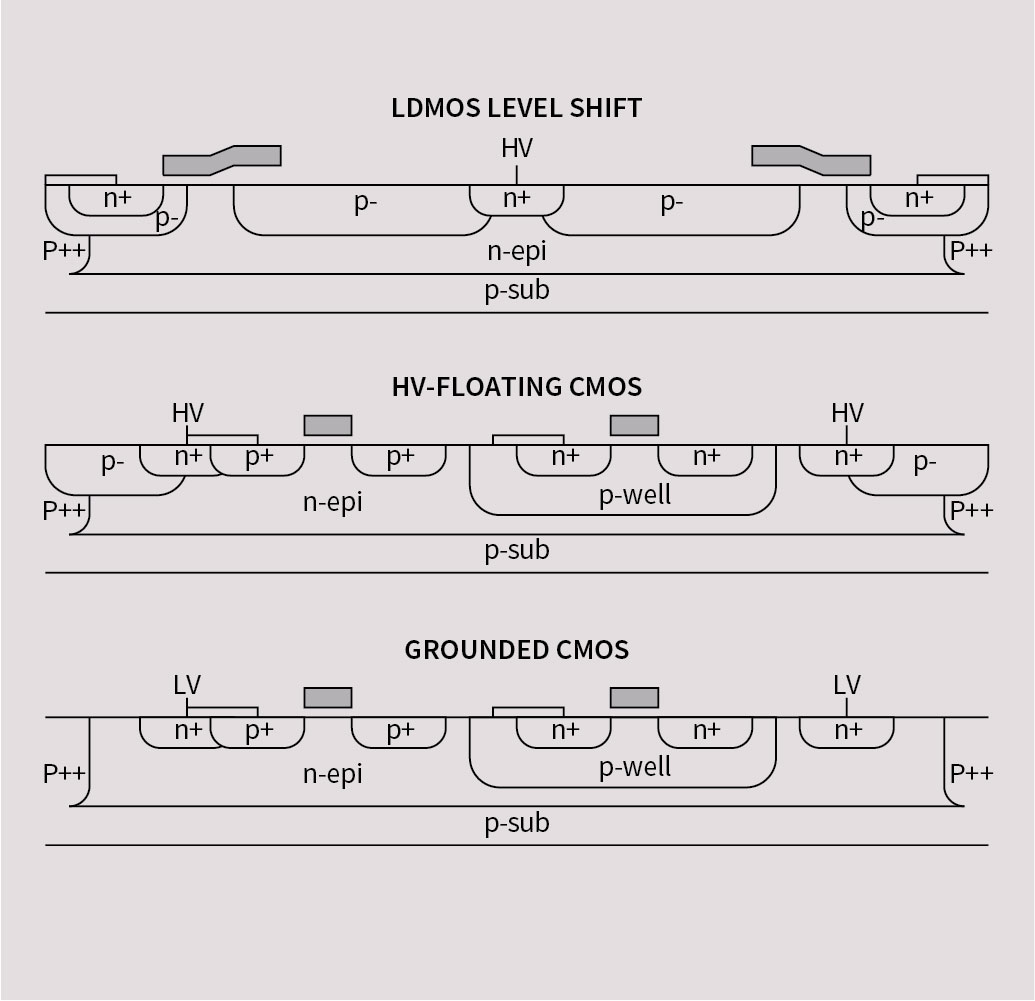

自从1989年国际整流器公司(IR)率先推出首款单片式产品以来,高压集成电路(HVIC)技术就开始 利用获得专利的和专有单片式结构集成双极器件、CMOS及横向DMOS器件,在600 V和1200 V的运 行偏置电压下,击穿电压分别高于700 V和1400 V。

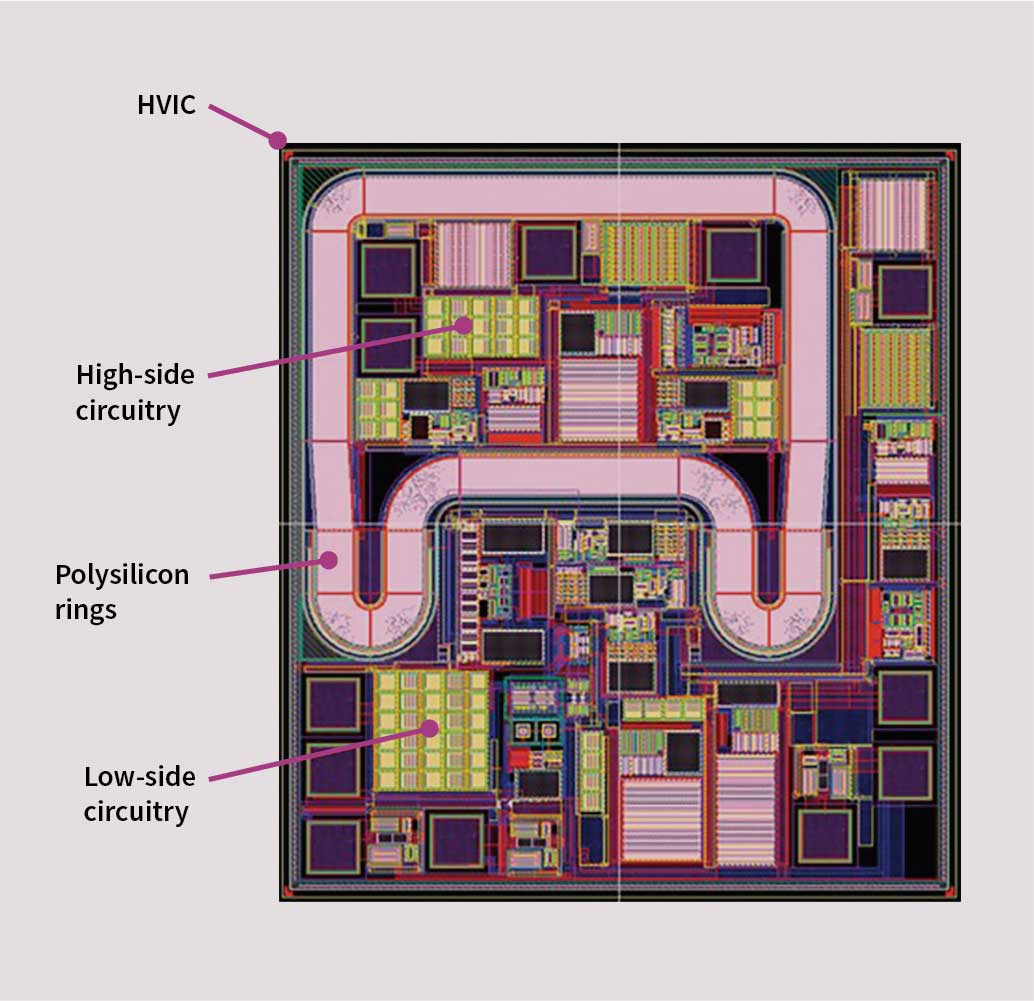

该混合信号HVIC技术可用于构建高压电平转换电路,以及低压模拟电路和数字电路。因为能将高压电路(位于由多晶硅环形成的“井”中)——可“浮动”600 V或1200 V——置于能够避开其它低压电路,高边功率MOSFET或IGBT的同一硅片上,其广泛存在于各种常见的离线电路拓扑中,包括降压 电路、同步升压电路、半桥电路、全桥电路和三相电路等等。

这些拥有浮控开关的HVIC门极驱动非常适合需要高边、半桥和三相驱动的拓扑。

同样令您感兴趣的内容

推荐文档

You will have a glimpse of the different gate driver technologies available at Infineon and their benefits.

For a better understanding we will take a look at the optimization of external gate resistors to drive MOSFETs in a given application.

With this training, you will learn how to calculate a gate resistance value for an IGBT application, how to identify suitable gate driver ICs based on peak current and power dissipation requirements, and how to fine-tune the gate resistance value in laboratory environment based on worst case conditions.

We offer a large portfolio of level shift high voltage gate drivers – silicon-on-insulator (SOI) and junction isolated (JI) technologies. Learn about the advantages of Infineon SOI gate driver: integrated bootstrap diode, Low level-shift losses, saving space and cost, and negative VS robustness.