# ICE3Axx65LJ/ICE3Bxx65LJ

CoolSET<sup>TM</sup> F3 Latch & Jitter version Design Guide

## Power Management & Supply

Never stop thinking.

Edition 2009-10-31 Published by Infineon Technologies Asia Pacific, 168 Kallang Way, 349253 Singapore, Singapore © Infineon Technologies AP 2004. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

#### ICE3AXX65LJ/ 3BXX65LJ

| <b>Revision History:</b> | 2009-10                                      | V1.1 |  |  |  |  |  |  |  |

|--------------------------|----------------------------------------------|------|--|--|--|--|--|--|--|

| Previous Version:        | V1.0                                         |      |  |  |  |  |  |  |  |

| Page                     | Subjects (major changes since last revision) |      |  |  |  |  |  |  |  |

| 8                        | Add precaution for the start up sequence.    |      |  |  |  |  |  |  |  |

|                          |                                              |      |  |  |  |  |  |  |  |

|                          |                                              |      |  |  |  |  |  |  |  |

|                          |                                              |      |  |  |  |  |  |  |  |

|                          |                                              |      |  |  |  |  |  |  |  |

|                          |                                              |      |  |  |  |  |  |  |  |

|                          |                                              |      |  |  |  |  |  |  |  |

|                          |                                              |      |  |  |  |  |  |  |  |

CoolSET<sup>™</sup> F3 Latch & Jitter version Design Guide: License to Infineon Technologies Asia Pacific Pte Ltd

Kok Siu Kam Eric Jeoh Meng Kiat

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

ap-lab.admin@infineon.com

AN-PS0008

#### **Table of Contents**

| Table of | able of Contents                                     |    |

|----------|------------------------------------------------------|----|

| 1        | Introduction                                         | 5  |

| 2        | List of Features                                     | 5  |

| 3        | Package                                              | 5  |

| 4        | Block Diagram                                        | 6  |

| 5        | Typical Application Circuit                          | 7  |

| 6        | Function Description                                 | 8  |

| 6.1      | Startup Cell                                         |    |

| 6.2      | Soft Start and Normal Operation                      | 8  |

| 6.3      | Active Burst Mode                                    | 9  |

| 6.3.1    | Entering Active Burst Mode                           |    |

| 6.3.2    | Working in Active Burst Mode                         |    |

| 6.3.3    | Leaving Active Burst Mode                            |    |

| 6.3.4    | V <sub>cc</sub> supply during burst mode             |    |

| 6.4      | Switching frequency modulation                       |    |

| 6.5      | Propagation delay compensation                       |    |

| 6.6      | Protection Features                                  |    |

| 6.6.1    | Auto Restart Mode                                    |    |

| 6.6.2    | Latched Off Mode                                     |    |

| 6.6.3    | Blanking Time for over load protection               | 15 |

| 7        | Layout Recommendation                                | 16 |

| 8        | CoolSET <sup>™</sup> F3 Latch & Jitter version Table | 16 |

| 9        | References                                           | 16 |

## 1 Introduction

The **ICE3A(B)xx65LJ** is the further development of the third generation CoolSET<sup>™</sup>-F3. It is a PWM controller with power MOSFET together in a DIP-8 package. The switching frequency is running at 100(67) KHz and it targets for DVD player, set-top box, portable game console, auxiliary power supply, etc.

The **ICE3A(B)xx65LJ** adopts the BICMOS technology and provides a wider Vcc operating range up to 26V. It inherits the proven good features of CoolSET<sup>™</sup>-F3 such as the active burst mode achieving the lowest standby power, the propagation delay compensation making the most precise current limit control in wide input voltage range, etc. In addition, it also adds on some useful features such as built-in soft start time, built-in basic with extendable blanking time for over load protection and built-in switching frequency modulation (frequency jittering), latch off enable pin, etc.

In this application note, functions of the device are described in detail with formula and its performance is shown with the test waveforms. The description of other related information such as DCM/CCM mode operating principles and slope compensation and the detailed design procedure are shown in the application note "AN-SMPS-ICE2xXXX-1".

## 2 List of Features

650V avalanche rugged CoolMOS™ with built in switchable Startup Cell

Active Burst Mode for lowest Standby Power

BiCMOS technology provide wide Vcc voltage range

Fast load jump response in Active Burst Mode

100kHz fixed switching frequency with frequency modulation

Latched Off mode for over temperature, Vcc over voltage and short winding protection

Auto Restart Mode for over load protection, Open Loop protection and Vcc under voltage protection

Built-in soft start time

Built-in and extendable blanking window for short duration peak current

External latch off enable pin

Propagation delay compensation provides accurate primary current limit

Switching frequency modulation and soft gate driving for low EMI

## 3 Package

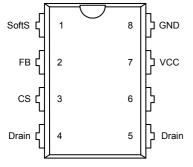

The package for CoolSET<sup>™</sup>-F3 Latch and Jitter mode product is DIP-8.

Figure 1 DIP-8 package

Application Note

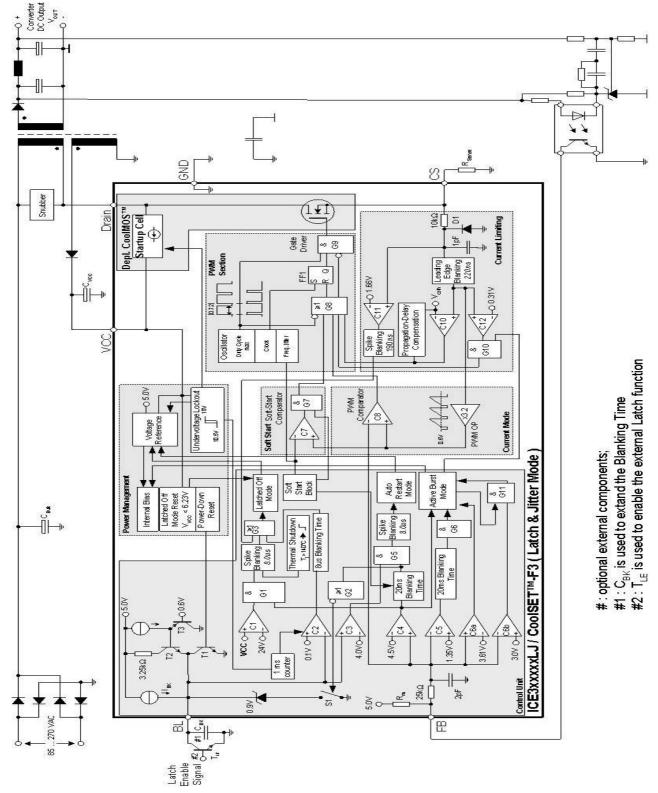

4 Block Diagram

Figure 2 Block Diagram of CoolSET™-F3 ICE3XXX65LJ

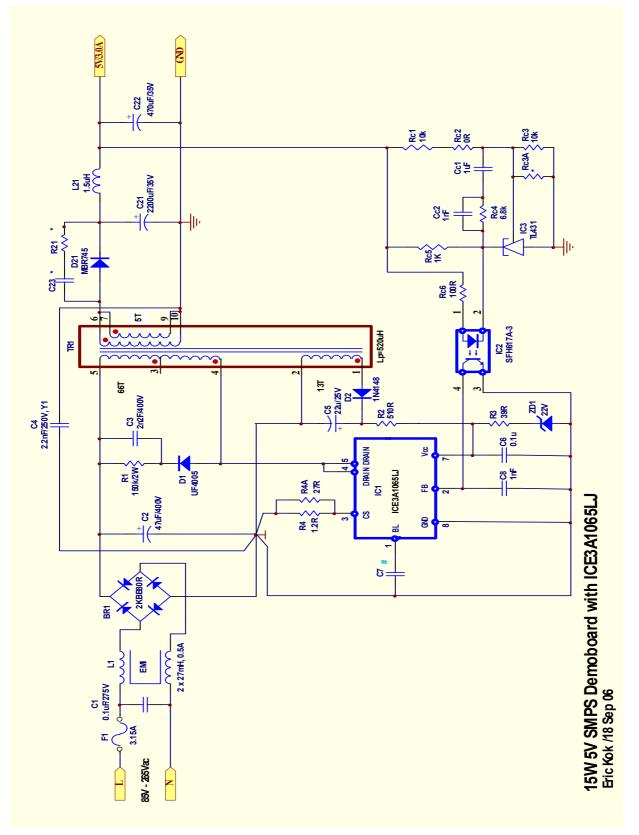

## 5 Typical Application Circuit

Figure 3 Typical application circuit with CoolSET™-F3, ICE3A1065LJ 15W 5V

## 6 Function Description

#### 6.1 Startup Cell

The Startup Cell delivers a constant charge current of  $I_{VCCCharge}$ =0.9mA to charge up the V<sub>CC</sub> capacitor C<sub>Vcc</sub> at V<sub>CC</sub> pin. When V<sub>CC</sub> exceeds the on-threshold V<sub>CCon</sub>=18V, the bias circuit is switched on. The Startup Cell is switched off by UVLO for reducing the power loss. The startup delay time, t<sub>DELAY</sub>, is independent from the AC line input voltage. It can be estimated by the equation (1):

$$t_{DELAY} = \frac{V_{VCCon} \cdot C_{Vcc}}{I_{Vcc\_Charge} - I_{Vcc\_Start}}$$

(1)

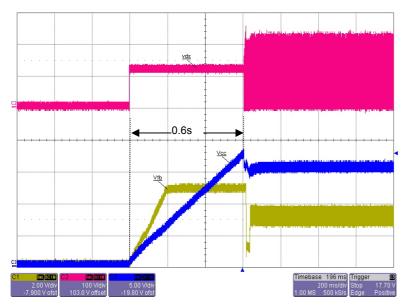

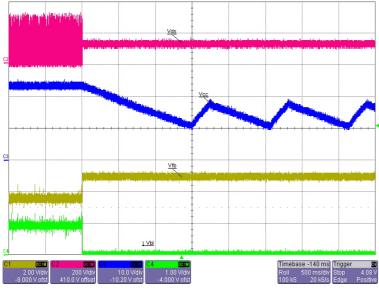

where,  $I_{Vcc\_Start}$  is the supply current when IC is in off state. Figure 4 shows the startup time delay at 85VAC input. (PIs refer to the datasheet for the symbol used in the equation )

Figure 4 The startup delay time at AC line input voltage of 85V.

Precaution : For a typical application, start up should be VCC ramps up first, other pin (such as FB pin) voltage will follow VCC voltage to ramp up. It is recommended not to have any voltage on other pins (such as FB; BA and CS) before VCC ramps up.

#### 6.2 Soft Start and Normal Operation

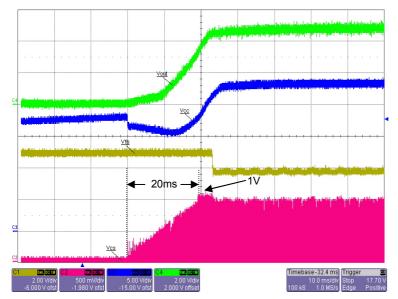

When the IC is turned on after the Startup Delay time, a digital soft start circuit is activated. A gradually increased soft start voltage is emitted by the digital soft start circuit, which in turn increases the duty cycle accordingly. The soft start control voltage is increased with the increasing of count number in the digital counter of the soft start circuit. The soft start time is set at 20ms. When the soft start time ends, IC goes into normal mode and the duty cycle is dependent on the FB signal. Figure 5 shows the soft start behaviour at 85VAC input. It can be seen that the primary peak current slowly increase to the maximum in the soft start period. After soft start stage, IC goes into normal operation with the conventional primary peak current control scheme. Please refer to "AN-SMPS-ICE2xXXXX-1" for the details of normal operation.

Figure 5 Soft start at AC line input voltage of 85V

#### 6.3 Active Burst Mode

The IC provides an Active Burst Mode function at no load or low load conditions to enable the system to achieve the lowest standby power requirement of less than 100mW. Active Burst Mode means the IC is always in the active state and can therefore immediately response to any changes on the FB signal,  $V_{FB}$ .

#### 6.3.1 Entering Active Burst Mode

Because of the current mode control scheme, the feedback voltage  $V_{FB}$  actually controls the power delivery to output. When the output load is getting lower, the feedback voltage  $V_{FB}$  drops. If it stays below 1.35V for a pre-set time frame of 20ms, the IC enters into the burst mode operation. The threshold power to enter burst mode is:

$$P_{BURST\_enter} = 0.5 \cdot L_P \cdot \left(\frac{V_{FBC5} - V_{Offset-Ramp}}{R_{sense} \cdot A_V}\right)^2 \cdot f_{SW}$$

(2)

where, L<sub>P</sub> is the transformer primary inductance, V<sub>FBC5</sub>=1.35V is the feedback voltage at which the system starts to burst, V<sub>Offset-Ramp</sub>=0.6V is the maximum level of the internal Voltage Ramp on which the amplified current ramp signal of the PWM-OP is superimposed, A<sub>V</sub> =3.2 is the internal PWM-OP gain, R<sub>sense</sub> is the current sense resistor, f<sub>SW</sub> is the switching frequency. Figure 6 shows the test waveform with the load drop from full load to light load. After blanking time IC goes into burst mode.

Figure 6 Entering Burst Mode

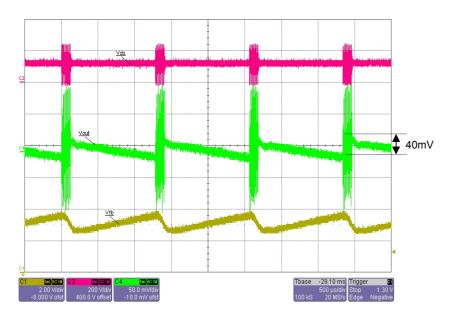

#### 6.3.2 Working in Active Burst Mode

During active burst mode, the IC is constantly monitoring the output voltage by feedback pin,  $V_{FB}$ , which controls burst duty cycle and burst frequency. The burst "on" starts when  $V_{FB}$  reaches 3.61V and stops when  $V_{FB}$  is down to 3.0V. During burst "on", the primary current limit is set to only 31% of maximum peak current ( $V_{CS}$ =0.31V) to reduce the conduction losses and to avoid audible noise. The FB voltage is changing like a saw tooth between 3.0V and 3.61V.The corresponding secondary output ripple (peak to peak) is regulated as below:

$$V_{out\_ripple\_pp} = \frac{R_{opto}}{R_{FB} \cdot G_{opto} \cdot G_{TL431}} \cdot \Delta V_{FB}$$

(3)

where,  $R_{opto}$  is the resistor in series with opto-coupler at the secondary side to limit the opto-coupler current,  $R_{FB}$  is the IC internal pull up resistor connected to FB Pin (refer to Figure 2),  $G_{opto}$  is the current transfer gain of opto-coupler,  $G_{TL431}$  is the voltage transfer gain between the comparator TL431 output and  $V_{out}$ ,  $\Delta V_{FB}$ =3.61-3.0=0.61V is the ripple on the  $V_{FB}$  during burst operation.

The leaving burst power threshold, i.e. maximum power to be handled during burst operation is:

$$P_{burst\_max} = 0.5 \cdot L_P \cdot (0.31 \cdot i_{peak\_max})^2 \cdot f_{SW} = 0.5 \cdot L_P \cdot (0.31 \cdot \frac{V_{CS\_max}}{R_{sense}})^2 \cdot f_{SW} = 0.0961 \cdot P_{max}$$

(4)

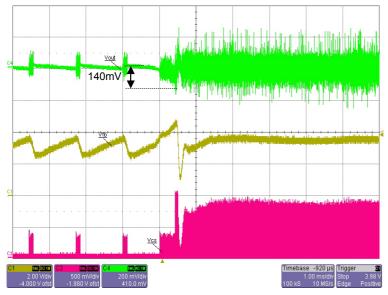

Where,  $i_{peak_{max}}$  is the maximum primary peak current,  $V_{CS_{max}}$  is the cycle by cycle current limit threshold at CS pin,  $P_{max}$  is the maximum output power of the power supply. It can be seen that the maximum power in burst mode is around 9.61% of  $P_{max}$ . Figure 7 shows the test waveform of burst mode at light load. It can be seen that the burst ripple is well regulated to be 40mV and it is independent on the output power.

Figure 7 working in Burst Mode at light load

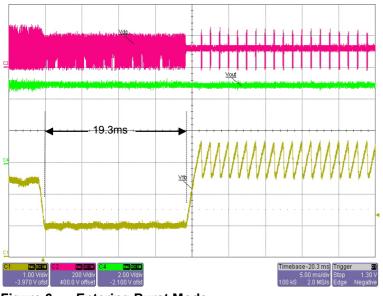

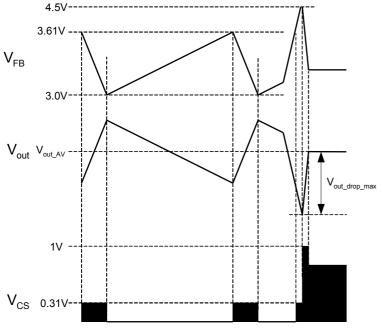

#### 6.3.3 Leaving Active Burst Mode

When the output load is increasing to be higher than  $P_{burst_max}$ ,  $V_{out}$  will drop a little bit and  $V_{FB}$  will rise up fast to 4.5V. The system leaves burst mode immediately when  $V_{FB}$  reaches 4.5V. Once system leaves burst mode, the current sense voltage limit,  $V_{CS_MAX}$ , is released to 1V, the feedback voltage  $V_{FB}$  swings back to the required level. The timing diagram of leaving burst mode is shown in Figure 8.

Figure 8 the timing diagram of leaving burst mode

The maximum  $V_{out}$  drop during the mode transition is

$$V_{out\_drop\_max} = \frac{R_{opto}}{R_{FB} \cdot G_{opto} \cdot G_{TL431}} \cdot (4.5 - \frac{3.0 + 3.61}{2}) = \frac{1.195 \cdot R_{opto}}{R_{FB} \cdot G_{opto} \cdot G_{TL431}}$$

(5)

**Application Note**

Figure 9 shows the waveform to leave burst mode with load jump from light load to full load. The output voltage drop during the transition is about 140mV.

Figure 9 test waveform of leaving burst mode

### 6.3.4 V<sub>cc</sub> supply during burst mode

The supply voltage for V<sub>CC</sub> has to be designed so that it always stays above V<sub>VCCoff</sub> limit during burst mode, even at no load. This can lead to a substantial high voltage at V<sub>CC</sub> pin during maximum load operation. The circuit configuration for V<sub>CC</sub> in Figure 3, which consists of C5, R2, R3, ZD1 and C6, is to ensure that the V<sub>CC</sub> will never exceed 26V under any operation conditions.

## 6.4 Switching frequency modulation

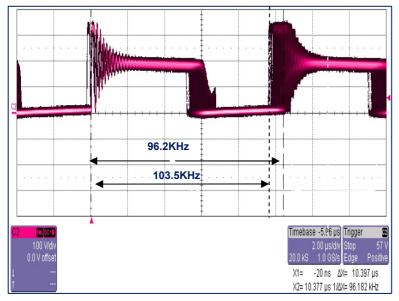

The IC is running at fixed frequency of 100KHz with jittering frequency at +/-4KHz in a switching modulation period of 4ms. This kind of frequency modulation can effectively help to obtain a low noise level conduction EMI measurement. The measurement jittering frequency is 96.2KHz ~ 103.5KHz (Figure 10).

Figure 10 Switching frequency jittering

12

#### 6.5 **Propagation delay compensation**

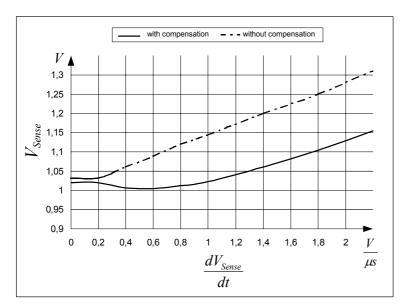

It is observed that the maximum input power will change with input voltage. This is due to the propagation delay of the controller in different dl/dt of the input voltage. The power difference can be as high as >14% between high line and low line. Starting from our  $2^{nd}$  generation, a propagation delay compensation network is implemented so that the power difference is greatly reduced to best around 2%. A measured result for a 15W demo boards shows an output power difference of around +/-3.8% between 85Vac and 269 Vac input. Figure 11 shows the propagation delay compensation curve implemented to the IC. This function applies to discontinuous conduction mode flyback converter only.

Figure 11 Propagation delay compensation curve

#### 6.6 **Protection Features**

The IC provides several protection features which lead to the Auto Restart Mode or Latched off mode. The following table shows the conditions of the system failure and the associate protection mode.

| Protection functions                                 | Failure condition                                                                  | Protection Mode |

|------------------------------------------------------|------------------------------------------------------------------------------------|-----------------|

| V <sub>CC</sub> Over voltage                         | $V_{CC}$ > 24V and $V_{FB}$ > 4.5V                                                 | Latched off     |

| Over temperature<br>( controller )                   | T <sub>J</sub> > 130 <sup>o</sup> C                                                | Latched off     |

| Short Winding/<br>Short Diode                        | V <sub>CS</sub> >1.66V                                                             | Latched off     |

| BL pin < 0.1V ( BL is external latch enable pin )    | V <sub>BL</sub> <0.1V                                                              | Latched off     |

| Output Overload /<br>Output Short Circuit            | $V_{FB}$ > 4.5V and $V_{BL}$ > 4.0V<br>( after built-in / extended blanking time ) | Auto Restart    |

| Open Loop                                            | -> Output Over Load                                                                | Auto Restart    |

| V <sub>cc</sub> Undervoltage / short<br>Opto-coupler | V <sub>CC</sub> < 10.5V                                                            | Auto Restart    |

#### 6.6.1 Auto Restart Mode

There is always a startup phase with switching cycles in the Auto Restart Mode. After this startup phase the conditions are checked whether the failure is still present. Normal operation proceeds once the failure mode is removed. Otherwise, new startup phase will be initiated again.

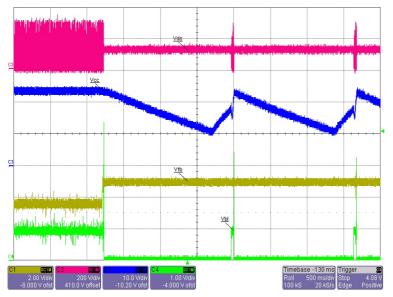

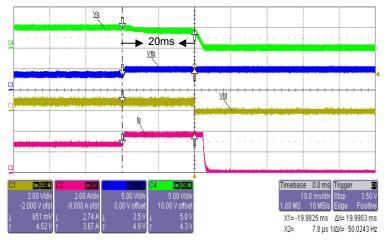

Figure 12 shows the switching waveform of the V<sub>CC</sub> and the feedback voltage V<sub>FB</sub> when the output is shorted to ground. The IC is turned on at V<sub>CC</sub> = 18V. After going through the startup phase, IC is off again due to the fault still exists. V<sub>CC</sub> is discharged until 10.5V. Then, the Startup Cell is activated again to charge up capacitor at V<sub>CC</sub> that initiates another restart cycle.

Figure 12 Auto Restart Mode ( without extended blanking time )

#### 6.6.2 Latched Off Mode

In case of Latched Off Mode, there is no new startup phase any more. Once Latched Off Mode is entered, the internal Voltage Reference is switched off in order to reduce the current consumption of the IC. In this stage only the UVLO is working which switches on/off the startup cell at  $V_{CCoff}/V_{CCon}$ . Latched Off Mode can only be reset when AC line input is plugged out and  $V_{CC}$  is discharged to be lower than 6.23V.

Figure 13 Latch off Mode ( $V_{BL} < 0.1V$ )

Application Note

#### 6.6.3 Blanking Time for over load protection

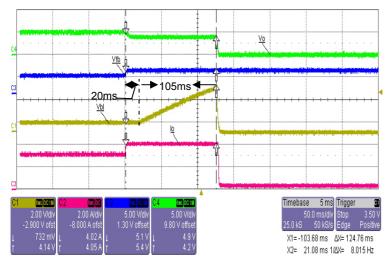

The IC controller provides a blanking window before entering into the auto restart mode due to output overload/short circuit. The purpose is to ensure that the system will not enter protection mode unintentionally. There are 2 kinds of the blanking time; basic and the extendable. The basic one is a built-in feature which is set at 20ms. The extendable one is to extend the basic one with a user defined additional blanking time. The extendable blanking time can be achieved by adding a capacitor,  $C_{BK}$  to the BL pin. When there is over load occurred ( $V_{FB} > 4.5V$ ), the  $C_{BK}$  capacitor will be charged up by an constant current source,  $I_{BK}$  (8.4uA) from 0.9V to 4.0V. Then the auto restart protection will be activated. The charging time from 0.9V to 4.0V to the  $C_{BK}$  capacitor is the extended blanking time. The total blanking time is the addition of the basic and the extended blanking time.

$$T_{blanking} = Basic + Extended = 20ms + \frac{(4.0 - 0.9) * C_{BK}}{I_{BK}} = 20ms + 369047.6 * C_{BK}$$

5)

The measured total blanking time showing in figure 14 is 125ms using  $C_{BK}$ =0.22uF.

In case of output overload or short circuit, the transferred power during the blanking period is limited to the maximum power defined by the value of the sense resistor  $R_{sense}$ .

Figure 14 blanking window for output over load protection (basic blanking time)

Figure 15 blanking window for output overload protection ( with extended blanking time,  $C_{\rm BK}{=}0.22uF$  )

## 7 Layout Recommendation

In order to get the optimized performance of the  $CoolSET^{TM}$ , the grounding of the PCB layout must be connected carefully. From the circuit diagram in figure 7, it indicates that the grounding for the  $CoolSET^{TM}$  can be split into several groups; signal ground, Vcc ground, Current sense resistor ground and EMI return ground. All the split grounds should be "star" connected to the bulk capacitor ground directly. The split grounds are described as below.

- Signal ground includes all small signal grounds connecting to the CoolSET<sup>™</sup> GND pin such as filter capacitor ground, C6, C7, C8 and opto-coupler ground.

- Vcc ground includes the Vcc capctior ground, C5 and the auxiliary winding ground, pin 2 of the power transformer.

- Current Sense resistor ground includes current sense resistor R4 and R4A.

- EMI return ground includes Y capacitor, C4.

## 8 CoolSET<sup>™</sup> F3 Latch & Jitter version Table

| Device      | Package  | V <sub>DS</sub> | Current /A | $R_{dson} / \Omega^1$ | Frequency /<br>KHz | Pout @<br>230Vac±15% <sup>2</sup> | Pout @ 85-265Vac <sup>2</sup> |

|-------------|----------|-----------------|------------|-----------------------|--------------------|-----------------------------------|-------------------------------|

| ICE3A1065LJ | PG-DIP-8 | 650V            | 1.0        | 2.95                  | 100                | 32W                               | 16W                           |

#### 9 References

- [1] Infineon Technologies, Datasheet "CoolSET™-F3 ICE3A1065LJ Off-Line SMPS Current Mode Controller with Integrated 650V Startup Cell / CoolMOS™ (Latched and Frequency Jitter Mode )"

- [2] Eric Kok Siu Kam, Jeoh Meng Kiat, Infineon Technologies, Application Note "AN-EVALSF3-ICE3A1065LJ, 15W 5.0V SMPS Evaluation Board with CoolSET<sup>™</sup> F3 ICE3A1065LJ "

- [3] Harald Zoellinger, Rainer Kling, Infineon Technologies, Application Note "AN-SMPS-ICE2xXXX-1, CoolSET<sup>™</sup> ICE2xXXXX for Off-Line Switching Mode Power supply (SMPS)"

<sup>&</sup>lt;sup>1</sup> Typ @ 25°C

<sup>&</sup>lt;sup>2</sup> Calculated maximum input power rating at  $T_a=75^{\circ}C$ ,  $T_j=125^{\circ}C$  and without copper area as heat sink.