## **EiceDRIVER™** gate driver 1EDI3038AS

## Single channel isolated SiC-MOSFET driver

## **Features**

- Galvanic isolated SiC-MOSFET driver using coreless transformer technology

- Single channel driver for SiC-MOSFETs up to 1200 V

- Low propagation delay 60 ns typically

- Split outputs TON and TOFF for independent turn-on and turn-off slew rates

- Integrated booster with up to 15 A peak current rail-to-rail output

- Integrated active Miller clamp supports unipolar switching

- Configurable external soft turn-off functionality

- CMTI up to 150 V/ns up to ±1200 V

- Reinforced insulation 8 kV peak according to DIN EN IEC 60747-17 (VDE 0884-17):2021-10

- 5.7 kV rms insulation according to UL 1577

- Secondary side active short circuit (SASC) pin

- Integrated safety features up to ASIL B:

- Safety pins on primary side and secondary ASC

- Super fast DESAT including BIST

- Gate monitoring and output stage monitoring

- Shoot-through protection with integrated timeout

- Primary supply monitoring UVLO

- Secondary supply monitoring VCC2 for OVLO and UVLO, VEE2 for UVLO only

- DATA interface for detailed error diagnosis via PWM signal

- 3.3 V and 5 V compatible I/O logic supply

- ISO 26262 Safety Element out of Context for safety requirements up to ASIL B

- Green Product (RoHS compliant)

## **Potential applications**

- Traction inverters for HEV and EV

- Auxiliary inverters for HEV and EV

- High power and fail save on-board chargers for HEV and EV

- High power and fail save DC/DC converters

## **Product validation**

Qualified for automotive applications. Product validation according to AEC-Q100.

**Description**

## **Description**

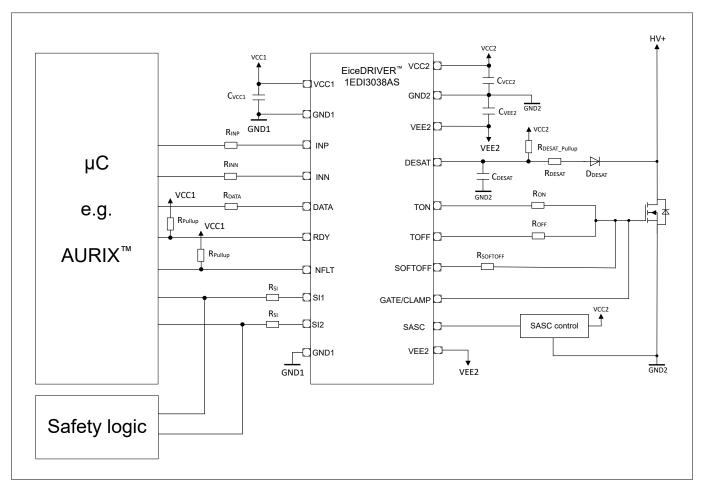

The EiceDRIVER™ gate driver 1EDI3038AS is a high voltage galvanic isolated SiC-MOSFET driver designed for high voltage automotive applications. The device is based on Infineon's coreless transformer (CT) technology providing 8 kV galvanic insulation between low voltage and high voltage domains.

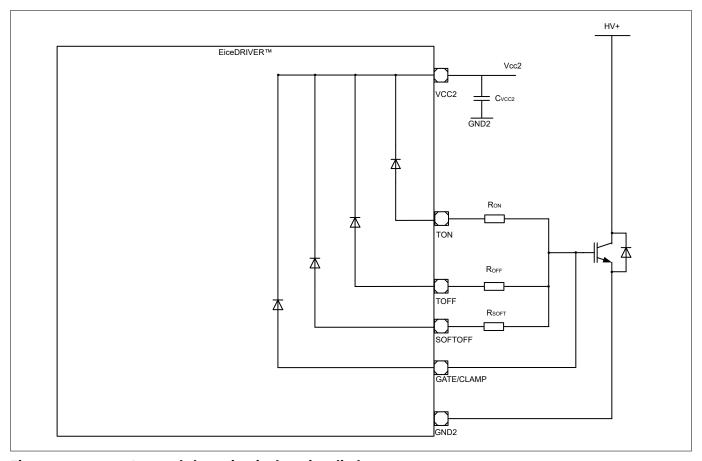

The IC supports up to 1200 V SiC-MOSFETs. The device features a powerful output stage of up to 15 A peak current required for high power switches. A split output stage (TON, TOFF) allows different slew rates for switching on and switching off due to separate gate resistors.

The low voltage domain (primary side) supports logic levels of 5 V as well as 3.3 V. At the high voltage domain (secondary side) it can drive the gate of SiC-MOSFETs directly. A short propagation delay of only 60 ns and a minimum pulse width of 150 ns offer high a switching frequency with minimum distortion of the PWM signal.

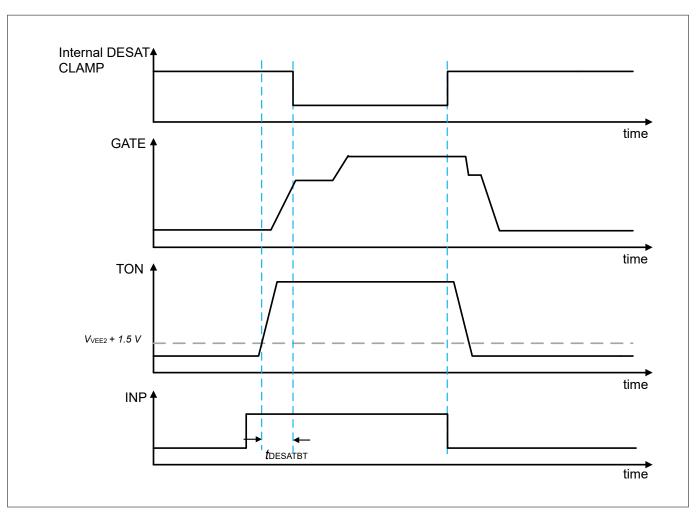

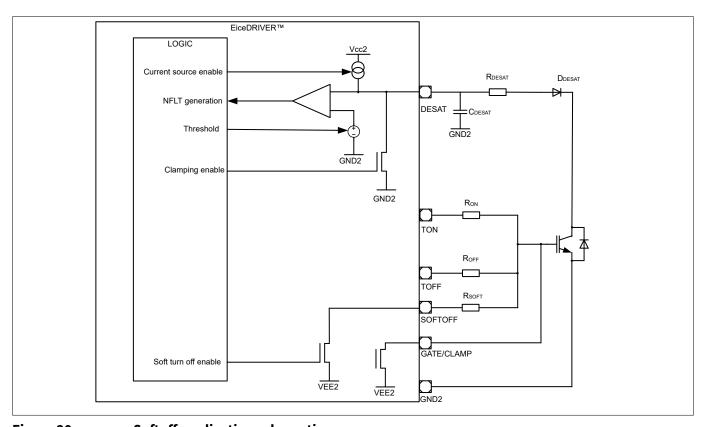

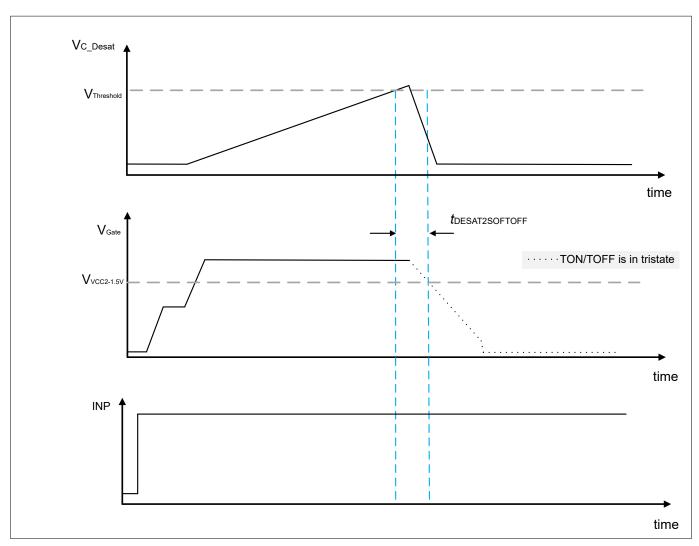

The DESAT protection together with the configurable external soft turn-off feature prevents SiC-MOSFETs destruction in short-circuit events.

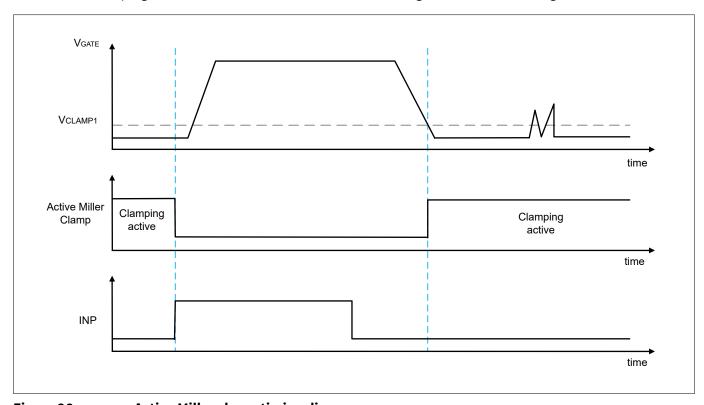

The integrated active Miller clamping stage up to 10 A allows unipolar supply of the SiC-MOSFET.

The device features a DATA interface that provides detailed error diagnosis through a PWM signal.

A large panel of integrated safety related features simplifies the design of ASIL D compliant systems. Safety inputs (SI1, SI2) at the primary side control the transition of the system to safe state. Additionally, the device offers a secondary side active short circuit (ASC) pin to trigger safe state also from the secondary side.

| Туре       | Package   | Marking    |  |

|------------|-----------|------------|--|

| 1EDI3038AS | PG-DSO-20 | 1EDI3038AS |  |

## **Table of contents**

## **Table of contents**

|       | Features                                                    | 1  |

|-------|-------------------------------------------------------------|----|

|       | Potential applications                                      | 1  |

|       | Product validation                                          | 1  |

|       | Description                                                 | 2  |

|       | Table of contents                                           | 3  |

| 1     | Block diagram                                               | 6  |

| 2     | Pin configuration                                           | 7  |

| 2.1   | Pin definitions and functions                               |    |

| 3     | General product characteristics                             | 9  |

| 3.1   | Absolute maximum ratings                                    |    |

| 3.2   | Functional range                                            | 11 |

| 3.3   | Thermal characteristics                                     | 12 |

| 3.4   | Insulation characteristics                                  | 13 |

| 4     | Operating modes and error reactions                         | 15 |

| 4.1   | Operating modes diagram                                     | 15 |

| 4.2   | Operating modes description                                 | 16 |

| 4.3   | Error classification                                        | 16 |

| 4.4   | Single failure events in PWM Enable mode and ASCP_ON mode   | 17 |

| 5     | Primary Side safety control                                 | 18 |

| 5.1   | Functional description of state transitions                 | 19 |

| 5.2   | Functional description of safety related timings            | 20 |

| 5.3   | Electrical characteristics primary side safety control      | 22 |

| 6     | Clear functionality                                         | 23 |

| 6.1   | Functional description clear                                | 23 |

| 6.2   | Electrical characteristics Clear                            | 24 |

| 7     | Power supply current consumption                            | 25 |

| 7.1   | Functional description power supply current consumption     | 25 |

| 7.2   | Electrical characteristics power supply current consumption | 26 |

| 8     | Power supply monitoring                                     | 27 |

| 8.1   | Functional description power supply monitoring              |    |

| 8.1.1 | Functional description at VCC1                              | 27 |

| 8.1.2 | Functional description at VCC2                              | 28 |

| 8.1.3 | Functional description at VEE2                              | 31 |

| 8.2   | Electrical characteristics power supply monitoring          | 33 |

| 9     | Switching characteristics                                   | 35 |

| 9.1   | Electrical characteristics switching                        | 35 |

## **Table of contents**

| 10                | I/O levels                                         | 37 |

|-------------------|----------------------------------------------------|----|

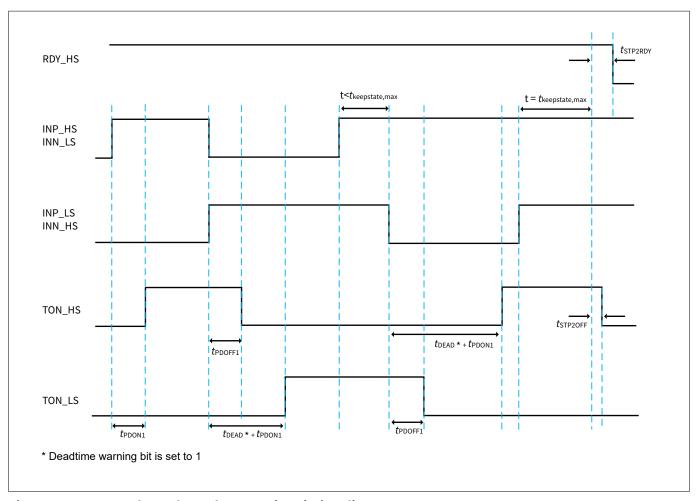

| 11                | Shoot Through Protection (STP)                     | 38 |

| 11.1              | Functional description STP                         | 38 |

| 11.2              | Electrical characteristics STP                     | 39 |

| 12                | Secondary Side input                               | 41 |

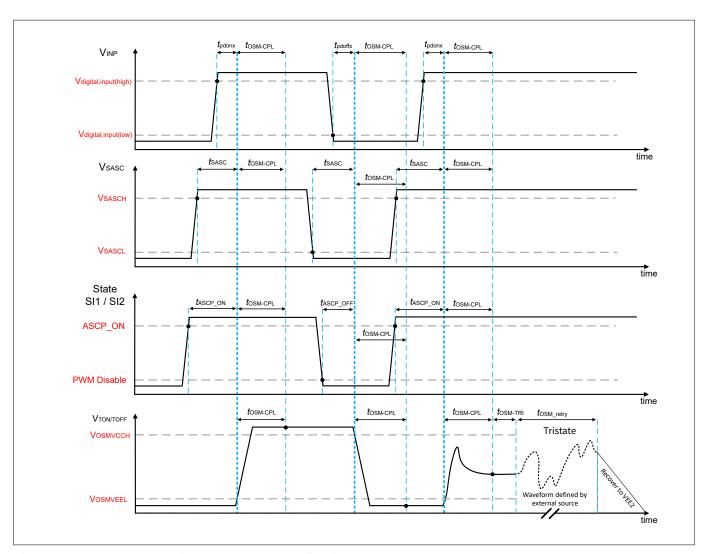

| 12.1              | Secondary Active Short Circuit (SASC)              | 41 |

| 12.1.1            | Functional description SASC                        | 41 |

| 12.1.2            | Electrical characteristics SASC                    | 41 |

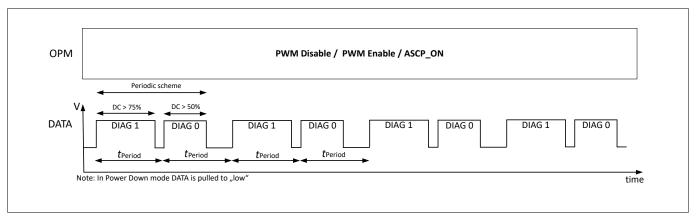

| 13                | DATA readout                                       | 43 |

| 13.1              | Functional description DATA                        | 43 |

| 13.2              | Electrical characteristics DATA                    | 45 |

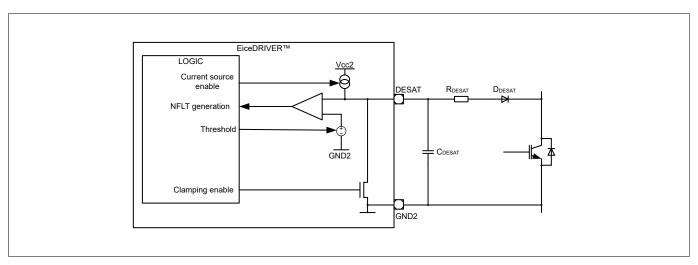

| 14                | DESAT protection                                   | 46 |

| 14.1              | Functional description DESAT protection            | 46 |

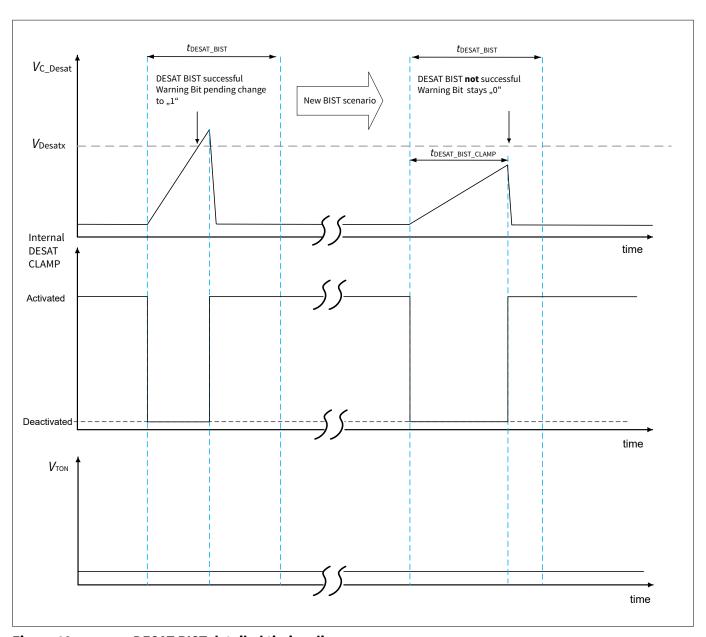

| 14.2              | Functional description DESAT BIST                  | 47 |

| 14.3              | Electrical characteristics DESAT protection        | 48 |

| 15                | Soft turn off                                      | 50 |

| 15.1              | Functional description soft turn off               | 50 |

| 15.2              | Electrical characteristics soft turn off           | 51 |

| 16                | Gate monitoring                                    | 53 |

| 16.1              | Electrical characteristics gate monitoring         | 54 |

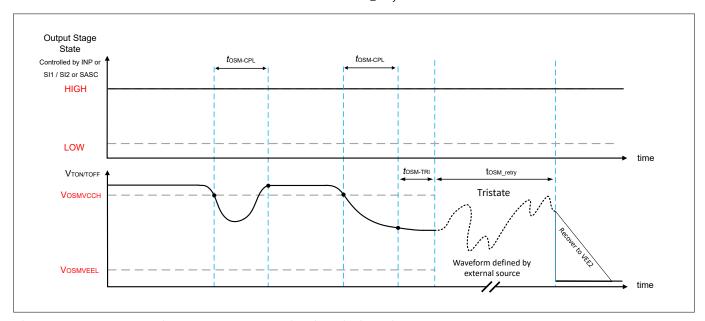

| 17                | Output stage monitoring                            | 56 |

| 17.1              | Electrical characteristics output stage monitoring |    |

| 18                | Active Miller clamp                                | 59 |

| 18.1              | Electrical characteristics Active Miller clamp     |    |

| 19                | Passive clamping                                   | 61 |

| 19.1              | Electrical characteristics passive clamping        |    |

| 20                | Short circuit clamping                             |    |

| 20.1              | Electrical characteristics short circuit clamping  |    |

|                   | Ready (RDY)                                        |    |

| <b>21</b><br>21.1 | Electrical characteristics RDY                     |    |

|                   |                                                    |    |

| 22                | Fault (NFLT)                                       |    |

| 22.1              | Functional description NFLT                        |    |

| 22.2              | Electrical characteristics NFLT                    | 64 |

| 23                | Application information                            |    |

| 23.1              | Typical application example                        | 67 |

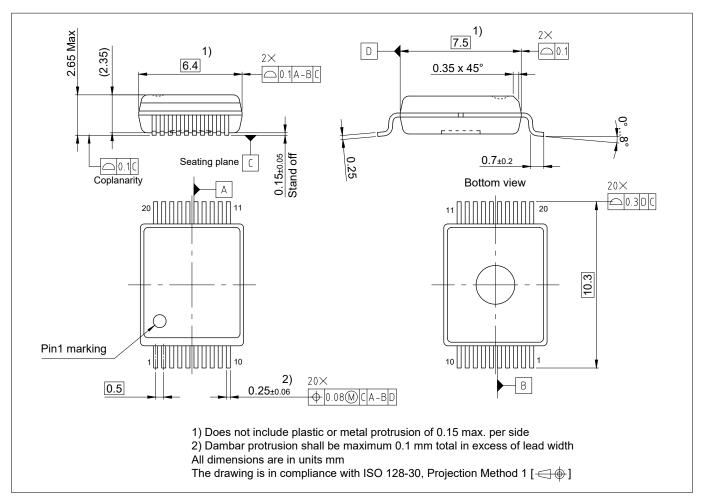

| 24                | Package information                                | 68 |

| 25                | Revision history                                   | 69 |

## **Table of contents**

| <b>Disclaimer</b> |

|-------------------|

|                   |

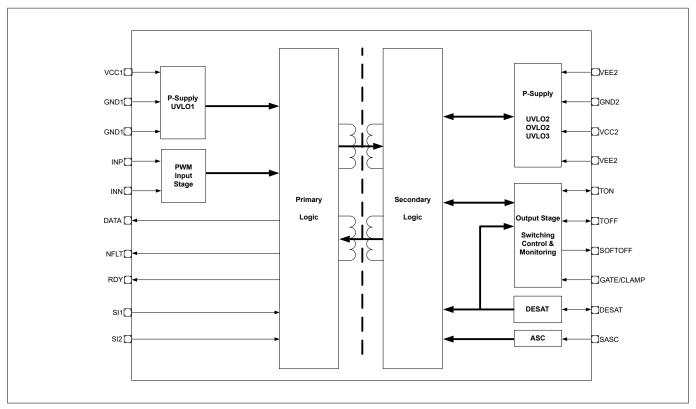

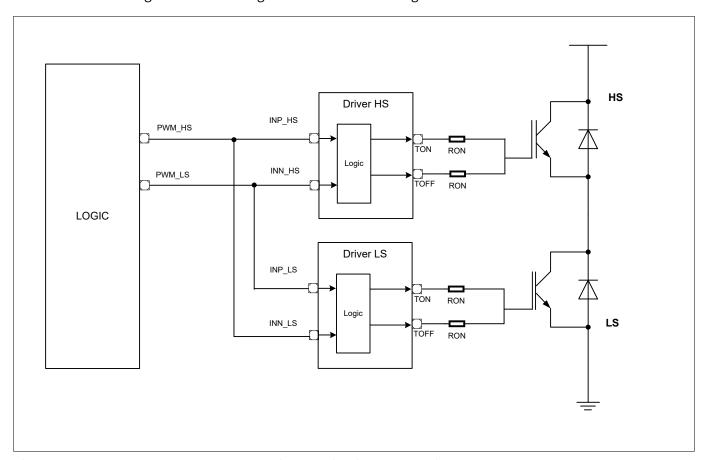

## 1 Block diagram

## 1 Block diagram

Figure 1 Block diagram

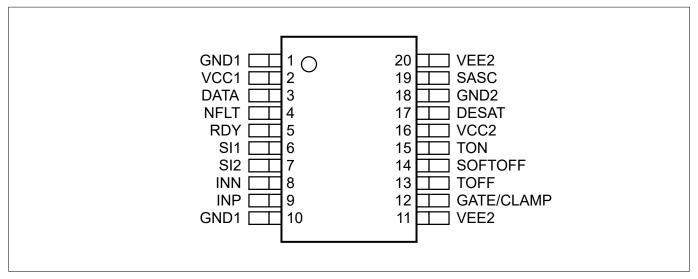

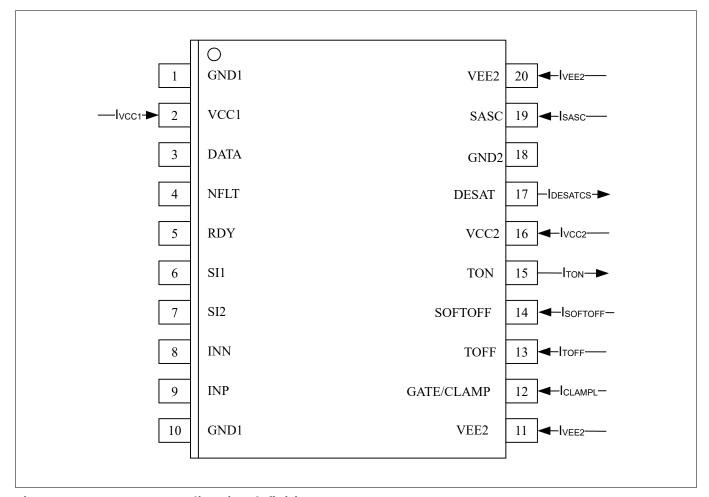

## 2 Pin configuration

## 2 Pin configuration

Figure 2 Pin assignment

## 2.1 Pin definitions and functions

#### Table 1 Pin definitions and functions

| Pin<br># | Pin<br>name | I/O<br>configuratio<br>n       | Voltage<br>class | Function                                                                                                                                                                                                                            |

|----------|-------------|--------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | GND1        | Ground                         | Primary ground   | Ground connection of the primary side.                                                                                                                                                                                              |

| 2        | VCC1        | Supply                         | Primary supply   | 5 V/3.3 V power supply for the primary side referred to GND1.                                                                                                                                                                       |

| 3        | DATA        | Push-pull<br>Output            | VCC1             | Provides a PWM signal to show diagnosis data.                                                                                                                                                                                       |

| 4        | NFLT        | Open Drain<br>Output           | VCC1             | Reports failure events triggered by DESAT protection. As a result the pin is driven to low. Has to be connected to VCC1 with an external pull-up resistance.                                                                        |

| 5        | RDY         | Open Drain<br>Output           | VCC1             | Reports voltage failure events on UVLO1, UVLO2, OVLO2, UVLO3, Life Sign Lost, Output Stage Error and Gate Monitoring Error. As a result this pin is driven to low. Has to be connected to VCC1 with an external pull-up resistance. |

| 6        | SI1         | Input<br>internal Pull<br>down | VCC1             | Safety input to control the output stage via the primary side to achieve a system safe state. Shall be connected to the corresponding SI2 input of the opposing gate driver inside a halfbridge topology.                           |

| 7        | SI2         | Input<br>internal Pull<br>down | VCC1             | Safety input to control the output stage via the primary side to achieve a system safe state. Connect to the corresponding SI1 input of the opposing gate driver inside a halfbridge topology.                                      |

## 2 Pin configuration

## Table 1 (continued) Pin definitions and functions

| Pin<br># | Pin<br>name    | I/O<br>configuratio<br>n                           | Voltage<br>class    | Function                                                                                                                                                                                                         |

|----------|----------------|----------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8        | INN            | Input<br>Internal Pull<br>up                       | VCC1                | The inverting PWM signal is used for monitoring the shoot through protection inside a halfbridge topology. Connect to INP of the opposing gate driver inside a halfbridge topology. If not used connect to GND1. |

| 9        | INP            | Input<br>Internal Pull<br>down                     | VCC1                | The non-inverting PWM signal of the driver to drive the secondary side output stage voltage.                                                                                                                     |

| 10       | GND1           | Ground                                             | Primary ground      | Ground connection of the primary side.                                                                                                                                                                           |

| 11       | VEE2           | Supply                                             | Secondary<br>supply | Negative power supply for the secondary side referred to GND2.<br>Connect to GND2 for unipolar operation.                                                                                                        |

| 12       | GATE/<br>CLAMP | Input                                              | VCC2                | Monitors the gate of the power switch and clamps the gate to VEE2 if the threshold $V_{\text{CLAMP}}$ is reached.                                                                                                |

| 13       | TOFF           | Input/Output                                       | VEE2                | Switches the power switch gate to VEE2 according to the PWM low input on INP.                                                                                                                                    |

| 14       | SOFTO<br>FF    | Output                                             | VEE2                | The SOFTOFF is activated in case a DESAT or gate monitoring error is present. Clamps the voltage to VEE2.                                                                                                        |

| 15       | TON            | Input/Output                                       | VCC2                | Switches the power switch gate to VCC2 according to the PWM high input on INP.                                                                                                                                   |

| 16       | VCC2           | Secondary<br>supply                                | VCC2                | Positive power supply for the secondary side referred to GND2.                                                                                                                                                   |

| 17       | DESAT          | Input VCC2 Internal Pull up through current source |                     | Monitors the voltage across the power switch during output "high" signal.                                                                                                                                        |

| 18       | GND2           | Ground                                             | Secondary ground    | Ground connection for the secondary side.                                                                                                                                                                        |

| 19       | SASC           | Input                                              | VCC2                | The active short circuit function controls the output voltage of TON to VCC2.                                                                                                                                    |

| 20       | VEE2           | Supply                                             | Secondary supply    | Negative power supply for the secondary side referred to GND2.<br>Connect to GND2 for unipolar operation.                                                                                                        |

#### 3 General product characteristics

## **3** General product characteristics

## 3.1 Absolute maximum ratings

#### Table 2 Absolute maximum ratings

$T_J$  = -40°C to 150°C; all voltages with respect to ground, pos. current flowing into pin (unless otherwise specified). Absolute maximum ratings are defined as ratings which when being exceeded may lead to destruction of the integrated circuit. Absolute maximum ratings are not subject to production test, specified by design.

| Parameter                                                                                       | Symbol                          | Values                  |      |                         | Unit | Note or condition  | P-      |

|-------------------------------------------------------------------------------------------------|---------------------------------|-------------------------|------|-------------------------|------|--------------------|---------|

|                                                                                                 |                                 | Min.                    | Тур. | Max.                    |      |                    | Number  |

| Positive power supply (primary)                                                                 | V <sub>VCC1_MAX</sub>           | -0.3                    | -    | 7                       | V    | Referenced to GND1 | PRQ-42  |

| Positive<br>power supply<br>(secondary)                                                         | V <sub>VCC2_MAX</sub>           | -0.3                    | _    | 30                      | V    | Referenced to GND2 | PRQ-43  |

| Negative<br>power supply<br>(secondary)                                                         | V <sub>VEE2_MAX</sub>           | -13                     | _    | 0.3                     | V    | Referenced to GND2 | PRQ-44  |

| Power supply<br>voltage<br>difference<br>(secondary)<br>VCC2-VEE2                               | V <sub>VCC2</sub> -<br>VEE2_MAX | -                       | -    | 40                      | V    |                    | PRQ-45  |

| Voltages on<br>any I/O pin<br>on primary<br>side (INP,<br>INN, SI1, SI2,<br>DATA, NFLT,<br>RDY) | V <sub>INX_MAX</sub>            | -0.3                    | -    | V <sub>VCC1</sub> + 0.3 | V    | Referenced to GND1 | PRQ-46  |

| SASC voltage                                                                                    | V <sub>SASC_MAX</sub>           | -0.3                    | -    | V <sub>CC2</sub> +0.3   | V    | Referenced to GND2 | PRQ-714 |

| DESAT<br>voltage                                                                                | V <sub>DESAT_MAX</sub>          | -0.3                    | -    | V <sub>VCC2</sub> + 0.3 | V    | Referenced to GND2 | PRQ-49  |

| Maximum<br>GATE/CLAMP<br>voltage                                                                | V <sub>GATE/</sub> CLAMP_MAX    | V <sub>VEE2</sub> - 0.3 | _    | V <sub>VCC2</sub> + 0.3 | V    | Referenced to GND2 | PRQ-52  |

| SOFTOFF<br>voltage                                                                              | V <sub>SOFTOFF_M</sub>          | V <sub>VEE2</sub> - 0.3 | -    | V <sub>VCC2</sub> + 0.3 |      | Referenced to GND2 | PRQ-603 |

| TON voltage                                                                                     | V <sub>OUT_MAX</sub>            | V <sub>VEE2</sub> - 0.3 | _    | V <sub>VCC2</sub> + 0.3 | V    | Referenced to GND2 | PRQ-53  |

#### 3 General product characteristics

#### Table 2 (continued) Absolute maximum ratings

$T_{\rm J}$  = -40°C to 150°C; all voltages with respect to ground, pos. current flowing into pin (unless otherwise specified). Absolute maximum ratings are defined as ratings which when being exceeded may lead to destruction of the integrated circuit. Absolute maximum ratings are not subject to production test, specified by design.

| Parameter                                                                | Symbol                          | Values                  |      |                         | Unit | Note or condition                                                                                                                      | P-      |

|--------------------------------------------------------------------------|---------------------------------|-------------------------|------|-------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------|---------|

|                                                                          |                                 | Min.                    | Тур. | Max.                    |      |                                                                                                                                        | Number  |

| TOFF voltage                                                             | V <sub>OFF_MAX</sub>            | V <sub>VEE2</sub> - 0.3 |      | V <sub>VCC2</sub> + 0.3 | V    | Referenced to GND2                                                                                                                     | PRQ-602 |

| TON high<br>maximum<br>current                                           | I <sub>OUTH_MAX</sub>           | -15                     | -    | _                       | A    | $t_{\rm MAX}$ = 500 ns, non-repetitive                                                                                                 | PRQ-701 |

| TOFF low<br>maximum<br>current                                           | I <sub>OUTL_MAX</sub>           | _                       | -    | 15                      | А    | $t_{\rm MAX}$ = 500 ns, non-repetitive                                                                                                 | PRQ-55  |

| GATE/CLAMP<br>low<br>maximum<br>current                                  | I <sub>Gate/</sub><br>Clamp_Max | -                       | _    | 10                      | A    | t <sub>MAX</sub> =500 ns, non-repetitive                                                                                               | PRQ-56  |

| Short circuit clamping maximum current on GATE/CLAMP, SOFTOFF, TON, TOFF | I <sub>SC_MAX</sub>             | -                       | -    | 2                       | A    | $t_{\rm MAX}$ =3 $\mu$ s, 20 repetitions, 100ms between repetitions                                                                    | PRQ-727 |

| Maximum<br>DESAT<br>negative<br>transient<br>current                     | I <sub>DESATNTC</sub>           | -50                     | -    | -                       | mA   | $t_{\rm DESATNTC}$ = 500 ns, $f_{\rm s,max}$ = 60 kHz                                                                                  | PRQ-733 |

| Current on<br>output logic<br>pins (DATA,<br>RDY, NFLT)                  | / <sub>OUTx_MAX</sub>           | -                       | _    | 10                      | mA   |                                                                                                                                        |         |

| HBM<br>robustness,<br>all pins                                           | V <sub>ESD_HBM1</sub>           |                         | _    | 2                       | kV   | Human Body Model "HBM" robustness according to AEC-Q100-002                                                                            | PRQ-669 |

| CDM<br>robustness,<br>all pins                                           | V <sub>ESD_CDM1</sub>           |                         | _    | 500                     | тс   | Charged Device Model "CDM" robustness according to AEC-Q100-011 Rev D. "TC" corresponds to "Test Condition" according to AEC-Q100-011. | PRQ-58  |

#### 3 General product characteristics

#### Table 2 (continued) Absolute maximum ratings

$T_J$  = -40°C to 150°C; all voltages with respect to ground, pos. current flowing into pin (unless otherwise specified). Absolute maximum ratings are defined as ratings which when being exceeded may lead to destruction of the integrated circuit. Absolute maximum ratings are not subject to production test, specified by design.

| Parameter                                         | Symbol                           | Values |      |      | Unit No | Note or condition                                                                                                                      | P-      |

|---------------------------------------------------|----------------------------------|--------|------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------|---------|

|                                                   |                                  | Min.   | Тур. | Мах. |         |                                                                                                                                        | Number  |

| CDM<br>robustness,<br>corner pins<br>(GND1, VEE2) | V <sub>ESD_CDM2</sub>            |        | _    | 750  | TC      | Charged Device Model "CDM" robustness according to AEC-Q100-011 Rev D. "TC" corresponds to "Test Condition" according to AEC-Q100-011. | PRQ-668 |

| Storage temperature                               | T <sub>s_MAX</sub>               | -55    | -    | 150  | °C      |                                                                                                                                        | PRQ-59  |

| Junction temperature                              | $T_{J\_MAX}$                     | -40    | -    | 150  | °C      |                                                                                                                                        | PRQ-60  |

| SOFTOFF low<br>maximum<br>sink current            | I <sub>SOFTOFF_lo</sub><br>w_Max | _      | -    | 3    | А       | $t_{\rm MAX}$ = 100 ns, non-repetitive                                                                                                 | PRQ-730 |

## 3.2 Functional range

#### Table 3 Functional range

$T_J$  = -40°C to 150°C; all voltages with respect to ground, pos. current flowing into pin (unless otherwise specified).

| Parameter                             | Symbol            | Values |      |      | Unit | Note or condition                | P-      |

|---------------------------------------|-------------------|--------|------|------|------|----------------------------------|---------|

|                                       |                   | Min.   | Тур. | Max. |      |                                  | Number  |

| Primary power supply                  | V <sub>VCC1</sub> | 3      | -    | 5.5  | V    | Referenced to GND1 <sup>1)</sup> | PRQ-61  |

| VCC1 ramp-<br>up rate                 | $t_{RP1}$         | -      | -    | 200  | V/ms |                                  | PRQ-62  |

| Secondary<br>Positive<br>power supply | V <sub>VCC2</sub> | 13.5   | 15   | 20   | V    | Referenced to GND2 <sup>2)</sup> | PRQ-64  |

| VCC2 ramp-<br>up slew rate            | t <sub>RP2</sub>  | -      | -    | 100  | V/ms |                                  | PRQ-65  |

| Negative<br>power supply              | V <sub>VEE2</sub> | -6     | -5   | 0    | V    | Referenced to GND2 <sup>3)</sup> | PRQ-573 |

| VEE2 ramp<br>up slew rate             | t <sub>RP3</sub>  | -100   | -    | -    | V/ms |                                  | PRQ-67  |

#### 3 General product characteristics

#### Table 3 (continued) Functional range

$T_J = -40$ °C to 150°C; all voltages with respect to ground, pos. current flowing into pin (unless otherwise specified).

| Parameter                                                                                       | Symbol                 | Values |      |                   | Unit  | Note or condition            | P-     |

|-------------------------------------------------------------------------------------------------|------------------------|--------|------|-------------------|-------|------------------------------|--------|

|                                                                                                 |                        | Min.   | Тур. | Max.              |       |                              | Number |

| Secondary<br>Power supply<br>voltage<br>difference<br>VCC2-VEE2                                 | V <sub>VCC2-VEE2</sub> | -      | -    | 25                | V     |                              | PRQ-68 |

| Junction<br>temperature                                                                         | TJ                     | -40    | -    | 150               | °C    |                              | PRQ-69 |

| Common<br>mode<br>transient<br>immunity                                                         | dV <sub>ISO</sub> /dt  | -150   | _    | 150               | kV/µs | For voltages up to +/-1200 V | PRQ-70 |

| Voltages on<br>any I/O pin<br>on primary<br>side (INP,<br>INN, SI1, SI2,<br>DATA, RDY,<br>NFLT) | V <sub>INx</sub>       | 0      | -    | V <sub>VCC1</sub> | V     | Referenced to GND1           | PRQ-71 |

- 1) For  $V_{\text{VCC1}}$  crossing  $V_{\text{UVLO1L}\_1}$  the UVLO1 reaction is performed.

- 2) For  $V_{\text{VCC2}}$  crossing  $V_{\text{OVLO2L}_{-x}}$  or  $V_{\text{UVLO2L}_{-x}}$  the OVLO2 or UVLO2 reaction is performed respectively.

- For  $V_{\text{VEE2}}$  crossing  $V_{\text{UVLO3L}}$  x the UVLO3 reaction is performed respectively.

#### Note:

Within the functional range the IC operates as described in the circuit descriptions. Continuous switching operation of the output stage is possible. Electrical characteristics stated within the following sections are specified within the conditions given in the electrical characteristics table. The reaction to undervoltage and overvoltage protection is only performed when exiting the functional range.

#### 3.3 Thermal characteristics

#### Thermal characteristics Table 4

$T_J$  = -40°C to 150°C; all voltages with respect to ground, pos. current flowing into pin (unless otherwise specified).

| Parameter                                     | Symbol                  | Values |      |      | Unit | Note or condition        | P-     |

|-----------------------------------------------|-------------------------|--------|------|------|------|--------------------------|--------|

|                                               |                         | Min.   | Тур. | Max. |      |                          | Number |

| Thermal Resistance Junction to Ambient (25°C) | R <sub>TH-JA,25°C</sub> | -      | 88   | -    | K/W  | T <sub>amb</sub> = 25 °C | PRQ-78 |

#### 3 General product characteristics

#### Table 4 (continued) Thermal characteristics

$T_J = -40$ °C to 150°C; all voltages with respect to ground, pos. current flowing into pin (unless otherwise specified).

| Parameter                                                      | Symbol                    | Values |      |      | Unit | Note or condition                                             | P-      |

|----------------------------------------------------------------|---------------------------|--------|------|------|------|---------------------------------------------------------------|---------|

|                                                                |                           | Min.   | Тур. | Max. |      |                                                               | Number  |

| Thermal Resistance Junction to Ambient (125°C)                 | R <sub>TH-JA,125°</sub> C | -      | 73   | -    | K/W  | T <sub>amb</sub> = 125 °C                                     | PRQ-79  |

| Thermal<br>Resistance<br>Junction to<br>Case Top               | R <sub>TH-JC-TOP</sub>    | _      | 50   | _    | K/W  | 25 °C ≤ T <sub>amb</sub> ≤ 125 °C                             | PRQ-81  |

| Ψ - Pseudo<br>Thermal<br>Resistance<br>Junction to<br>Case Top | $\Psi_{JC-TOP}$           | -      | 21   | -    | K/W  | 25 °C ≤ T <sub>amb</sub> ≤ 125 °C                             | PRQ-83  |

| Transient Thermal Impedance Junction to Ambient                | Z <sub>TH-JA</sub>        | -      | 50   | -    | K/W  | 25 °C ≤ $T_{\rm amb}$ ≤ 125 °C, Pulse width $t_{\rm p}$ ≤ 4 s | PRQ-738 |

Note:

This thermal data was generated in accordance with JEDEC JESD51 standards. R  $_{ ext{TH-JA}}$  and  $\Psi_{ ext{JC-}}$ TOP are simulated on a 2s4p board (35mm x 50mm x 1.5mm) with 35µm copper thickness and 40% metallization on the inner power planes. The copper is split between the primary and secondary side. The device footprint is a direct fan-out on top layer. Only the corner pins are connected with a single via to an internal copper layer.

#### **Insulation characteristics** 3.4

Table 5 Insulation characteristics for reinforced insulation in compliance with DIN EN IEC 60747-17 (VDE 0884-17):2021-10

| Description                                            | Symbol | Characteristic | Unit |

|--------------------------------------------------------|--------|----------------|------|

| Installation classification per IEC 60664-1, Table F.1 |        |                | -    |

| for rated mains voltage ≤ 150 V <sub>RMS</sub>         |        | I-IV           |      |

| for rated mains voltage ≤ 300 V <sub>RMS</sub>         |        | I-IV           |      |

| for rated mains voltage ≤ 600 V <sub>RMS</sub>         |        | I-III          |      |

| for rated mains voltage ≤ 1000 V <sub>RMS</sub>        |        | I-II           |      |

| Climatic classification                                | -      | 40/125/21      | -    |

| Pollution degree (IEC 60664-1)                         | _      | 2              | _    |

## **3 General product characteristics**

Table 5 (continued) Insulation characteristics for reinforced insulation in compliance with DIN EN IEC 60747-17 (VDE 0884-17):2021-10

| Description                                                                                                                                                                                                                     | Symbol            | Characteristic     | Unit              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------|-------------------|

| Minimum external clearance                                                                                                                                                                                                      | CLR               | > 8                | mm                |

| Minimum external creepage                                                                                                                                                                                                       | CPG               | > 8                | mm                |

| Minimum comparative tracking index                                                                                                                                                                                              | СТІ               | > 400              | _                 |

| Maximum rated repetitive peak isolation voltage                                                                                                                                                                                 | $V_{IORM}$        | 1767               | V <sub>peak</sub> |

| Maximum rated transient isolation voltage                                                                                                                                                                                       | $V_{IOTM}$        | 8000               | V <sub>peak</sub> |

| Maximum impulse voltage, tested in air                                                                                                                                                                                          | $V_{IMP}$         | 8000               | V <sub>peak</sub> |

| Maximum surge isolation voltage for reinforced insulation, tested in oil Test voltage in subgroup #1 = 11 kV $\geq$ 1.3 x $V_{\rm IMP}$ , min. 10 kV                                                                            | V <sub>IOSM</sub> | 11000              | V <sub>peak</sub> |

| Input to output test voltage, method b1) $V_{\text{ini,b}} = 1.2 \text{ x}$ $V_{\text{IOTM}}$ , $V_{\text{pd(m)}} \ge V_{\text{IORM}} \text{ x } 1.875$ , 100% production test, $t_{\text{ini,b}} = t_{\text{m}} = 1 \text{ s}$ | $q_{	ext{PD}}$    | < 5                | pC                |

| Input to output test voltage, method a) $V_{\text{ini,a}} = V_{\text{IOTM}}$ , $V_{\text{pd(m)}} \ge V_{\text{IORM}} \times 1.6$ , sample test, $t_{\text{ini}} = 60 \text{ s}$ , $t_{\text{m}} = 60 \text{ s}$                 | $q_{PD}$          | < 5                | рС                |

| Isolation resistance at 25 °C $\leq$ $T_{amb} \leq$ 125 °C, $V_{io} =$ 500 V                                                                                                                                                    | R <sub>IO</sub>   | > 10 <sup>12</sup> | Ω                 |

| Isolation resistance at $T_S$ = 150°C, $V_{io}$ = 500 V                                                                                                                                                                         | R <sub>IO</sub>   | > 109              | Ω                 |

## Table 6 Insulation characteristics recognized according to UL 1577

| Parameter                            | Symbol           | Characteristic | Unit    |

|--------------------------------------|------------------|----------------|---------|

| Insulation withstand voltage / 1 min | $V_{\rm ISO}$    | 5700           | V (rms) |

| Insulation test voltage / 1 s        | V <sub>ISO</sub> | 6000           | V (rms) |

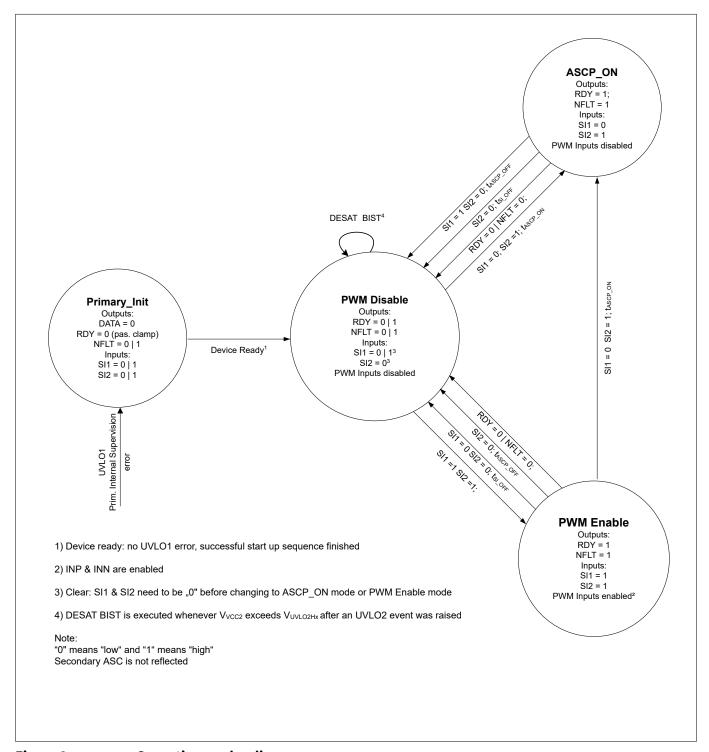

4 Operating modes and error reactions

## 4 Operating modes and error reactions

## 4.1 Operating modes diagram

Figure 3 Operating modes diagram

Note:

- Life sign lost will be detected only if communication has been established once.

- External pull-up required on RDY and NFLT (open drain output).

# infineon

#### 4 Operating modes and error reactions

## 4.2 Operating modes description

The device has the following modes which it can operate in:

- Primary\_Init mode

- PWM Disable mode

- PWM Enable mode

- ASCP ON mode

#### Primary\_Init mode and start up

The device is in Primary\_Init mode at start-up if an primary internal supervision or an UVLO1 error occurs. In both cases it will not operate as the primary die is not ready. DATA is pulled to "low".

#### **PWM Disable mode**

- In PWM Disable mode with NFLT = "high" and RDY = "high" no error occurred.

- In PWM Disable mode with NFLT or RDY = "low" an error occurred.

#### Mode transition to PWM Enable mode

Once in PWM Disable mode the change to PWM Enable mode is done with setting SI1 and SI2 signal to "high". Changing the state of SI2 back to "low" the device is returning into PWM Disable mode.

#### **PWM Enable mode**

In PWM Enable mode the output gate voltage is following the signal transitions on INP in case there is no STP keep error between INP & INN input signals.

#### ASCP\_ON mode

Setting SI1 = "low" and SI2= "high" transitions the device state to ASCP\_ON mode after a defined delay. During this mode the switching state transition via INP signal is disabled. The output stage is in a stable "high" condition. Changing the state of SI2 to "low" shifts the device back to PWM Disable mode with a defined delay. If an error related to NFLT or RDY occurs, the device is shifted to PWM Disable Mode. A state transition from ASCP\_ON mode to PWM Enable mode is prohibited.

#### **Error transitions**

The transition from PWM Enable mode or ASCP\_ON mode to PWM Disable mode is done according error events which are based on a NFLT error or a RDY error.

#### 4.3 Error classification

The following errors are classified as NFLT error:

DESAT event

In this case NFLT is pulled to "low".

The following errors are classified as RDY error:

- Primary supervision error

- UVLO1 event

- UVLO2 event

- OVLO2 event

- UVLO3 event

- Sec. Internal Supervision error

- Output stage monitoring error

- Gate monitoring error

## 4 Operating modes and error reactions

- STP keep error

- Life sign error

In all cases RDY transitions to "low".

## 4.4 Single failure events in PWM Enable mode and ASCP\_ON mode

#### Table 7 Single failure events in PWM Enable and ASCP\_ON mode

| •                                |                                                                    |                                    |                                                                 |                              |

|----------------------------------|--------------------------------------------------------------------|------------------------------------|-----------------------------------------------------------------|------------------------------|

| Failure Event                    | Device in PWM Enable mode Output stage reaction when TON is "high" | Resulting<br>pin status<br>changes | Device in ASCP_ON mode Output stage reaction when TON is "high" | Resulting pin status changes |

| DESAT error when TON = "high"    | Tristate and turn off via SOFTOFF                                  | NFLT = 1 → 0                       | Tristate and turn off via SOFTOFF                               | NFLT = 1 → 0                 |

| Gate monitoring error            | Tristate and turn off via SOFTOFF                                  | RDY = 1 → 0                        | Tristate and turn off via SOFTOFF                               | RDY = 1 → 0                  |

| OSM error                        | Tristate                                                           | RDY = 1 → 0                        | Tristate                                                        | RDY = 1 → 0                  |

| UVL01                            | Normal switch-off                                                  | RDY = 1 → 0                        | Normal switch-off                                               | RDY = 1 → 0                  |

| UVLO2                            | Normal switch-off                                                  | RDY = 1 → 0                        | Normal switch-off                                               | RDY = 1 → 0                  |

| OVLO2                            | Normal switch-off                                                  | RDY = 1 → 0                        | Normal switch-off                                               | RDY = 1 → 0                  |

| UVL03                            | Normal switch-off                                                  | RDY = 1 → 0                        | Normal switch-off                                               | RDY = 1 → 0                  |

| Prim. internal supervision error | Normal switch-off                                                  | RDY = 1 → 0                        | Normal switch-off                                               | RDY = 1 → 0                  |

| Sec. internal supervision error  | Normal switch-off                                                  | RDY = 1 → 0                        | Normal switch-off                                               | RDY = 1 → 0                  |

| Life sign error                  | Normal switch-off                                                  | RDY = 1 → 0                        | Normal switch-off                                               | RDY = 1 → 0                  |

| STP keep error                   | Normal switch-off                                                  | RDY = 1 → 0                        | TON stays "high"                                                | RDY = 1 → 1                  |

Note:

- In case the output stage is off the desaturation detection is disabled

- During an UVLO1 failure event the NFLT pin may also switch to "low"

# infineon

**5 Primary Side safety control**

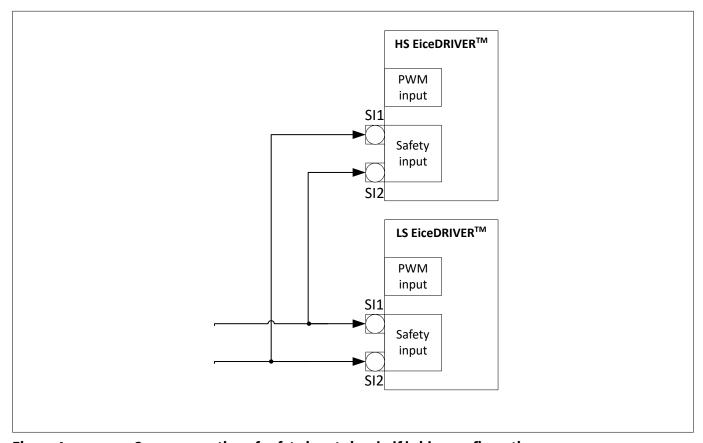

## **5** Primary Side safety control

The device has two dedicated safety inputs on the primary side. The safety inputs control the output stage reaction in the Safety input states table.

Table 8 Safety input states table

| Operation Mode | SI1 | SI2 | Delay                 | TON/TOFF    | Exception                                                                                  |

|----------------|-----|-----|-----------------------|-------------|--------------------------------------------------------------------------------------------|

| PWM Disable    | 0   | 0   | t <sub>SI_OFF</sub>   | Low (VEE2)  | Primary_Init mode                                                                          |

| PWM Disable    | 1   | 0   | t <sub>ASCP_OFF</sub> | Low (VEE2)  | Primary_Init mode                                                                          |

| ASCP_ON Mode   | 0   | 1   | t <sub>ASCP_ON</sub>  | High (VCC2) | Primary_Init mode or events in 'Single failure events in PWM Enable mode and ASCP_ON mode' |

| PWM Enable     | 1   | 1   | -                     | PWM         | Primary_Init mode or events in 'Single failure events in PWM Enable mode and ASCP_ON mode' |

Note:

- "0" means "low"; "1" means "high".

- If an error related to NFLT or RDY appeared during state transition including the internal delay of SI1 and SI2, the device follows the predefined emergency turn off sequence.

The described PWM signal refers to INP/INN signal on primary side input pins.

The safety inputs of the HS and LS driver are cross connected, as follows. In that way, if a primary ASC is triggered, the opposite driver is turning off. Hence a shoot through is avoided.

Figure 4 Cross connection of safety inputs in a half bridge configuration

# **(infineon**

#### **5 Primary Side safety control**

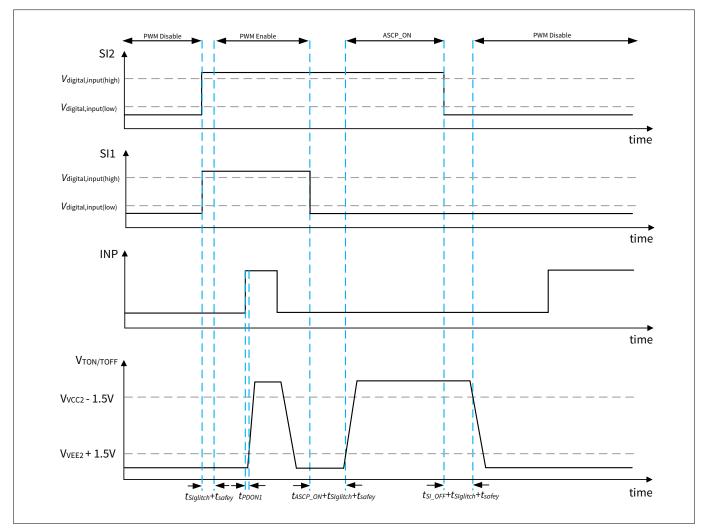

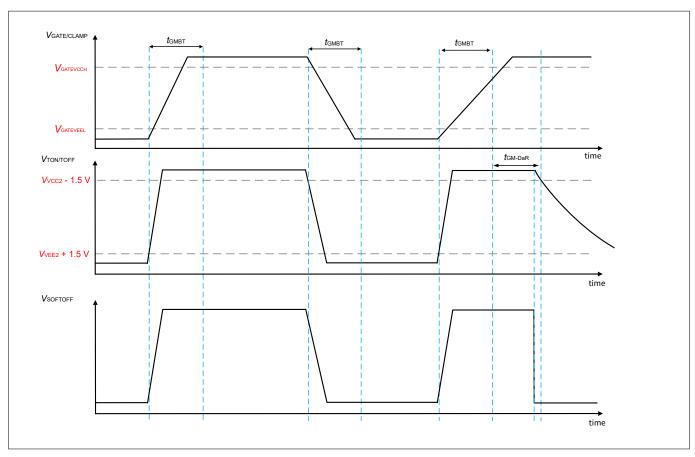

## 5.1 Functional description of state transitions

#### **PWM Disable mode to PWM Disable mode**

The device input triggers to change the operation mode from PWM Disable mode to PWM Disable mode via following state transitions:

- SI2 stays "low" and SI1 = "high".

- SI2 stays "low" and SI1 = "low".

In PWM Disable mode the PWM signal on INP is disabled.

#### PWM Disable mode to PWM Enable mode

The device input triggers to change the operation mode from PWM Disable mode to PWM Enable mode via following state transition:

• SI1 = "low" to "high" and SI2 = "low" to "high" - see further information in the Note and in Tsafety diagram Only during PWM Enable mode the PWM signal on INP is a valid input signal for the output stage.

In case INP is "high" before PWM Enable mode is reached after a delay of  $t_{\text{safety}} + t_{\text{SIglitch}}$ , TOFF stays "low". TON is activated by next rising edge on INP.

#### PWM Enable mode to PWM Disable mode

The device can be triggered from PWM Enable mode to PWM Disable mode via safety inputs with following state transitions:

- SI1 = "low" and SI2 = "low". After  $t_{SI\_OFF}$  delay is elapsed, TON switches ''low''.

- SI1 stays "high" and SI2 = "low". After  $t_{ASCP\ OFF}$  delay is elapsed, TON switches ''low''.

After internal recognition of the transition via the safety inputs the output stage does not follow the INP signal. In case there is a state transition on INP from "high" to "low" or "low" to "high" during  $t_{\rm ASCP\_OFF}$  or  $t_{\rm SI\_OFF}$  this transition is disabled.

#### PWM Disable mode to ASCP\_ON mode

The device can be triggered to change the operation state from PWM Disable mode to ASCP\_ON mode via following transition on SI1 and SI2:

SI1 = "low" and SI2 = "high"

An additional delay is included into this state transition and is defined in  $t_{\rm ASCP\_ON}$ .

In the PWM Disable and ASCP\_ON modes all INP state transitions are ignored.

#### ASCP\_ON mode to PWM Disable mode

The device triggers a state transitions from ASCP\_ON mode to PWM Disable mode via following state transitions on SI1 and SI2:

- SI2 = "low". After  $t_{SI OFF}$  delay is elapsed, TON switches "low".

- SI1 = "high" and SI2 = "low". After  $t_{ASCP\ OFF}$  delay is elapsed, TON switches ''low''.

Inside PWM Disable mode and ASCP\_ON mode the INP input is ignored.

During  $t_{SI OFF}$  and  $t_{ASCP OFF}$  the output stage is "high".

#### PWM Enable mode to ASCP\_ON mode

The device can trigger a state transition from PWM Enable mode to ASCP\_ON mode by setting SI1 to "low".

An additional delay is included and defined in  $t_{\mathsf{ASCP\_ON}}$ .

In case there is a state transition on INP from "high" to "low" or "low" to "high" during  $t_{ASCP\_ON}$  this transition is ignored.

During  $t_{ASCP-ON}$  the last valid INP signal is active on TON/TOFF.

#### 5 Primary Side safety control

Note:

A direct state transition from ASCP\_ON mode to PWM Enable mode is prohibited.

A direct state transition from PWM Disable mode when SI1 stays "high" by switching SI2 = "high" is prohibited, because when the safety inputs are cross connected to the safety inputs of the opposing gate driver inside a halfbridge topology, the opposing gate driver will otherwise remain in the ASCP\_ON mode.

When the device is powered-up with SI1 = SI2 = "high" and the device is ready it transitions directly from PWM Disable into PWM Enable.

Figure 5 Safety inputs diagram

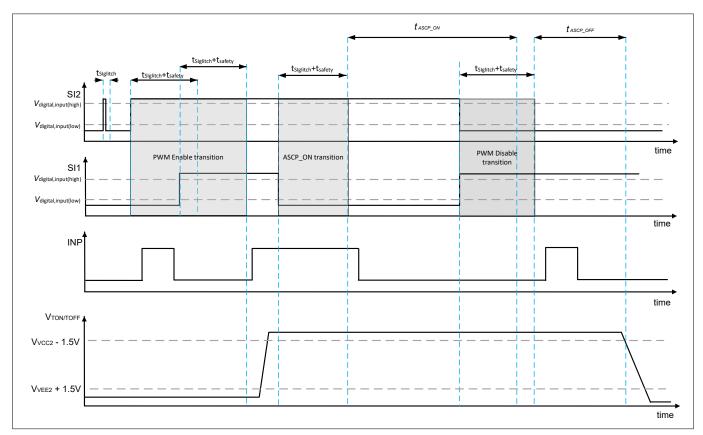

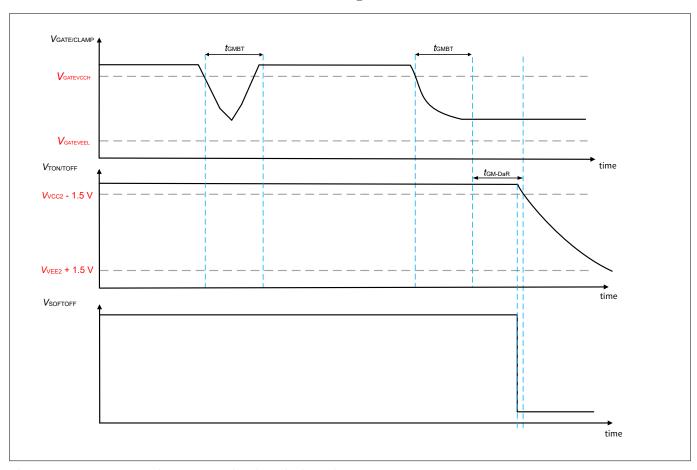

## 5.2 Functional description of safety related timings

The device can be switched in between the operating modes via valid signal transitions of SI1 & SI2 from "low" to "high" or "high" to "low".

The safety inputs SI1 and SI2 recognize a valid signal transition in case the signal transition is stable for more than  $t_{\text{SIglitch.}}$

In case the signal is stable for less than  $t_{Slglitch}$  the safety transition timer  $t_{safety}$  is not activated and the signal transition is not valid.

At the timestamp of a valid transition from "low" to "high" or "high" to "low" on one safety input a timer starts to count. This time is defined as  $t_{\text{safety}}$ .

In case of an additional valid signal transition on any safety input during  $t_{\text{safety}}$  the timer is started again. If there is no additional valid signal transition during  $t_{\text{safety}}$  on any safety input the state transition is executed.

#### 5 Primary Side safety control

In case the signal transition is beyond the defined safety transition timer the device is executing the recognized state transition after  $t_{\text{safety}}$  is elapsed.

The  $t_{SI-OFF}$  delay defines the delay between following state transitions:

- from PWM Enable mode to PWM Disable mode via the safety pin transitions SI1 = "low" and SI2 = "low".

- from ASCP\_ON mode to PWM Disable mode via the safety pin transitions SI1 stays "low" and SI2 = "low".

The  $t_{ASCP-ON}$  delay defines the delay between following state transitions:

- from PWM Enable mode to ASCP\_ON mode via the safety pin transitions SI1 = "low" and SI2 stays "high".

- from PWM Disable mode to ASCP\_ON mode via the safety pin transitions SI1 stays "low" and SI2 = "high".

The  $t_{ASCP-OFF}$  delay defines the delay between following state transitions:

- from PWM Enable mode to PWM Disable mode via the safety pin transitions SI1 stays "high" and SI2 = "low".

- from ASCP\_ON mode to PWM Disable mode via the safety pin transitions SI1 = "high" and SI2 = "low".

$t_{\rm Sltrans}$  is defined as the minimum time the device needs to stay in the dedicated operation mode state. Switching between states in less than  $t_{Sltrans}$  is prohibited.

Figure 6 Safety related timing diagram

Note: The minimum state transition time  $t_{Sltrans}$  is not reflected in the timing diagram

#### **5 Primary Side safety control**

## 5.3 Electrical characteristics primary side safety control

#### Table 9 Electrical characteristics primary side safety control

$T_J$  = -40°C to 150°C; all voltages with respect to ground, pos. current flowing into pin (unless otherwise specified).

Voltage supply inputs ( $V_{VCC1}$ ,  $V_{VCC2}$  and  $V_{VEE2}$ ) are within the functional range (unless otherwise specified).

| Parameter                               | Symbol                |      | Value | 5    | Unit | Note or condition                                                                                                                                                                                                                    | P-<br>Number |

|-----------------------------------------|-----------------------|------|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|                                         |                       | Min. | Тур.  | Max. |      |                                                                                                                                                                                                                                      |              |

| SI1, SI2 Pull<br>down<br>resistance     | R <sub>PDIN1</sub>    | 40   | 48    | 60   | kΩ   | V <sub>SI1</sub> = VCC1, V <sub>SI2</sub> = VCC1, VCC1 = 5V                                                                                                                                                                          | PRQ-349      |

| SI_OFF delay                            | t <sub>SI_OFF</sub>   | 0.95 | 1.15  | 1.35 | μs   | VCC1 = 5 V, VCC2 = 15 V, VEE2 = -5V, INP = "high", SI1 = "high" and SI2 = "high", start event is SI1 = "low" and SI2 = "low", after $t_{SIglitch}+t_{safety}$ $t_{SI\_OFF}$ is elapsed, stop event is TON = VCC2-1.5V, no load       | PRQ-665      |

| ASCP ON<br>delay                        | t <sub>ASCP_ON</sub>  | 4.60 | 5.00  | 5.45 | μs   | VCC1 = 5 V, VCC2 = 15 V, VEE2 = -5V, INP = "low", SI1 = "high" and SI2 = "high", start event is SI1 = "low" and SI2 = "high", after $t_{SIglitch}+t_{safety}$ $t_{ASCP\_ON}$ is elapsed, stop event is TON = VEE2+1.5V, no load      | PRQ-347      |

| ASCP OFF<br>delay                       | t <sub>ASCP_OFF</sub> | 0.95 | 1.10  | 1.35 | μs   | VCC1 = 5 V, VCC2 = 15 V, VEE2 = -5V, INP =<br>"high", SI1 = "high" and SI2 = "high", start event is SI1 = "high" and SI2 = "low", after $t_{SIglitch}+t_{safety}$ $t_{ASCP\_OFF}$ is elapsed, stop event is TON = VCC2-1.5V, no load | PRQ-348      |

| Safety<br>transition<br>timer           | $t_{\sf safety}$      | 550  | 670   | 737  | ns   | VCC1 = 5 V, VCC2 = 15 V, VEE2 = -5V, INP = high, SI1 = low high, SI2 = low high after $t_{\text{safety,max}}$                                                                                                                        | PRQ-358      |

| Safety glitch filter                    | t <sub>Siglitch</sub> | _    | -     | 20   | ns   | VCC1 = 5 V, VCC2 = 15 V, VEE2 = -5V, SI1 = SI2 = low high ▶ low within $t_{Slglitch}$                                                                                                                                                | PRQ-663      |

| Minimum<br>state<br>transition<br>timer | t <sub>Sltrans</sub>  | 8    | _     | _    | μs   |                                                                                                                                                                                                                                      | PRQ-661      |

# infineon

#### **6 Clear functionality**

## 6 Clear functionality

## 6.1 Functional description clear

In case the device recognizes an error reflected on NFLT or RDY the device operation mode switches to PWM Disable mode. An error is sticky.

All error bits can be cleared by a valid state transition starting from PWM Disable mode with SI1 = "low" and SI2 = "low":

- to PWM Enable mode by SI1 = "high" and SI2 = "high".

- to ASCP\_ON mode by SI1 = "low" and SI2 = "high".

If the error reflected on RDY or NFLT disappeared and the internal error bits can be cleared, the device switches back to ASCP ON mode or PWM Enable mode with the dedicated transition of SI1 and SI2.

#### Error

The following errors are mapped to an error bit:

- UVLO2

- UVLO3

- OVLO2

- DESAT error

- OSM error

- Gate monitoring error

- STP keep error

The life sign error is raised when the life sign was established once and then lost. The life sign error is not part of the DATA readout.

DATA readout contains the No life sign established bit. The No life sign established bit reflects the instantaneous status of the life sign.

In case of no life sign error is active all active errors remain sticky until a valid clear command.

If the error is present during the clear command, the clear command is not executed.

The device stays in PWM Disable mode and RDY or NFLT stays "low".

The clear command via safety inputs needs to be executed again.

#### Warning

In case a warning occurred and is recognized by the device it is notified via the diagnostic frame.

If the warning source is gone the warning bit is self-cleared after it was transmitted via the diagnostic frame

Warnings do not impact the state of NFLT or RDY.

Even with an activated warning bit the device can execute changes inside the operating states via the valid transitions of SI1 and SI2.

The following warnings are mapped to a warning bit:

- DESAT BIST warning

- Dead time warning

- SASC activation warning

# infineon

#### **6 Clear functionality**

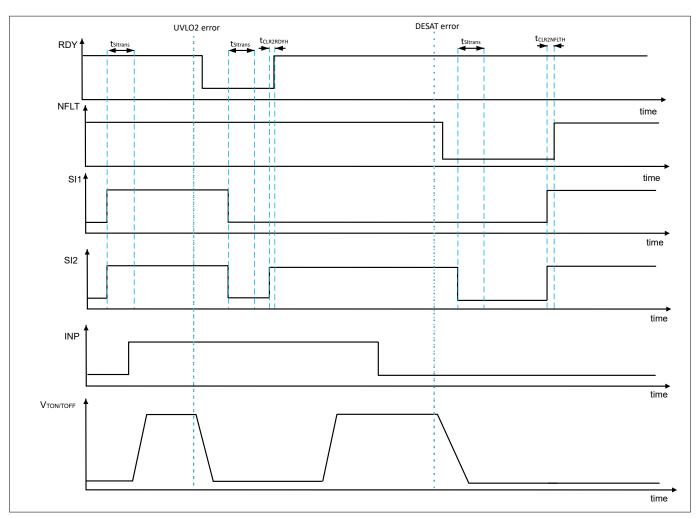

Figure 7 Clear of errors timing diagram

## **6.2** Electrical characteristics Clear

## Table 10 Electrical characteristics Clear

$T_J$  = -40°C to 150°C; all voltages with respect to ground, pos. current flowing into pin (unless otherwise specified).

Voltage supply inputs ( $V_{VCC1}$ ,  $V_{VCC2}$  and  $V_{VEE2}$ ) are within the functional range (unless otherwise specified).

| Parameter                  | Symbol                 | Values |      |      | Unit | Note or condition                                                                                                                               | P-      |

|----------------------------|------------------------|--------|------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                            |                        | Min.   | Тур. | Max. |      |                                                                                                                                                 | Number  |

| clear time to<br>NFLT high | t <sub>CLR2NFLTH</sub> | -      | _    | 1    | μs   | VCC1=5V; $10k\Omega$ pullup on NFLT to VCC1, SI1 = "low", SI2 = "low" , Start rising edge on SI2 to "high" , Stop rising edge on NFLT to "high" | PRQ-249 |

| clear time to<br>RDY high  | t <sub>CLR2RDYH</sub>  | _      | _    | 1    | μs   | VCC1=5V; $10k\Omega$ pullup on RDY to VCC1, SI1 = "low", SI2 = "low", Start rising edge on SI2 to "high", Stop rising edge on RDY to "high"     | PRQ-658 |

7 Power supply current consumption

## 7 Power supply current consumption

## 7.1 Functional description power supply current consumption

The device is designed to support two different supply configurations, bipolar supply and unipolar supply.

- In case the unipolar topology is used the device is typically supplied with 15 V on VCC2 and 0 V on VEE2.

- In case the bipolar topology is used the device is typically supplied with 15 V on VCC2 and -5 V on VEE2.

In any case of the mentioned topologies it is recommended to connect the GATE/CLAMP directly to the gate of the power semiconductor to prevent unintended turn on caused by parasitic capacitances of the power switch.

Figure 8 Current direction definition

$I_{\rm QVCC1}$  defines the quiescent current consumption of the primary chip in case it is supplied and in idle mode without INP switching.

$I_{\text{OPVCC1\_ON}}$  defines the operating current consumption of the primary chip in case it is supplied and the output stage is statically switched to "high".

$I_{\text{OPVCC1\_OFF}}$  defines the operating current consumption of the primary chip in case it is supplied and the output stage is statically switched to "low".

$I_{\text{OPVCC2\_ON}}$  defines the operating current consumption of the secondary chip on VCC2 in case it is supplied and the output stage is statically switched to "high".

$I_{\text{OPVCC2\_OFF}}$  defines the operating current consumption of the secondary chip on VCC2 in case it is supplied and the output stage is statically switched to "low".

$I_{\text{OPVEE2\_ON}}$  defines the operating current consumption of the secondary chip on VEE2 in case it is supplied and the output stage is statically switched to "high".

#### 7 Power supply current consumption

$I_{\text{OPVEE2\_OFF}}$  defines the operating current consumption of the secondary chip on VEE2 in case it is supplied and the output stage is statically switched to "low".

## 7.2 Electrical characteristics power supply current consumption

#### Table 11 Electrical characteristics power supply current consumption

$T_J$  = -40°C to 150°C; all voltages with respect to ground, pos. current flowing into pin (unless otherwise specified).

Voltage supply inputs ( $V_{VCC1}$ ,  $V_{VCC2}$  and  $V_{VEE2}$ ) are within the functional range (unless otherwise specified).

| Parameter                                         | Symbol                    | nbol Values |      |      | Unit | Note or condition                                                                                                                                                                                                                 | P-      |

|---------------------------------------------------|---------------------------|-------------|------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                                                   |                           | Min.        | Тур. | Max. |      |                                                                                                                                                                                                                                   | Number  |

| Quiescent<br>Current on<br>VCC1                   | I <sub>QVCC1</sub>        | 3           | 5    | -    | mA   | PWM Disable mode, all primary I/Os without impact on PWM Disable mode open, V <sub>VCC1</sub> = 5 V, V <sub>VCC2</sub> = 15 V, V <sub>VEE2</sub> = -5 V                                                                           | PRQ-94  |

| Operating Current VCC1 with TON = "high"          | I <sub>OPVCC1_ON</sub>    | _           | 12   | 14.5 | mA   | PWM Enable mode, INN = 0, INP = 1, SI1 = 1, SI2 = 1, outputs open, $V_{VCC1}$ = 5 V, $V_{VCC2}$ = 15 V, $V_{VEE2}$ = -5 V                                                                                                         | PRQ-95  |

| Operating<br>Current VCC1<br>with TOFF =<br>"low" | I <sub>OPVCC1_OFF</sub>   | _           | 5.5  | 7    | mA   | PWM Enable Mode, INN = 0, INP = 0, SI1, SI2= 1, outputs open, $V_{VCC1}$ = 5 V, $V_{VCC2}$ = 15 V, $V_{VEE2}$ = -5 V                                                                                                              | PRQ-96  |

| Operating<br>Current VCC2<br>with TON =<br>"high" | I <sub>OPVCC2_ON1</sub>   | -           | 11   | 13   | mA   | PWM Enable mode, INN = 0, INP = 1, SI1 = 1, SI2 = 1, other primary outputs open, DESAT = "low", Gate shorted to TON, $V_{VCC1} = 5 \text{ V}$ , $V_{VCC2} = 15 \text{ V}$ , $V_{VEE2} = -5 \text{ V}$ , other secondary pins open | PRQ-99  |

| Operating<br>Current VCC2<br>with TOFF =<br>"low" | I <sub>OPVCC2_OFF</sub> 1 | 6           | 11   | 13   | mA   | PWM Enable mode, INN = 0, INP = 0, SI1 = 1, SI2 = 1, other primary outputs open, DESAT = "low", Gate shorted to TOFF, $V_{VCC1}$ = 5 V, $V_{VCC2}$ = 15 V, $V_{VEE2}$ = -5 V, other pins open                                     | PRQ-100 |

| Operating<br>Current VEE2<br>with TON =<br>"high" | I <sub>OPVEE2_ON1</sub>   | -           | 1.5  | 2    | mA   | PWM Enable mode, INN = 0, INP = 1, SI1 = 1, SI2 = 1, other primary outputs open, DESAT = "low", Gate shorted to TON, $V_{VCC1}$ = 5 V, $V_{VCC2}$ = 15 V, $V_{VEE2}$ = -5 V, other secondary pins open                            | PRQ-101 |

| Operating<br>Current VEE2<br>with TOFF =<br>"low" | I <sub>OPVEE2_OFF</sub> 1 | 0.5         | 1.5  | 2.5  | mA   | PWM Enable mode, INN = 0, INP = 0, SI1 = 1, SI2 = 1, other primary outputs open, DESAT = "low", Gate shorted to TOFF, $V_{VCC1}$ = 5 V, $V_{VCC2}$ = 15 V, $V_{VEE2}$ = -5 V, other secondary pins open                           | PRQ-102 |

#### 8 Power supply monitoring

## 8 Power supply monitoring

## 8.1 Functional description power supply monitoring

The time  $t_{PS2RDY}$  is defining the time from the detection of an undervoltage or an overvoltage event on any of the monitored voltage rails VCC1 ,VCC2 ,VEE2 until the notification by changing RDY to "low".

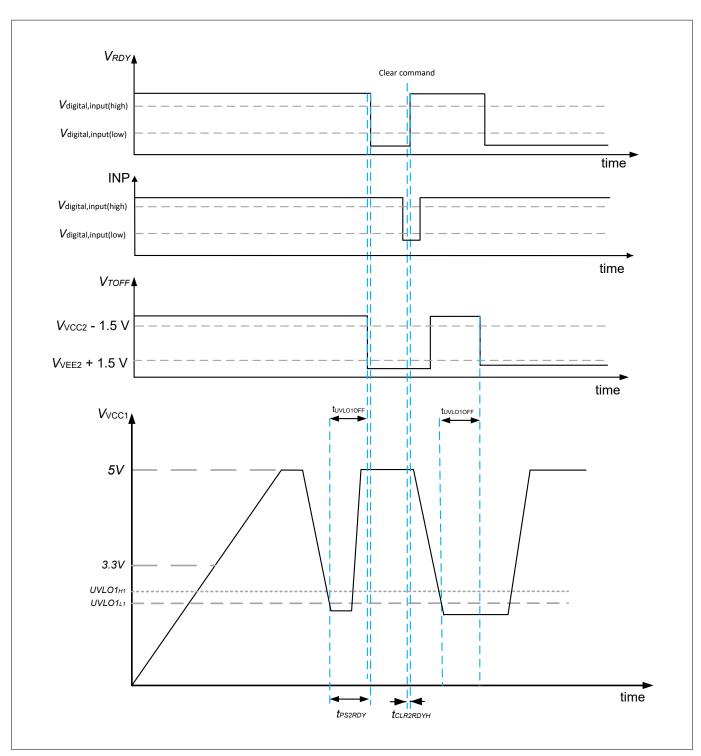

## 8.1.1 Functional description at VCC1

The device is equipped with an undervoltage lockout on the primary supply of VCC1 in order to ensure the correct behavior of the device.

In case the voltage on VCC1 is exceeding  $V_{\text{UVLO1,H1}}$  the primary side state changes from power down mode into PWM Disable mode.

Note: In all undervoltage conditions SASC signal still works until voltage drops below V<sub>ASCOFF</sub> at VCC2. Primary ASC via SI1 and SI2 is deactivated in case UVLO1 is detected.

The detection & reaction time  $t_{\text{UVLO1OFF}}$  is started by crossing the low threshold of undervoltage functionality  $V_{\text{UVLO1L}\_1}$ , and stops when TON =  $V_{\text{VCC2}}$  - 1.5V. The reaction is taken whether the fault is cleared during  $t_{\text{UVLO10FF}}$  or not.

In case the voltage on VCC1 drops below  $V_{\text{UVLO1L}-1}$  the device changes into Primary INIT mode.

#### 8 Power supply monitoring

Figure 9 UVLO1 detailed scheme

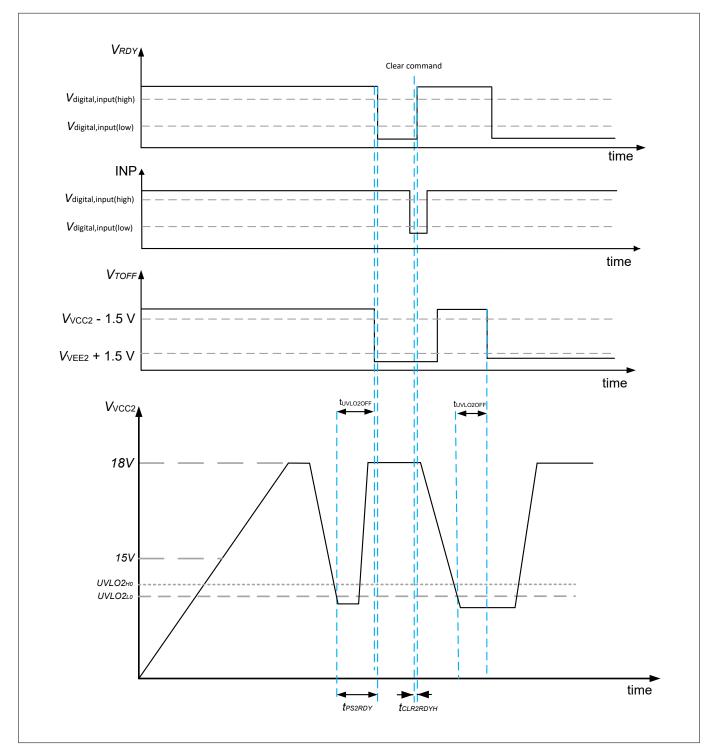

## 8.1.2 Functional description at VCC2

The device is equipped with a undervoltage monitoring on VCC2 supply rail to prevent damage of the power switch..

In case an undervoltage on VCC2 is detected, the device executes a regular turn off sequence after  $t_{\text{UVLO2OFF}}$ .

- Primary side input signals on INP and INN are ignored.

- The device changes its operation state to PWM Disable mode.

#### 8 Power supply monitoring

- RDY is switched to "low" within detection and notification time  $t_{PS2RDY}$ .

- Diagnostics are available on DATA output.

If  $V_{VCC2}$  decreases below  $V_{UVLO2L1}$  the undervoltage lockout gets active.

The detection & reaction time  $t_{\rm UVLO2OFF}$  is started by crossing the low threshold of undervoltage functionality  $V_{\rm UVLO2L_0}$ , and stops when TON =  $V_{\rm VCC2}$  - 1.5V. The reaction is taken whether the fault is cleared during  $t_{\rm UVLO2OFF}$  or not.

Figure 10 UVLO2 scheme

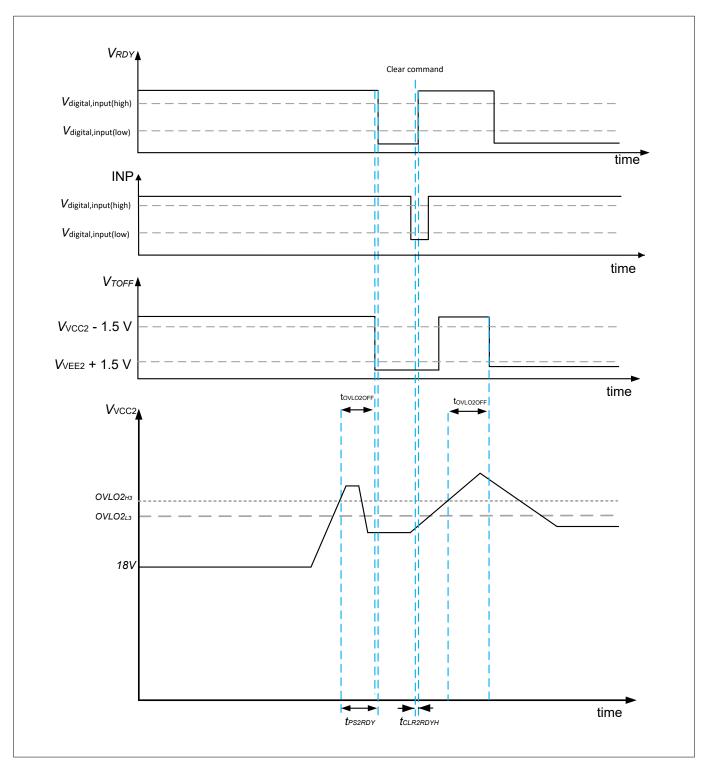

The device is equipped with an overvoltage lockout for the secondary supply VCC2 in order to prevent damage of the power switch.

#### 8 Power supply monitoring

In case there is an overvoltage on VCC2 supply, the device executes a regular turn off sequence after  $t_{\text{OVLO2OFF}}$ .

- Primary side input signals on INP and INN are ignored.

- The device changes its operation state to PWM Disable mode.

- RDY is switched to "low" within detection and notification time  $t_{PS2RDY}$ .

- Diagnostics are available on DATA output.

Note: SASC signal will overwrite the turn-off command, which may lead to damage of the power switch.

The detection & reaction time  $t_{\text{OVLO2OFF}}$  is started by crossing the high threshold of overvoltage functionality  $V_{\text{OVLO2H}\_3}$ , and stops when TON =  $V_{\text{VCC2}}$  - 1.5V. The reaction is taken whether the fault is cleared during  $t_{\text{OVLO2OFF}}$  or not.

# infineon

#### 8 Power supply monitoring

Figure 11 OVLO2 scheme

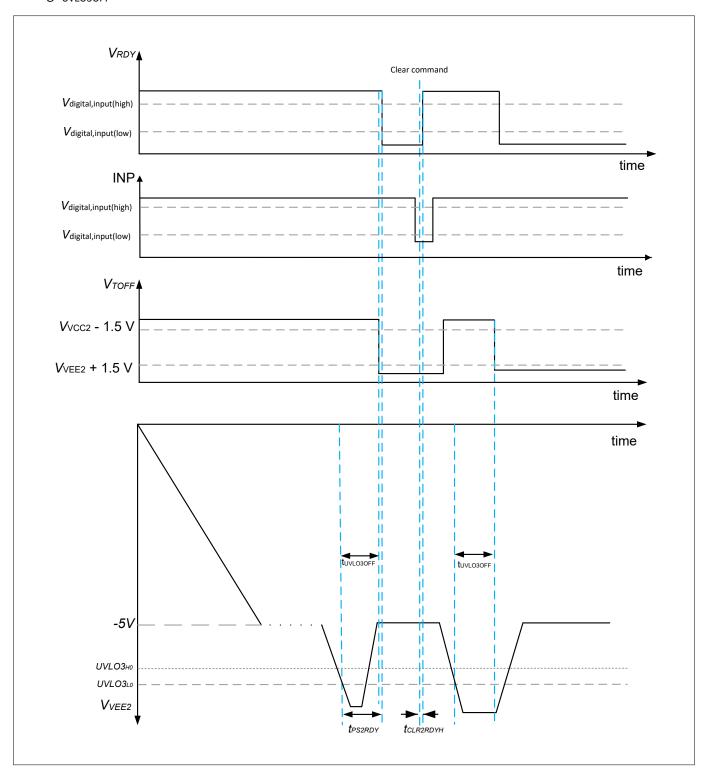

## 8.1.3 Functional description at VEE2

The device is equipped with an undervoltage lockout to prevent damage on the power switch.

In case an undervoltage on VEE2 is detected, the device executes a regular turn off sequence after  $t_{\rm UVLO30FF}$ .

31

- Primary side input signals on INP and INN are ignored.

- The device changes its operation state to PWM Disable mode.

- RDY is switched to "low" within detection and notification time t<sub>PS2RDY</sub>.

- Diagnostics are available on DATA output.

#### 8 Power supply monitoring

Note: SASC signal will overwrite the turn-off command.

The detection & reaction time  $t_{\rm UVLO3OFF}$  is started by crossing the low threshold of undervoltage functionality  $V_{\rm UVLO3L_0}$ , and stops when TON =  $V_{\rm VCC2}$  - 1.5V. The reaction is taken whether the fault is cleared during  $t_{\rm UVLO3OFF}$  or not.

Figure 12 UVLO3 scheme

## 8 Power supply monitoring

## 8.2 Electrical characteristics power supply monitoring

#### Table 12 Electrical characteristics power supply monitoring

$T_J$  = -40°C to 150°C; all voltages with respect to ground, pos. current flowing into pin (unless otherwise specified).

Voltage supply inputs ( $V_{VCC1}$ ,  $V_{VCC2}$  and  $V_{VEE2}$ ) are within the functional range (unless otherwise specified).

| Parameter                                                              | Symbol                | Values |      |      | Unit | Note or condition                                                                                                                                   | P-      |

|------------------------------------------------------------------------|-----------------------|--------|------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                                                                        |                       | Min.   | Тур. | Max. |      |                                                                                                                                                     | Number  |

| Power supply<br>monitoring<br>detection<br>and<br>notification<br>time | t <sub>PS2RDY</sub>   | -      | -    | 2.5  | μs   | VCC2 = typ., VEE2 = typ.                                                                                                                            | PRQ-183 |

| Voltage<br>lockout<br>threshold<br>activation<br>timer                 | $t_{ m VLO,active}$   | 95     | 100  | 106  | μs   |                                                                                                                                                     | PRQ-405 |

| UVLO1<br>threshold<br>low                                              | V <sub>UVLO1L_1</sub> | 2.6    | 2.75 | 2.91 | V    | VCC1, referenced to GND1                                                                                                                            | PRQ-409 |

| UVLO1<br>threshold<br>high                                             | V <sub>UVLO1H_1</sub> | 2.71   | 2.85 | 2.95 | V    | VCC1, referenced to GND1                                                                                                                            | PRQ-160 |

| UVLO1<br>detection &<br>reaction time                                  | t <sub>UVLO1OFF</sub> | _      | 500  | 800  | ns   | no $C_{LOAD}$ , no $R_{LOAD}$<br>Start: $V_{VCC1} < V_{UVLO1L_1}$ with Slewrate = 2 V/µs, Overdrive = +/- 400 mV,<br>Stop: TON = $V_{VCC2}$ - 1.5 V | PRQ-180 |

| UVLO2<br>threshold<br>low                                              | V <sub>UVLO2L_0</sub> | 11.6   | 12.0 | 12.4 | V    | @ VCC2, referenced to GND2                                                                                                                          | PRQ-172 |

| UVLO2<br>threshold<br>high                                             | V <sub>UVLO2H_0</sub> | 12.0   | 12.4 | 12.8 | V    | @ VCC2, referenced to GND2                                                                                                                          | PRQ-171 |

| UVLO2<br>detection &<br>reaction time                                  | t <sub>UVLO2OFF</sub> | _      | 500  | 800  | ns   | no $C_{LOAD}$ , no $R_{LOAD}$ ,<br>Start: $V_{VCC2} < V_{UVLO2L_x}$ with Slewrate=10 V/µs; Overdrive=+/-400 mV,<br>Stop: TON = $V_{VCC2}$ - 1.5 V   | PRQ-181 |

| OVLO2<br>threshold<br>low                                              | V <sub>OVLO2L_3</sub> | 20.6   | 21.3 | 22.0 | V    | @ VCC2, referenced to GND2                                                                                                                          | PRQ-169 |

## 8 Power supply monitoring

## Table 12 (continued) Electrical characteristics power supply monitoring

$T_J$  = -40°C to 150°C; all voltages with respect to ground, pos. current flowing into pin (unless otherwise specified).

Voltage supply inputs ( $V_{VCC1}$ ,  $V_{VCC2}$  and  $V_{VEE2}$ ) are within the functional range (unless otherwise specified).

| Parameter                             | Symbol                | ymbol Values |      |      | Unit | Note or condition                                                                                               | P-      |

|---------------------------------------|-----------------------|--------------|------|------|------|-----------------------------------------------------------------------------------------------------------------|---------|

|                                       |                       | Min.         | Тур. | Мах. |      |                                                                                                                 | Number  |

| OVLO2<br>threshold<br>high            | V <sub>OVLO2H_3</sub> | 21.2         | 22.0 | 22.5 | V    | @ VCC2, referenced to GND2                                                                                      | PRQ-168 |

| OVLO2<br>detection &<br>reaction time | t <sub>OVLO2OFF</sub> | -            | 500  | 800  | ns   | no $C_{LOAD}$ , no $R_{LOAD}$ ,<br>Start: $V_{VCC2} > V_{OVLO2H_x}$ with Slewrate=10 V/µs; Overdrive=+/-400 mV, | PRQ-568 |

|                                       |                       |              |      |      |      | Stop: TON = $V_{VCC2}$ - 1.5 V                                                                                  |         |

| UVLO3<br>threshold<br>low             | V <sub>UVLO3L_1</sub> | -7.65        | -7.2 | -6.9 | V    | @ VEE2, referenced to GND2                                                                                      | PRQ-412 |

| UVLO3<br>threshold<br>high            | V <sub>UVLO3H_1</sub> | -6.8         | -6.4 | -6.1 | V    | @ VEE2, referenced to GND2                                                                                      | PRQ-413 |