# EVALPFC-300W-IPP60R190P6

300W PFC Evaluation Board IPP60R190P6 with CCM PFC controller

#### IFAT PMM APS SE SL

| Steiner Alois   | (IFAT PMM APS SE AC) |

|-----------------|----------------------|

| Stückler Franz  | (IFAT PMM APS SE AC) |

| Zechner Florian | (IFAT PMM APS SE AC) |

Edition 2011-02-02 Published by Infineon Technologies Austria AG 9500 Villach, Austria © Infineon Technologies Austria AG 2011. All Rights Reserved.

#### Attention please!

THE INFORMATION GIVEN IN THIS APPLICATION NOTE IS GIVEN AS A HINT FOR THE IMPLEMENTATION OF THE INFINEON TECHNOLOGIES COMPONENT ONLY AND SHALL NOT BE REGARDED AS ANY DESCRIPTION OR WARRANTY OF A CERTAIN FUNCTIONALITY, CONDITION OR QUALITY OF THE INFINEON TECHNOLOGIES COMPONENT. THE RECIPIENT OF THIS APPLICATION NOTE MUST VERIFY ANY FUNCTION DESCRIBED HEREIN IN THE REAL APPLICATION. INFINEON TECHNOLOGIES HEREBY DISCLAIMS ANY AND ALL WARRANTIES AND LIABILITIES OF ANY KIND (INCLUDING WITHOUT LIMITATION WARRANTIES OF NON-INFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS OF ANY THIRD PARTY) WITH RESPECT TO ANY AND ALL INFORMATION GIVEN IN THIS APPLICATION NOTE.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (<a href="www.infineon.com">www.infineon.com</a>).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office. Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

AN 2013-03

Revision History: date (13-06-07) , V1.0

Previous Version: none Subjects: 1<sup>st</sup> revision

Authors: Steiner Alois (IFAT PMM APS SE AC)

Stückler Franz (IFAT PMM APS SE AC)

Zechner Florian (IFAT PMM APS SE AC)

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: [alois.steiner@infineon.com]

### **Table of contents**

| 1  | Introduktion |                                                        | Error! Bookmark not defined. |  |  |

|----|--------------|--------------------------------------------------------|------------------------------|--|--|

|    | 1.1          | CoolMOS™ P6                                            | 4                            |  |  |

|    | 1.2          | thinQ!™ SiC Diode Generation 5                         | 4                            |  |  |

|    | 1.3          | CCM-PFC Controller                                     | 4                            |  |  |

| 2  | Evalu        | ation Board                                            | 5                            |  |  |

| 3  | Techr        | nical Specifications                                   | 5                            |  |  |

| 4  | Circu        | it Description                                         | 5                            |  |  |

|    | 4.1          | Line Input                                             | 5                            |  |  |

|    | 4.2          | Power Stage – Boost Type PFC Converter                 | 6                            |  |  |

|    | 4.3          | PWM Control of Boost Converter                         | 6                            |  |  |

| 5  | Circu        | it Operation                                           | 6                            |  |  |

|    | 5.1          | Soft Startup                                           | 6                            |  |  |

|    | 5.2          | Boost Follower                                         | 6                            |  |  |

|    | 5.3          | Gate Switching Frequency                               | 7                            |  |  |

|    | 5.4          | Protection Features                                    | 7                            |  |  |

|    | 5.4          | .1 Input brown-out protection (BOP)                    | 7                            |  |  |

|    | 5.4          | 8                                                      |                              |  |  |

|    | 5.4          | .3 First over-voltage protection (OVP1)                | 8                            |  |  |

|    | 5.4          | .4 Second over-voltage protection (OVP2)               | 8                            |  |  |

|    |              | .5 Peak current limit                                  |                              |  |  |

|    |              | .6 IC supply under voltage lockout                     |                              |  |  |

|    | 5.4          | .7 Bulk Voltage Monitor and Enable Function (VBTHL_EN) | 8                            |  |  |

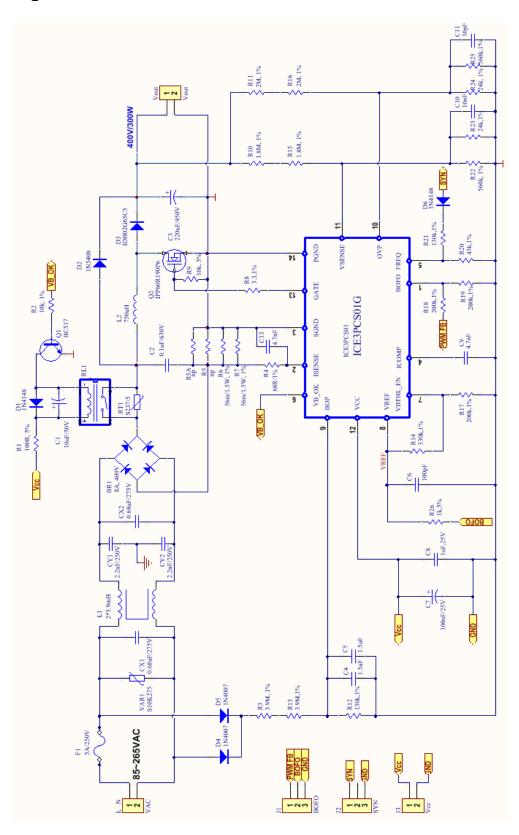

| 6  | Circu        | it Diagram                                             | 9                            |  |  |

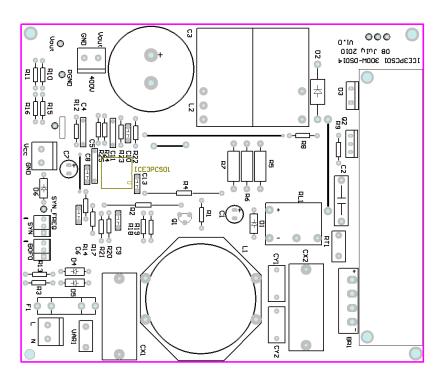

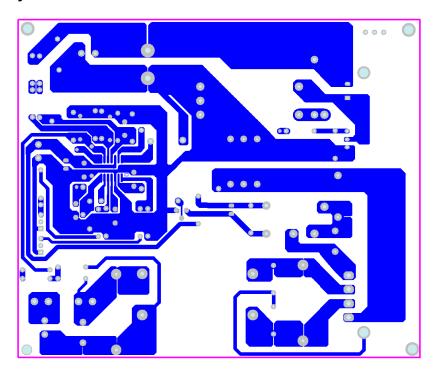

| 7  | PCB I        | _ayout                                                 | 10                           |  |  |

|    | 7.1          | Top layer view                                         | 10                           |  |  |

|    | 7.2          | Bottom layer view                                      | 10                           |  |  |

| 8  | Comp         | onent List                                             | 11                           |  |  |

| 9  | Boost        | t Choke Layout                                         | 12                           |  |  |

|    | 12           |                                                        |                              |  |  |

| 10 | Test r       | eport                                                  | 13                           |  |  |

|    | 10.1         | Load and Line Test                                     | 13                           |  |  |

|    | 10.2         | 14                                                     |                              |  |  |

| 11 | Pofor        | 0000                                                   | 1.4                          |  |  |

#### Introduktion

#### 1.1 CoolMOS™ P6

CoolMOS™ P6 <u>IPP60R190P6</u> achieves extremely low conduction and switching losses especially in light load condition enabling switching applications to work more efficient and be designed more compact, lighter and cooler.

Moreover, with its granular portfolio, P6 can address the specific needs of applications such as server, PC power, telecom rectifiers and consumer applications, while additionally offering the best price/performance ratio on the market today.

<u>CoolMOS™ P6</u> closes the gap between technologies which focus on delivering ultimate performance, such as the high performance CoolMOS™ CP, and those which concentrate more on ease of use, for example CoolMOS™ C6/E6.

### 1.2 thinQ!™ SiC Diode Generation 5

thinQ!™ Generation 5 <u>IDH02G65C5</u> represents Infineon's leading edge technology for SiC Schottky Barrier diodes. The Infineon proprietary diffusion soldering process, already introduced with G3, is now combined with a new, more compact design and thin wafer technology. The result is a new family of products showing improved efficiency over all load conditions, coming from both the improved thermal characteristics and a lower figure of merit (Q c x V f).

#### 1.3 CCM-PFC Controller

The evaluation board presented here is a 300W power factor correction (PFC) circuit with 85~265VAC universal input and output of 395VDC rated voltage or 333VDC in boost follower mode. The continuous conduction mode (CCM) PFC controller <a href="ICE3PCS01G">ICE3PCS01G</a> is employed in this board to achieve the unity power factor.

This <a href="ICE3PCS01G">ICE3PCS01G</a> is specially designed for applications of power supplies used in PC, server, LCD/PDP TV and Telecom, requesting high efficiency and power factor. The voltage loop compensation is integrated digitally for better dynamic response and less design effort. Appreciated for its high integrated design, <a href="ICE3PCS01G">ICE3PCS01G</a> can achieve full requirements of the PFC application implemented in the 14-pin in DS014 package. At the same time the number of peripheral components is minimized. The gate switching frequency is adjustable from 21kHz to 250kHz and able to synchronize with external switching frequency from 50kHz to 150kHz.

### 2 Evaluation Board

Figure 1 IPP60R190P6 Demoboard

### 3 Technical Specifications

| Input voltage              | 85VAC~265VAC                                       |

|----------------------------|----------------------------------------------------|

| Input frequency            | 47~63Hz                                            |

| Output voltage and current | 395VDC, 0.75A                                      |

| Output power               | ~ 300W                                             |

| Average efficiency         | >95% at 115VAC                                     |

| Switching Frequency        | Possible Range: 21kHz~250kHz; set by R20 to 100kHz |

## 4 Circuit Description

### 4.1 Line Input

The AC line input side comprises the input fuse F1 as over-current protection. The choke L1, X2-capacitors CX1/CX2 and Y1-capacitor CY1/CY2 are used to suppress common mode noise as well as differential mode noise. RT1 is placed in series to limit inrush current during each power on. A relay is mounted across the RT1 to short the resistor when VOUT is higher than 95% rated voltage.

### 4.2 Power Stage – Boost Type PFC Converter

After the bridge rectifier BR1, there is a boost type PFC converter consisting of L2, Q2, D3 and C3. The seventh generation CoolMOS™ IPP60R190P6 is used as the power switch Q2. BR1, Q2 and SiC Diode D3 share the same heat sink so that the system heat can be equably spread. Output capacitor C3 provides energy buffering to reduce the output voltage ripple (100Hz at 50Hz AC input) to the acceptable level and meet the holdup time requirement.

#### 4.3 PWM Control of Boost Converter

The ICE3PCS01G is a 14-pins control IC for power factor correction converters. It is suitable for wide range line input applications from 85 to 265 VAC with overall efficiency above 97%. The IC supports converters in boost topology and it operates in continuous conduction mode (CCM) with average current control.

The IC operates with a cascaded control; the inner current loop and the outer voltage loop. The inner current loop of the IC controls the sinusoidal profile for the average input current. It uses the dependency of the PWM duty cycle on the line input voltage to determine the corresponding input current. This means the average input current follows the input voltage as long as the device operates in CCM. Under light load condition, depending on the choke inductance, the system may enter into discontinuous conduction mode (DCM) resulting in a higher harmonics but still meeting the Class D requirement of IEC 1000-3-2.

The outer voltage loop controls the output bulk voltage, integrated digitally within the IC. Depending on the load condition, internal PI compensation output is converted to an appropriate DC voltage which controls the amplitude of the average input current.

The IC is equipped with various protection features to ensure safe operating condition for both the system and device.

### **5** Circuit Operation

### 5.1 Soft Startup

During power up when the  $V_{\text{OUT}}$  is less than 96% of the rated level, internal voltage loop output increases from initial voltage under the soft-start control. This results in a controlled linear increase of the input current from 0A thus reducing the current stress in the power components.

Once  $V_{\text{OUT}}$  has reached 96% of the rated level, the soft-start control is released to achieve good regulation and dynamic response and VB\_OK pin outputs 5V indicating PFC output voltage in normal range.

### 5.2 Boost Follower

The IC provides adjustable lower step of bulk voltage in case of low line input and light output power. The low line condition is determined when pin BOP voltage is less than 2.3V. Pin BOFO is connected to PWM feedback voltage through a voltage divider, representing the output power. The light load condition is determined when pin BOFO voltage is less than 0.5V. Once these two conditions are met in the same time, a 20uA current source is flowing out of pin VSENSE so that the bulk voltage should be reduced to a lower level in order to keep the VSENSE voltage same as the internal reference 2.5V.

The reduced bulk voltage can be designed by upper side resistance of voltage divider from pin VSENSE. Thus the low side resistance is designed by the voltage divider ratio from the reference 2.5V to the rated bulk voltage. An internal  $300k\Omega$  resistor will be paralleled with external low side resistor of BOFO pin to provide the adjustable hysteresis for entry/exit power when boost follower is activated.

The boost follower feature will be disabled internally during PFC soft-start in order to prevent bulk voltage oscillation due to the unstable PWM feedback voltage. This feature is disabled on this demo board externally by pulling up pin BOFO higher than 0.5V continuously by R26 and closed Jumper1 between pin 1 and pin2. To use the boost follower feature as described above, please just remove the jumper 1 connection between pin 1 and pin 2.

### 5.3 Gate Switching Frequency

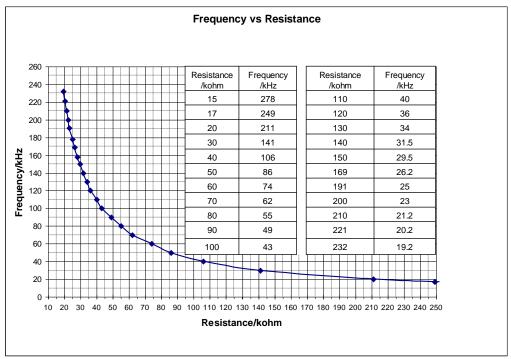

The switching frequency of the PFC converter can be set with an external resistor  $R_{\text{FREQ}}$  at pin FREQ with reference to pin SGND. The voltage at pin FREQ is typical 1V. The corresponding capacitor for the oscillator is integrated in the device and the  $R_{\text{FREQ}}$ /frequency is given in Figure 2. The recommended operating frequency range is from 21 kHz to 250 kHz. As an example, a  $R_{\text{FREQ}}$  of 43k $\Omega$  at pin FREQ will set a switching frequency  $F_{\text{SW}}$  of 100 kHz typically.

Figure 2 Frequency setting

The switching frequency can be synchronized to the external pulse signal after 6 external pulses delay once the voltage at the FREQ pin is higher than 2.5V. The synchronization means two points. Firstly, the PFC switching frequency is tracking the external pulse signal frequency. Secondly, the falling edge of the PFC signal is triggered by the rising edge of the external pulse signal. The external R20 combined with R21 and the external diode, D6 can ensure FREQ pin voltage to be kept between 1.0V (clamped internally) and 5V (maximum pin voltage). If the external pulse signal has disappeared longer than 108us (typical) the switching frequency will be synchronized to internal clock set by the external resistor R20.

### 5.4 Protection Features

#### 5.4.1 Input brown-out protection (BOP)

ICE3PCS01G provides a new BOP feature whereby it senses directly the input voltage for Input Brown-Out condition via an external resistor/capacitor/diode network. This network provides a filtered value of  $V_{IN}$  which turns the IC on when the voltage at pin 9 (BOP) is more than 1.25V. The IC enters into the fault mode when BOP goes below 1.0V. The hysteresis prevents the system to oscillate between normal and fault mode. Note also that the peak of  $V_{IN}$  needs to be at least 20% of the rated  $V_{OUT}$  in order to overcome open loop protection and power up system.

### 5.4.2 Open loop protection (OLP)

The open loop protection is available for this IC to safe-guard the output. Whenever voltage at pin VSENSE falls below 0.5V, or equivalently  $V_{\text{OUT}}$  falls below 20% of its rated value, it indicates an open loop condition (i.e. VSENSE pin not connected). In this case, most of the blocks within the IC will be shutdown. It is implemented using a comparator with a threshold of 0.5V.

### 5.4.3 First over-voltage protection (OVP1)

Whenever  $V_{OUT}$  exceeds the rated value by 8%, the first over-voltage protection OVP1 is active. This is implemented by sensing the voltage at pin VSENSE with respect to a reference voltage of 2.7V. A VSENSE voltage higher than 2.7V will immediately block the gate signal. After bulk voltage falls below the rated value, gate drive resumes switching again.

### 5.4.4 Second over-voltage protection (OVP2)

The second OVP (OVP2) is provided in case that the first one fails due to the aging or incorrect resistors connected to the VSENSE pin. This is implemented by sensing the voltage at pin OVP with respect to a reference voltage of 2.5V. When voltage at OVP pin is higher than 2.5V, the IC will immediately turn off the gate, thereby preventing damage to bus capacitor.

When the bulk voltage drops out of the hysteresis, which is below 2.3V the IC can be latched further or begin auto soft-start. These two protection modes are distinguished through detecting the external equivalent resistance connecting to VBTHL\_EN pin after  $V_{CC}$  is higher than UVLO threshold. If the equivalent resistance is higher than 100k  $\Omega$  the IC selects latch mode for second OVP, otherwise auto soft-start mode.

In normal operation the trigger level of OVP2 should be designed higher than OVP1. However in the condition of mains transient overshoot the bulk voltage may be pulled up to the peak value of mains that is higher than the threshold of OVP1 and OVP2. In this case the OVP1 and OVP2 are triggered in the same time the IC will shut down the gate drive until bulk voltage falls out of the two protection hysteresis, then resume the gate drive again

### 5.4.5 Peak current limit

The IC provides a cycle by cycle peak current limitation (PCL). It is active when the voltage at pin ISENSE reaches -0.2V. This voltage is amplified by a factor of -5 and connected to comparator with a reference voltage of 1.0V. A deglitcher with 200ns after the comparator improves noise immunity to the activation of this protection. In other words, the current sense resistor should be designed lower than -0.2V PCL for normal operation.

#### 5.4.6 IC supply under voltage lockout

When  $V_{CC}$  voltage is below the under voltage lockout threshold  $V_{CCUVLO}$ , typical 11V, IC is off and the gate drive is internally pull low to maintain the off state. The current consumption is down to 1.4mA only.

### 5.4.7 Bulk Voltage Monitor and Enable Function (VBTHL EN)

The IC monitors the bulk voltage status through VSENSE pin and output a TTL signal to enable PWM IC or control inrush relay. During soft-start once the bulk voltage is higher than 95% rated value, pin VB\_OK outputs a high level. The threshold to trigger the low level is decided by the pin VBTHL voltage adjustable externally.

When pin VBTHL is pulled down externally lower than 0.5V most function blocks are turned off and the IC enters into standby mode for low power consumption. When the disable signal is released the IC recovers by soft-start.

# 6 Circuit Diagram

# 7 PCB Layout

### 7.1 Top layer view

### 7.2 Bottom layer view

# 8 Component List

|            | Component List     |                               |                         |  |  |  |  |

|------------|--------------------|-------------------------------|-------------------------|--|--|--|--|

| Designator | Part Type          | Description                   | Manufacturer/ Part No.  |  |  |  |  |

| BR1        | 8A, 400V           | Bridge Rectifier              | Vishay / KBU8G          |  |  |  |  |

| C1         | 10uF/50V           | Electrolytic Cap              |                         |  |  |  |  |

| C2         | 0.1uF/630V         | Ceramic Cap                   | Epcos / B32652A6104J    |  |  |  |  |

| C3         | 220uF/450V         | Electrolytic Cap              | Epcos / B43304C5227M    |  |  |  |  |

| C4         | 1.5 uF/50V         | Ceramic Cap                   |                         |  |  |  |  |

| C5         | 1.5 uF/50V         | Ceramic Cap                   |                         |  |  |  |  |

| C6         | 100pF/50V          | Ceramic Cap                   |                         |  |  |  |  |

| C7         | 100uF/25V          | Electrolytic Cap              |                         |  |  |  |  |

| C8         | 1uF/25V            | Ceramic Cap                   |                         |  |  |  |  |

| C9         | 4.7nF/50V          | Ceramic Cap                   |                         |  |  |  |  |

| C10        | 10nF/50V           | Ceramic Cap                   |                         |  |  |  |  |

| C11        | 10pF/50V           | Ceramic Cap                   |                         |  |  |  |  |

| C13        | 4.7nF/50V          | Ceramic Cap                   |                         |  |  |  |  |

| CX1        | 0.68uF, X1, 275V   | Ceramic Cap                   | Epcos / B32922C3474M    |  |  |  |  |

| CX2        | 0.68uF, X1, 275V   | Ceramic Cap                   | Epcos / B32922C3474M    |  |  |  |  |

| CY1        | 2.2nF, Y2, 250V    | Ceramic Cap                   | Epcos / B81123C1222M000 |  |  |  |  |

| CY2        | 2.2nF, Y2, 250V    | Ceramic Cap                   | Epcos / B81123C1222M000 |  |  |  |  |

| D1         | 1N4148             | Diode                         |                         |  |  |  |  |

| D2         | 1N5408             | Diode                         | Vishay / 1N5408         |  |  |  |  |

| D3         | IDH02G65C5         | Diode                         | Infineon Technologies   |  |  |  |  |

| D4         | 1N4007             | Diode                         | Vishay / 1N4007         |  |  |  |  |

| D5         | 1N4007             | Diode                         | Vishay /1N4007          |  |  |  |  |

| D6         | 1N4148             | Diode                         |                         |  |  |  |  |

| F1         | 5A                 | Fuse                          |                         |  |  |  |  |

| IC1        | ICE3PCS01G         | DSO-14                        | Infineon Technologies   |  |  |  |  |

| J1         | Jumper             | Connector (BOFO)              |                         |  |  |  |  |

| J2         | Jumper             | Connector (SYNC)              |                         |  |  |  |  |

| J3         | Jumper             | Connector (V <sub>CC</sub> )  |                         |  |  |  |  |

| J4         | Jumper             | Connector (V <sub>IN</sub> )  |                         |  |  |  |  |

| J5         | Jumper             | Connector (V <sub>OUT</sub> ) |                         |  |  |  |  |

| L1         | 2*3.9mH            | CM Choke                      | Epcos / B82725J2602N20  |  |  |  |  |

| L2         | 750uH              | PFC Choke                     |                         |  |  |  |  |

| Q1         | BC517              | NPN Transistor                |                         |  |  |  |  |

| Q2         | <u>IPP60R190P6</u> | Power MOSFET                  | Infineon Technologies   |  |  |  |  |

| R1         | 100R/0.25W, 5%     | Carbon Film Resistor          |                         |  |  |  |  |

| R2         | 10k/0.25W, 1%      | Carbon Film Resistor          |                         |  |  |  |  |

| R3         | 3.9M/0.25W, 1%     | Carbon Film Resistor          |                         |  |  |  |  |

| R4         | 68/0.25W, 1%       | Carbon Film Resistor          |                         |  |  |  |  |

| R5A | 0.33/0.5W, 5%  | Metal Film Resistor  |

|-----|----------------|----------------------|

| R5  | 0.1/0.5W, 5%   | Metal Film Resistor  |

| R6  | 0.1/0.5W, 5%   | Metal Film Resistor  |

| R7  | 0.1/0.5W, 5%   | Metal Film Resistor  |

| R8  | 3.3/0.25W, 1%  | Carbon Film Resistor |

| R9  | 10k/0.25W, 5%  | Carbon Film Resistor |

| R10 | 1.8M/0.25W, 1% | Carbon Film Resistor |

| R11 | 2M/0.25W, 1%   | Carbon Film Resistor |

| R12 | 130k/0.25W, 1% | Carbon Film Resistor |

| R13 | 3.9M/0.25W, 1% | Carbon Film Resistor |

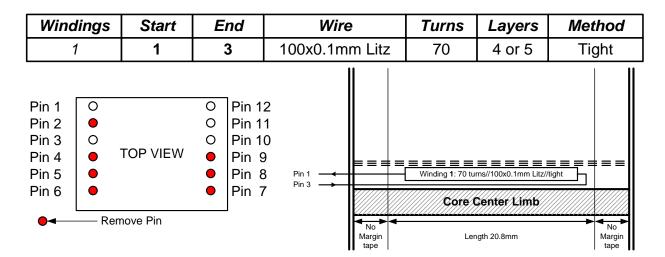

### 9 Boost Choke Layout

Manufacturer: Kaschke

Choke: AI1-KASCHKE-750UH-PQ3535

Inductance: L=750uH

# 10 Test report

All test condition are supply with Vcc=12V

### 10.1 Load and Line Test

|        | V <sub>IN</sub> | I <sub>IN</sub> | P <sub>IN</sub> | U <sub>out</sub> | I <sub>OUT</sub> | P <sub>OUT</sub> | Eff.   | PF      |

|--------|-----------------|-----------------|-----------------|------------------|------------------|------------------|--------|---------|

| Input  |                 |                 |                 |                  |                  |                  |        |         |

|        | 89,706          | 3,49803         | 313,3           | 379,84           | 0,78582          | 298,4859         | 95,272 | 0,99841 |

|        | 89,74           | 3,1073          | 278,39          | 379,819          | 0,70019          | 265,9455         | 95,53  | 0,99836 |

|        | 89,767          | 2,78335         | 249,41          | 379,788          | 0,62859          | 238,7309         | 95,718 | 0,99823 |

|        | 89,799          | 2,39961         | 215,1           | 379,761          | 0,54338          | 206,3545         | 95,934 | 0,99821 |

|        | 89,827          | 2,08104         | 186,58          | 379,755          | 0,47205          | 179,2634         | 96,079 | 0,99811 |

| 85Vac  | 89,859          | 1,70004         | 152,46          | 379,74           | 0,3863           | 146,6936         | 96,218 | 0,99798 |

|        | 89,886          | 1,38571         | 124,26          | 379,728          | 0,3151           | 119,6523         | 96,292 | 0,99759 |

|        | 89,918          | 1,01081         | 90,61           | 379,741          | 0,2296           | 87,18853         | 96,224 | 0,99689 |

|        | 89,949          | 0,64084         | 57,34           | 379,766          | 0,14473          | 54,96353         | 95,855 | 0,99478 |

|        | 89,976          | 0,32995         | 29,31           | 379,791          | 0,07434          | 28,23366         | 96,328 | 0,9874  |

|        | 229,9           | 1,3258          | 303,2           | 379,8            | 0,786            | 298,51           | 98,454 | 0,99488 |

|        | 229,9           | 1,1823          | 270,19          | 379,8            | 0,701            | 266,07           | 98,474 | 0,99402 |

|        | 229,9           | 1,0623          | 242,65          | 379,8            | 0,629            | 239              | 98,495 | 0,99353 |

|        | 229,9           | 0,9203          | 209,86          | 379,8            | 0,544            | 206,72           | 98,502 | 0,99186 |

|        | 229,9           | 0,8013          | 182,43          | 379,8            | 0,473            | 179,66           | 98,483 | 0,99009 |

| 230Vac | 230             | 0,6585          | 149,39          | 379,8            | 0,387            | 147,17           | 98,511 | 0,98648 |

|        | 230             | 0,5429          | 121,98          | 379,8            | 0,316            | 120,07           | 98,435 | 0,977   |

|        | 230             | 0,4033          | 89,08           | 379,8            | 0,23             | 87,499           | 98,225 | 0,96031 |

|        | 230             | 0,2685          | 56,36           | 379,8            | 0,145            | 55,163           | 97,877 | 0,9125  |

|        | 230             | 0,1638          | 29,05           | 379,8            | 0,074            | 28,116           | 96,784 | 0,77109 |

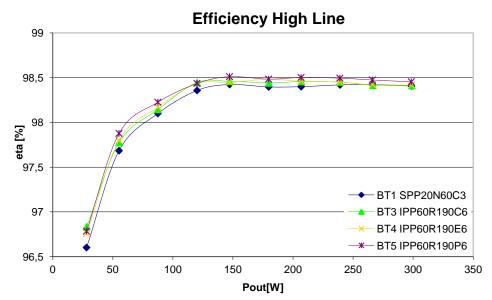

Figure 3 Efficiency High Line

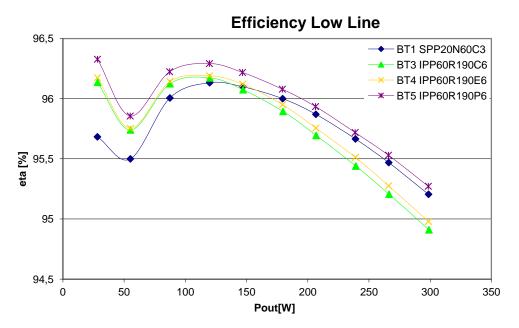

Figure 4 Efficiency Low Line

### 11 References

- [1] <u>ICE3PCS01G</u> datasheet, Infineon Technologies AG, 2010.

- [2] 600V CoolMOS™ P6 Power MOSFET, Product Brief, Infineon Technologies AG, 2012.

- [3] IDH02G65C5, datasheet, Infineon Technologies AG, 2012.