Power Management & Supply

| Revision               | n History: 2002-01                           | V1.2         |  |  |  |

|------------------------|----------------------------------------------|--------------|--|--|--|

| Previous Version: V1.1 |                                              |              |  |  |  |

| Page                   | Subjects (major changes since last revision) |              |  |  |  |

|                        | Document's layout has been change            | d: 2002-Sep. |  |  |  |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com.

CoolMOS<sup>™</sup>, CoolSET<sup>™</sup> are a trademarks of Infineon Technologies AG.

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

$\overline{\phantom{a}}$

#### **Edition 2002-01**

Published by Infineon Technologies AG, St.-Martin-Strasse 53, 81669 München, Germany

© Infineon Technologies AG 2002.

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide.

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life-support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

| Table of                  | f Contents                                                                                                        | Page |

|---------------------------|-------------------------------------------------------------------------------------------------------------------|------|

| 1                         | Abstract                                                                                                          | 4    |

| 2                         | Introduction                                                                                                      | 4    |

| 3                         | Selecting the Package                                                                                             | 6    |

| 4                         | How to Choose the Voltage Rating of the MOSFET?                                                                   | 6    |

| 5                         | How to Select the Operating Junction Temperature?                                                                 | 8    |

| 6                         | How to Choose the Current Rating of the MOSFET?                                                                   | 8    |

| 7                         | How to Choose the Right $R_{ds(on)}$ ?                                                                            | 9    |

| 8                         | How to Calculate the Maximum Power Losses for a Specific Junction Temperature?                                    |      |

| 9                         | How to Calculate the Power Losses?                                                                                | 13   |

| <b>10</b><br>10.1<br>10.2 | Conduction Losses                                                                                                 | 14   |

| <b>11</b><br>11.1<br>11.2 | Switching Losses  Discontinuous Conduction Mode Converter  Continuous and Discontinuous Conduction Mode Converter | 25   |

| <b>12</b><br>12.1<br>12.2 | Total Power Losses                                                                                                | 27   |

| <b>13</b><br>13.1<br>13.2 | Calculation of Peak Pulse Current                                                                                 | 31   |

| <b>14</b><br>14.1<br>14.2 | Maximum Output Power Capability                                                                                   | 34   |

| 15                        | Conclusion                                                                                                        | 37   |

AN-CoolMOS-03

### 1 Abstract

This application note is focusing on the selection of the high voltage MOSFET for Switched Mode Power Supply (SMPS). It shows a mathematical way to select the MOSFET with the intention to accelerate the design cycle of a SMPS.

Iteration process is introduced to evaluate as well the maximum allowable power dissipation as the conduction and switching power losses of the MOSFET. Maximum peak pulse current for discontinuous and continuous conduction mode converters has been calculated. To simplify the first iteration, charts of the output power handling capability versed the switching frequency have been shown.

### 2 Introduction

In the last couple of years the design cycle duration of SMPS in electronic applications becomes more and more important. Many applications need well controlled voltage containing features like low power dissipation for standby mode and a high efficiency during normal mode. These features make great demands on the power supply itself which can be satisfied by SMPS, like it is done actually for instance in most PC, charger or TV-set. Due to this wide range of applications the requirements for the SMPS cover a extensive array of features.

Some applications require one output voltage of the SMPS, others need more than one, some SMPS have a higher output voltage than the input voltage, others vice versa. One of the most important parameter for the selection of SMPS is the output power. To have a solution for each of the different applications, different topologies have been developed to achieve an optimum cost/performance ratio.

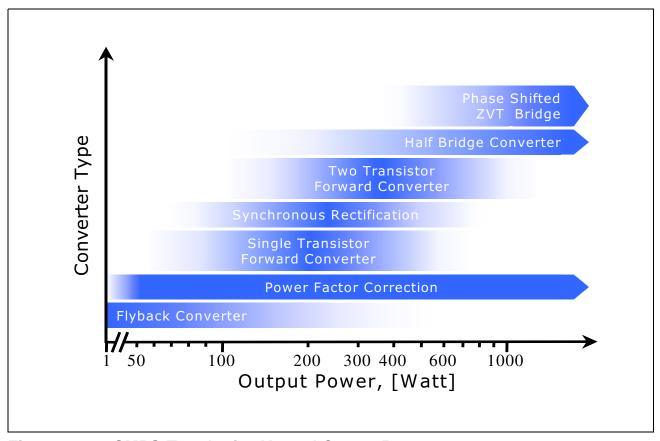

Figure 1 shows the most popular topologies for different output power classes.

Application Note 4 V1.2, 2002-01

Introduction

Figure 1 SMPS-Topologies Versed Output Power

The topologies mentioned in **Figure 1** can be operated in continuous conduction mode and in discontinuous conduction mode. The main difference between these both families are the shape of the current. Discontinuous conduction mode has a triangular shaped current, whereas for the continuous conduction mode a trapezoid shaped current is typical.

These topologies lead to different requirements for the MOSFETs, like

- packages

- drain-source voltage rating

- drain current rating

- on state resistance.

**Selecting the Package**

#### **Selecting the Package** 3

The selection of the MOSFET package mainly depends on following parameters.

cooling

Power dissipation/ Power losses of the MOSFET has a great impact on selection of the

package.

SMD packages can be used for lower power dissipation: DPAK for approximately 0.5 W (depending on pad size) D2PAK for approximately 1 W (depending on pad size)

The through hole packages like TO-220 and especially TO-247 with attached heat sink and forced cooling can dissipate much more

power.

Creepage distance

The creepage distance between legs of the package should correspond to the voltage requirements in the given application

field.

Space/volume The size of the package can be also influence by the available

> space/volume/height in a given case of SMPS/lamp ballast. For examples, notebook adapters use I2Pak in order to reduce the

height of the device.

Cost Smaller packages are usually less expensive, than the bigger ones.

> Also SMD mounting technology can be more cost-effective during the manufacturing process. Fully isolated package helps to reduce the cost of heat sink assembly by skipping the manufacturing step

of putting the isolation pad between package and heat sink.

#### 4 **How to Choose the Voltage Rating of the MOSFET?**

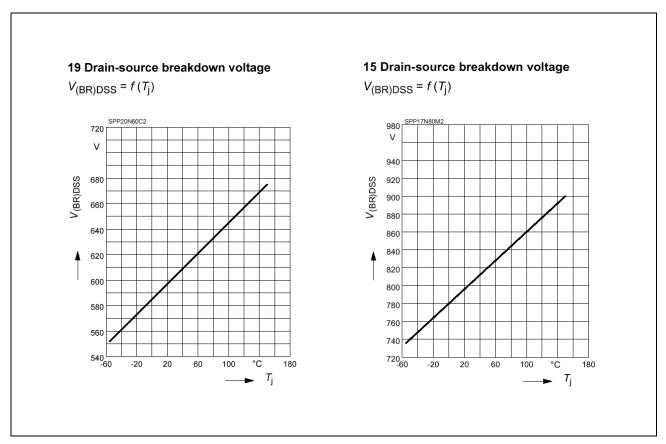

The avalanche breakdown voltage of CoolMOS is slightly higher than it's voltage rating due to typical safety margin. The voltage rating is defined at room temperature. Breakdown voltage of CoolMOS has strong positive temperature coefficient as it can be seen in Figure 2.

**Application Note** 6 V1.2, 2002-01

### **How to Choose the Voltage Rating of the MOSFET?**

Figure 2 Dependence of the Breakdown Voltage on the Junction Temperature of 600 V CoolMOS and 800 V CoolMOS

Breakdown voltage at typical operation temperature of 100 - 120°C is approx. 7% higher than rated voltage.

Reliability tests are done at rated voltage, especially the HTRB (High Temperature Reversed Bias). These test results are used as input information for calculation of acceleration factors in different reliability models. In order to achieve high forecasted reliability the maximum operating voltage should be lower than the one used in HTRB.

Another criteria for selecting the voltage rating of the MOSFET are the overvoltage spikes. During turn off transient the voltage on the drain can reach much higher values as in steady state due to parasitic inductances in the circuit.

All these criteria should be considered during the selection of the MOSFET voltage rating. The maxi-mum steady state voltage during turn off should not exceed 70 to 90% of the rated voltage. These derating values has been achieved by the years of experience.

Application Note 7 V1.2, 2002-01

**How to Select the Operating Junction Temperature?**

### 5 How to Select the Operating Junction Temperature?

Similar reliability rules can be applied for the selection of operating junction temperature of the MOSFET. The operating junction temperature should not exceed the maximum value specified in the datasheet. Pushing the operating temperature to the maximum is not reasonable. The majority of reliability test are done at maximum junction temperature, especially the HTRB (High Temperature Reversed Bias) and HTGS (High Temperature Gate Source). These test results are used as input information for calculation of acceleration factors in different reliability models. In order to achieve high forecasted reliability the maximum operating temperature should be lower than the maximum one. For example, reducing the junction temperature by 30°C will improve the MTBF (Mean Time Between Failure) of the CoolMOS by an order of magnitude.

On the other hand, the on-state resistance of the MOSFET increases with the junction temperature. It leads to increase in conduction power losses.

For these reasons the derating factors of 70-90% of the maximum junction temperature are recommended.

### 6 How to Choose the Current Rating of the MOSFET?

In the majority of SMPS applications the MOSFET is not being stressed up to it's maximum current rating due to poor cooling conditions. Designer prefers to take an advantage of low on-state resistance of the MOSFET in order to reduce the power losses. Usually MOSFETs with selected low  $R_{\rm ds(on)}$  have higher current rating then needed in the application. Nevertheless, it is useful to check the Safe Operating Area of the selected MOSFET.

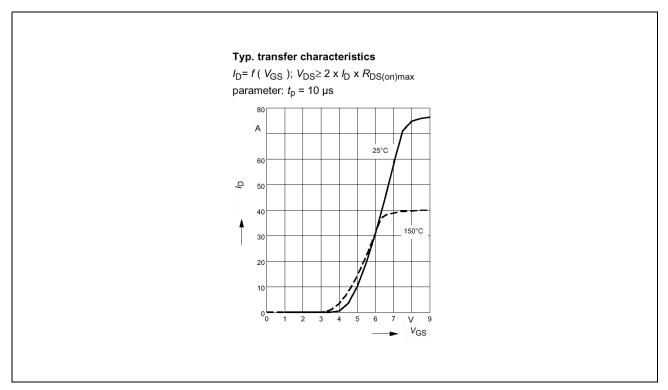

On the other hand, gate-source voltage should be high enough to completely turn on the MOSFET. The transistor should be able to carry the maximum pulse current in converter under all conditions. Especially during start up or short circuit on the output of SMPS the supply voltage for the control IC can fall close to under voltage lockout limit. Some modern control IC have the under voltage lock out of approximately 7 V. The gate-source voltage of MOSFET can be less than 5 V, if we consider the voltage drops on the output stage of the control IC and on the current sense resistor in source path of transistor. MOSFET should be able to carry the required current without increase of drain-source voltage at given gate-source voltage. The transfer characteristic from the datasheet can be used in order to prove it Figure 3. If the MOSFET does not meet the requirements, another transistor with higher current rating should be selected.

Application Note 8 V1.2, 2002-01

How to Choose the Right  $R_{ds(on)}$ ?

Figure 3 Transfer Characteristic

### 7 How to Choose the Right $R_{ds(on)}$ ?

The most complicated selection is to choose the correct on state resistance of the device. The limit for the on state resistance is the maximum allowable power dissipation of the application and the maximum junction temperature of the MOSFET.

The power losses of the MOSFET can be divided into the conduction losses and the switching losses. The conduction losses are easy to calculate due to a constant on state resistance of the MOSFET and a well defined drain current.

Problems occur by calculating the switching losses of the MOSFET. These losses strongly depend on parasitic parameters of the circuit. This application note is based on measurements of the switching energy versed the drain current in a test setup, which means, that it is not one to one transferable to other applications due to different parasitics. Test setup of SMPS is still necessary for the designer, but with this application note it is possible to save iterations for the design process.

The intention of this application note is to relieve the development of a SMPS by selecting an optimum MOSFET fulfilling the requirements of the application. To achieve this the maximum allowable power dissipation of the application with consideration of heat sink, topology etc. is compared with power losses of the MOSFET itself.

### How to Choose the Right $R_{ds(on)}$ ?

Designing the SMPS is a complicated process that requires many iterations. One thing the designer knows for sure is the output power of the SMPS. In most case the choice of topology is also done. It is usually based on the output power and the output voltage level.

Next step might be to fix the switching frequency. This is the point where the problem starts. Let us assume that the switching frequency is fixed to some value, which corresponds to other design criteria like EMI noise or magnetic losses, but is not related to the power losses in the MOSFET.

We will also assume, that the space for heat sink is known. That means we can estimate the thermal resistance of the heat sink  $R_{thCA}$ .

### How to Choose the Right $R_{ds(on)}$ ?

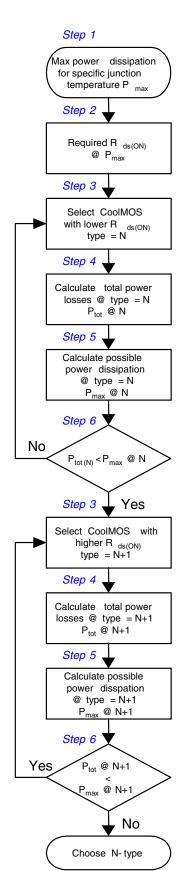

### Step 1: Calculate the maximum power dissipation for a specific junction temperature

First step would be to calculate how much power losses can be allowed for the defined heat sink and specific junction temperature.

## Step 2: Calculate the required $R_{\rm ds(ON)}$ satisfying the maximum power losses from Step 1

At this point we already know the value of the maximum allowable power dissipation. We also know the topology and the drain current waveform. By using the drain current waveform we can calculate the value of  $R_{\rm ds(ON)}$ , that will satisfy the maximum power losses. For the first iteration we will use only conduction power losses because we do not know the MOSFET type yet. The switching losses depend strongly on the particular MOSFET type. For this reason we will skip the switching losses for the first iteration, but we will check it in the following steps.

### Step 3: Select the CoolMOS type with $R_{\rm ds(ON)}$ defined in Step 2

In this step we will select the CoolMOS transistor type, that has the required on state resistance calculated in Step 2. Please note to use not a room temperature value, but a value at a higher junction tem-perature specific for particular design (usually between 110°C and 120°C). It should be double of a room temperature value.

## Step 4: Calculate the total power losses for the selected Cool-MOS type in Step 3

Now we have enough information to calculate the total power losses for the selected CoolMOS transistor under particular operating conditions. As we now know the exact transistor type, we are able to calculate the switching power losses for a given switching frequency.

## Step 5: Recalculate the maximum power dissipation for a selected CoolMOS type

With the available junction to case thermal resistance of the selected CoolMOS device it is possible to make the calculation of maximum allowable power dissipation more precisely. This step can help to skip one of the iteration what will be explained in Step 6.

# Step 6: Compare the total power losses calculated in Step 4 for the selected CoolMOS type with maximum allowable power dissipation from Step 5

At this point it is necessary to compare the total power losses calculated in Step 4 with the maximum allowable power dissipation resulting from the defined junction temperature and heat sink (Step 5).

If the total power losses from Step 4 are lower than the maximum allowable power dissipation (Step 1), then the selected CoolMOS type meets the requirements. We did find the right type.

As a further optimization it could be possible to check if the next CoolMOS type with higher  $R_{\rm ds(ON)}$  will do the same job. Repeat Steps 4, 5 and 6 with this new selection.

In case of total power losses from Step 4 are higher than the maxi-mum allowable power dissipation (Step 1), select the next type from the CoolMOS family with lower on state resistance and repeat the Steps 4, 5 and 6. Another possibility would be to adjust the heat sink.

The right type is found, when the next CoolMOS with higher  $R_{\rm ds(ON)}$  does not meet the requirements.

### **How to Calculate the Maximum Power Losses for a Specific**

## Step 1 Calculate the maximum power dissipation for a specific junction temperature

First step would be to calculate how much power losses can be allowed for the defined heat sink and specific junction temperature.

### 8 How to Calculate the Maximum Power Losses for a Specific Junction Temperature?

This section explains how to calculate the maximum allowable power dissipation in the CoolMOS for a specific junction temperature using the datasheet parameters.

### Input information:

$T_{\mathsf{J}(\mathsf{max})}$  - maximum junction temperature

$T_{A}$  - ambient temperature

$R_{\rm thJC}$  - assumed thermal resistance junction to case for the specific device

$R_{\text{thCA}}$  - thermal resistance case to ambient

### Solution:

The actual junction temperature:

$$T_J = \left[ P_{max} \cdot \left( R_{thJC} + R_{thCA} \right) \right] + T_A$$

[1]

then the maximum allowable power dissipation:

$$P_{tot} = \frac{T_{J(max)} - T_A}{R_{thJC} + R_{thCA}}$$

[2]

### **Example for Step 1:**

We assume that the thermal resistance of the heat sink is

$$R_{\text{thCA}} = 40 \text{ K/W}.$$

Actually we have to consider the thermal resistance junction to case of the MOSFET also, but we did not select the MOSFET type yet. Let us assume some value for the thermal resistance of MOSFET just for the first iteration. Let us say it will be the value of second smallest CoolMOS device with a thermal resistance of 5 K/W:

Application Note 12 V1.2, 2002-01

#### **How to Calculate the Power Losses?**

$R_{\rm thJC} = 5 \text{ K/W}.$

The maximum allowed junction temperature in our case will be very conservative value:

$$T_{\rm J} = 110^{\circ}{\rm C}.$$

The ambient temperature is:

$$T_{\rm A} = 70^{\circ}{\rm C}$$

Now using the equation 2 we can calculate the maximum allowable power dissipation in our case:

$$P_{max} = \frac{T_{J} - T_{A}}{R_{thJC} + R_{thCA}} = \frac{110 \text{ }^{\circ}C - 70 \text{ }^{\circ}C}{5 \frac{K}{W} + 40 \frac{K}{W}} = 0.889 \text{ } W$$

# Step 2 Calculate the required $R_{\rm ds(ON)}$ satisfying the maximum power losses from Step 1

At this point we already know the value of the maximum allowable power dissipation. We also know the topology and the drain current waveform. Using the drain current waveform we can calculate the value of  $R_{\rm ds(on)}$ , that will satisfy the maximum power losses. For the first iteration we will use only conduction power losses because we did not know the MOSFET type yet. The switching losses depend strongly on the particular MOSFET type. For this reason we will skip the switching losses for the first iteration, but we will check it in the following steps.

### 9 How to Calculate the Power Losses?

This section demonstrates how to calculate the power losses in the CoolMOS from the actual circuit using the datasheet parameters.

### 10 Conduction Losses

#### Input information:

D - duty cycle

$t_{\rm on}$  - turn on time

*f* - switching frequency

$V_{\text{in(dc)}}$  - input DC voltage

$R_{\rm ds(ON)}$  - drain to source on-state resistance

Application Note 13 V1.2, 2002-01

**Conduction Losses**

#### Solution:

Conduction energy losses can be obtained by

$$E_{cond} = \int_{0}^{t} on v_{ds}(t) \cdot i_{d}(t) dt = \int_{0}^{t} on R_{ds(ON)} \cdot i_{d}(t)^{2} dt$$

[3]

where,  $v_{ds}(t)$  is the on-state voltage drop and  $i_{d}(t)$  is the drain current waveform after turn on. Then conduction power losses:

$$P_{cond} = E_{cond} \cdot f$$

[4]

The turn on resistance of a MOSFET depends on its junction temperature. The on-state resistance at defined junction temperature can be calculated as:

$$R_{ds(ON)} \left(T_{J}\right) = R_{ds(ON)} (25 \text{ °C}) \cdot \left(1 + \frac{\alpha}{100}\right)^{T_{J} - 25 \text{ °C}}$$

The temperature factor a is for all CoolMOS transistors 0.8.

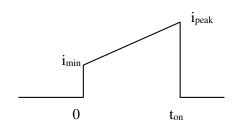

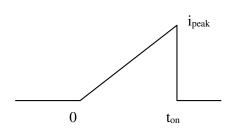

### 10.1 Discontinuous Conduction Mode Converter

The drain current waveform:

i<sub>peak</sub>

0

ton

Mathematical expression:

$$i_d = i_{peak} \cdot \frac{t}{t_{on}}$$

$$E_{cond} = \int_{0}^{t} on v_{ds}(t) \cdot i_{d}(t) dt = \int_{0}^{t} on R_{ds(ON)} \cdot i_{d}(t)^{2} dt = \frac{1}{3} \cdot R_{ds(ON)} \cdot i_{peak}^{2} \cdot t_{on}$$

[5]

$$P_{cond} = E_{cond} \cdot f = \frac{1}{3} \cdot R_{ds(ON)} \cdot i_{peak}^{2} \cdot D$$

[6]

**Conduction Losses**

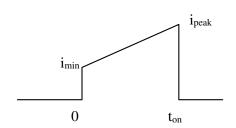

### 10.2 Continuous Conduction Mode Converter

The drain current waveform:

Mathematical expression:

$$i_{d} = i_{\min} + \frac{i_{peak} - i_{\min}}{t_{on}} \cdot t$$

In order to simplify the equations we will assume, that:

$$i_{min} = K_{min} \cdot i_{peak}$$

This means that the minimum drain current is a fixed percentage of the peak drain current.

$$E_{cond} = \int_{0}^{t_{on}} R_{ds(ON)} \cdot i_{d}(t)^{2} dt = \frac{1}{3} \cdot \left( i_{min}^{2} + i_{peak} \cdot i_{min} + i_{peak}^{2} \right) \cdot R_{ds(ON)} \cdot t_{on}$$

[7]

$$P_{cond} = E_{cond} \cdot f = \frac{1}{3} \cdot R_{ds(ON)} \cdot D \cdot \left( i_{min}^2 + i_{peak} \cdot i_{min} + i_{peak}^2 \right)$$

[8]

### Example for Step 2 (discontinuous conduction mode converter):

We can find how to calculate the  $R_{ds(ON)}$  using equation 6:

$$R_{ds(ON)} = \frac{3 \cdot P_{cond}}{i_{peak}^{2} \cdot D}$$

In our design we will use the following operating parameters:

$i_{peak} = 2.4 \text{ A (peak drain current)},$

D = 0.21 (duty cycle).

From the example for Step 1 we have

$P_{\text{max}} = 0.889 \text{ W}.$

Now we can calculate the required on state resistance at  $T_J = 110$ °C:

$$R_{ds(ON)} = \frac{3 \cdot P_{cond}}{i_{peak}^{2} \cdot D} = \frac{3 \cdot 0.889 \text{ W}}{(2.4 \text{ A})^{2} \cdot 0.21} = 2.205 \Omega$$

#### **Conduction Losses**

As we can see the required on state resistance of CoolMOS for satisfying the maximum power dissipation is slightly above 2  $\Omega$ .

For a selection of required CoolMOS we need the on state resistance at a junction temperature of 25°C.

$$R_{ds(ON)} (25 \text{ °C}) = \frac{R_{ds(on)} (T_J)}{\left(1 + \frac{\alpha}{100}\right)^{T_J - 25 \text{ °C}}} = \frac{2.205 \Omega}{\left(1 + \frac{0.8}{100}\right)^{110 \text{ °C} - 25 \text{ °C}}} = 1.12 \Omega$$

For later calculations we will make the simplification, that on state resistance at 25°C is half of the resistance at junction temperature.

Using this information we can select a type from the CoolMOS family.

Application Note 16 V1.2, 2002-01

**Conduction Losses**

### Step 3 Select the CoolMOS type with $R_{ds(on)}$ defined in Step 2

In this step we will select the CoolMOS transistor type, that has the required on state resistance calculated in **Step 2**. Please note to use not a room temperature value, but the value at a higher junction temperature specific for particular design (usually between 110°C and 120°C). It is approximately double of a room temperature value. This selection based only on conduction losses. The switching losses were not considered in this first iteration.

### **Example for Step 3 (discontinuous conduction mode converter):**

From our previous calculation the required on state resistance is

$R_{\rm ds(on)}$  =1.12  $\Omega$

at  $T_{\rm J} = 25^{\circ}{\rm C}$ .

Let us take a look on the CoolMOS product family.

|                        | *                                                   | •                                      |                                                     | *                                      | **                                     | *                                         |                          | No.           |

|------------------------|-----------------------------------------------------|----------------------------------------|-----------------------------------------------------|----------------------------------------|----------------------------------------|-------------------------------------------|--------------------------|---------------|

|                        | SOT-223                                             | TO-252<br>(D-PAK)                      | TO-251<br>(I-PAK)                                   | TO-220 SMD<br>(D <sup>2</sup> -PAK)    | TO-220                                 | TO-220<br>FullPAK                         | TO-262<br>I²-PAK         | TO-247        |

| <b>6.0 Ω</b><br>0.8 A  | SPN01N60S5                                          | SPD01N60S5                             | SPU01N60S5                                          |                                        |                                        |                                           |                          |               |

| <b>3.0 Ω</b><br>1.9 A  | SPN02N60C3 <sup>1</sup><br>SPN02N60S5               | SPD02N60C3<br>SPD02N60S5               | SPU02N60C3 <sup>1</sup><br>SPU02N60S5               | SPB02N60C3<br>SPB02N60S5               | SPP02N60C3<br>SPP02N60S5               |                                           |                          |               |

| <b>1.4 Ω</b><br>3.2 A  | SPN03N60C3 <sup>1</sup><br>SPN03N60S5               | SPD03N60C3<br>SPD03N60S5               | SPU03N60C3 <sup>1</sup><br>SPU03N60S5               | SPB03N60C3<br>SPB03N60S5               | SPP03N60C3<br>SPP03N60S5               |                                           |                          |               |

| <b>0.95 Ω</b><br>4.5 A | SPN04N60C3 <sup>1</sup><br>SPN04N60C2<br>SPN04N60S5 | SPD04N60C3<br>SPD04N60C2<br>SPD04N60S5 | SPU04N60C3 <sup>1</sup><br>SPU04N60C2<br>SPU04N60S5 | SPB04N60C3<br>SPB04N60C2<br>SPB04N60S5 | SPP04N60C3<br>SPP04N60C2<br>SPP04N60S5 | SPA04N60C3<br>SPA04N60C2                  |                          |               |

| <b>0.6 Ω</b><br>7.3 A  | Best-in-Class                                       | SPD07N60C3<br>SPD07N60C2<br>SPD07N60S5 | SPU07N60C3 <sup>1</sup><br>SPU07N60C2<br>SPU07N60S5 | SPB07N60C3<br>SPB07N60C2<br>SPB07N60S5 | SPP07N60C3<br>SPP07N60C2<br>SPP07N60S5 | SPA07N60C3<br>SPA07N60C2                  | SPI07N60C3<br>SPI07N60S5 |               |

| <b>0.38 Ω</b><br>11 Α  |                                                     | Best-in-Class                          | Best-in-Class                                       | SPB11N60C3<br>SPB11N60C2<br>SPB11N60S5 | SPP11N60C3<br>SPP11N60C2<br>SPP11N60S5 | SPA11N60C3<br>SPA11N60C2                  | SPI11N60C3<br>SPI11N60S5 |               |

| <b>0.19 Ω</b><br>20 A  |                                                     |                                        |                                                     | SPB20N60C3<br>SPB20N60C2<br>SPB20N60S5 | SPP20N60C3<br>SPP20N60C2<br>SPP20N60S5 | SPA20N60C3<br>SPA20N60C2<br>Best-in-Class |                          |               |

| <b>0.07 Ω</b><br>47 A  | - 1                                                 |                                        |                                                     | Best-in-Class                          | Best-in-Class                          | Dear                                      |                          |               |

| 47 A                   | ¹available                                          | on request,                            | <sup>2</sup> available                              | in Q2 2002                             |                                        |                                           |                          | Best-in-Class |

Figure 4 600 V Product Family

The SPP04N60C3 seems to be a good choice.

**Switching Losses**

## Step 4 Calculate the total power losses for the selected CoolMOS type in Step 3

Now we have enough information to calculate the total power losses for the selected CoolMOS transistor under particular operating conditions. As we now know the exact transistor type, we are able to calculate the switching power losses for a given switching frequency.

### 11 Switching Losses

### Input information:

f - switching frequency

$V_{\rm ds(on)}$  - DC voltage between drain and source before the start of the turn-on transition

$V_{\rm ds(off)}$  - DC voltage between drain and source after the end of the turn-off transition

$R_{\text{gate}}$  - gate resistor

$E_{\rm on}$  - energy losses during turn-on transition

$E_{\rm off}$  - energy losses during turn-off transition

$R_{\text{gate(test)}}$  - gate resistance during measurement of  $E_{\text{on}}$  and  $E_{\text{off}}$

$V_{

m ds(test)}$  - drain to source voltage during measurement of  $E_{

m on}$  and  $E_{

m off}$

#### Solution:

Switching energy losses occur due to simultaneous presence of significant drain-source voltage and drain current during each transient from turn off state into turn on state and vice versa.

Turn on switching energy losses can be obtained by

$$E_{on} = \int_{0}^{\bullet t_{d(on)} + t_r} v_{ds}(t) \cdot i_{d}(t) dt$$

[9]

Turn off switching energy losses is expressed as

$$E_{off} = \int_{0}^{\bullet t_{d(off)} + t_f} v_{ds}(t) \cdot i_{d}(t) dt$$

[10]

**Switching Losses**

Total switching power losses are:

$$P_{sw} = (E_{on} + E_{off}) \cdot f \tag{11}$$

Next charts will demonstrate the parameters, which influence the switching behavior of MOSFET and correspondingly the values of switching energy losses. The information shown is based on the investigations of a usual boost converter driven in the double pulse measurement mode. Please note that the turn on transient strongly depends on the used commutated diode and not on the MOSFET itself in case of non-triangle current waveforms. The power losses are given mostly by the characteristics of the commutated diode.

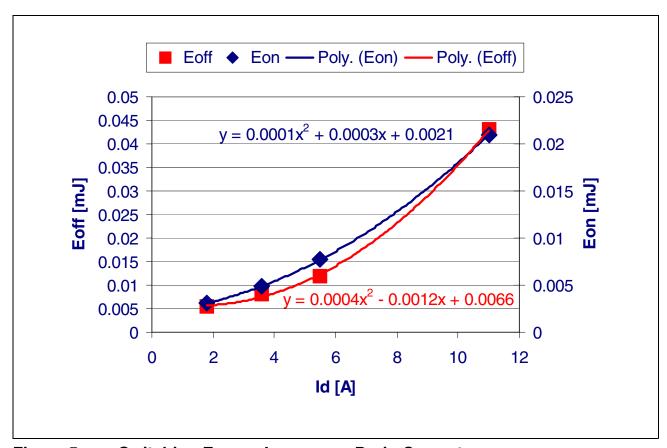

Both  $E_{\rm on}$  and  $E_{\rm off}$  strongly depend on the value of drain current **Figure 5**.  $E_{\rm on}$  losses are dominated by the used commutated diode, not by MOSFET. We should take the power losses value at the corresponding drain current value in particular case. The curve can be interpolated with a second order polynome in order to simplify the calculations.

Figure 5 Switching Energy Losses vs. Drain Current (SPP11N60C3, SDP06S60,  $R_{\text{gate}}$  = 6.8  $\Omega$ ,  $V_{\text{ds}}$  = 380 V,  $T_{\text{J}}$  = 125°C)

### **Switching Losses**

This information can be found in CoolMOS datasheets. It can be easily implemented directly into calculation.

$$E_{on}(i_d) = E_{on}(i_d)$$

[12]

$$E_{off}(i_d) = E_{off}(i_d)$$

[13]

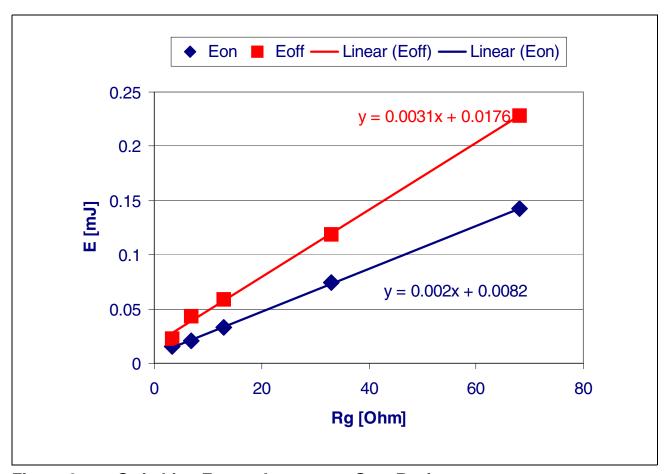

**Figure 6** demonstrates the switching energy losses versed external gate resistor. The recharging speed of CoolMOS capacitance can be controlled by  $R_{\text{gate}}$ . It influences the switching time, and correspondingly the switching losses. The curves are almost linear.

Figure 6 Switching Energy Losses vs. Gate Resistor (SPP11N60C3, SDP06S60,  $I_d$  = 11 A,  $V_{ds}$  = 380 V,  $T_J$  = 125°C)

### **Switching Losses**

The CoolMOS datasheet includes this chart. If your particular design does have another gate resistor as given in the datasheet you should implement a corrective factor into the equations of switching losses as following:

$$E_{on}(i_d, R_{gate}) = E_{on}(i_d) \cdot \frac{E_{on}(R_{gate})}{E_{on}(R_{gate(test)})} = E_{on}(i_d) \cdot CF_{on}(R_{gate})$$

[14]

$$E_{off}(i_d, R_{gate}) = E_{off}(i_d) \cdot \frac{E_{off}(R_{gate})}{E_{off}(R_{gate(test)})} = E_{off}(i_d) \cdot CF_{off}(R_{gate})$$

[15]

We include corrective factors to maintain the clarity for following calculations.

$$CF_{on}(R_{gate}) = \frac{E_{on}(R_{gate})}{E_{on}(R_{gate(test)})}$$

[16]

$$CF_{off}(R_{gate}) = \frac{E_{off}(R_{gate})}{E_{off}(R_{gate(test)})}$$

[17]

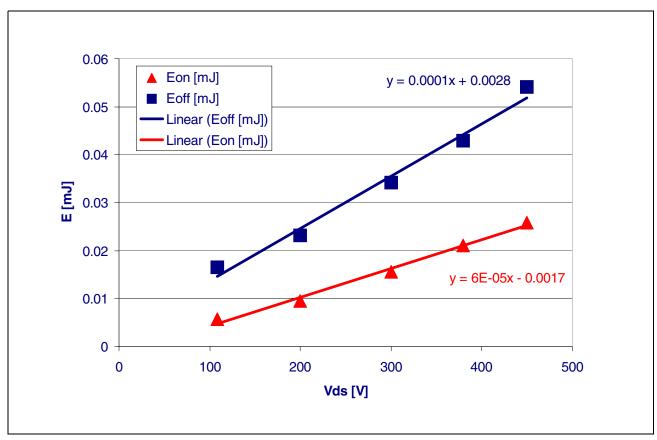

The drain to source voltage across the CoolMOS also has an effect on switching behavior. The dependence of switching losses on the drain-source voltage is almost linear **Figure 7**.

Application Note 21 V1.2, 2002-01

### **Switching Losses**

Figure 7 Switching Energy Losses vs. Drain-Source Voltage (SPP11N60C3, SDP06S60,  $I_d$  = 11 A,  $R_{gate}$  = 6.8  $\Omega$ ,  $T_J$  = 125°C)

This information is not included in the datasheet due to the linearity of this dependence. We are still able to calculate the corrective factor for the switching losses, if the particular design's voltage differs from the datasheet parameters:

$$E_{on}(i_d, V_{ds(on)}) = E_{on}(i_d) \cdot \frac{E_{on}(V_{ds(on)})}{E_{on}(V_{ds(on)})} = E_{on}(i_d) \cdot \frac{6 \cdot 10^{-5} \cdot \frac{mJ}{V} \cdot V_{ds(on)} - 1.7 \cdot 10^{-3} mJ}{0.021 \, mJ} = E_{on}(i_d) \cdot CF_{on}(V_{DS}(on))$$

[18]

$$E_{off}(i_d, V_{ds(off)}) = E_{off}(i_d) \cdot \frac{E_{off}(V_{ds(off)})}{E_{off}(V_{ds(test)})} = E_{off}(i_d) \cdot \frac{10^{-4} \cdot \frac{mJ}{V} \cdot V_{ds(off)} + 2.8 \cdot 10^{-3}}{0.043 \, mJ} = E_{off}(i_d) \cdot CF_{off}(V_{DS}(off))$$

[19]

**Switching Losses**

We include corrective factors to maintain the clarity for following calculations.

$$CF_{on}(V_{DS}(on)) = \frac{E_{on}(V_{ds(on)})}{E_{on}(V_{ds(test)})} = \frac{6 \cdot 10^{-5} \cdot \frac{mJ}{V} \cdot V_{ds(on)} - 1.7 \cdot 10^{-3} mJ}{0.021 \, mJ}$$

[20]

$$CF_{off}(V_{DS}(off)) = \frac{E_{off}(V_{ds(off)})}{E_{off}(V_{ds(test)})} = \frac{10^{-4} \cdot \frac{mJ}{V} \cdot V_{ds(off)} + 2.8 \cdot 10^{-3}}{0.043 \, mJ}$$

[21]

Summarizing the switching energy depends on the peak current, the drain to source voltage and the gate resistance. To calculate the switching energy, the charts of the datasheet are the basis plus the correction factors for gate resistance and drain to source voltage.

$$E_{on}(i_d, V_{ds(on)}, R_g) = E_{on}(i_d) \cdot \frac{E_{on}(V_{ds(on)})}{E_{on}(V_{ds(test)})} \cdot \frac{E_{on}(R_{gate})}{E_{on}(R_{gate(test)})} = E_{on}(i_d) \cdot CF_{on}(V_{DS}(on)) \cdot CF_{on}(R_{gate})$$

[22]

$$E_{off}(i_d, V_{ds(off)}, R_{gate}) = E_{off}(i_d) \cdot \frac{E_{off}(V_{ds(off)})}{E_{off}(V_{ds(test)})} \cdot \frac{E_{off}(R_{gate})}{E_{off}(R_{gate(test)})} = E_{off}(i_d) \cdot CF_{off}(V_{DS}(off)) \cdot CF_{off}(R_{gate})$$

[23]

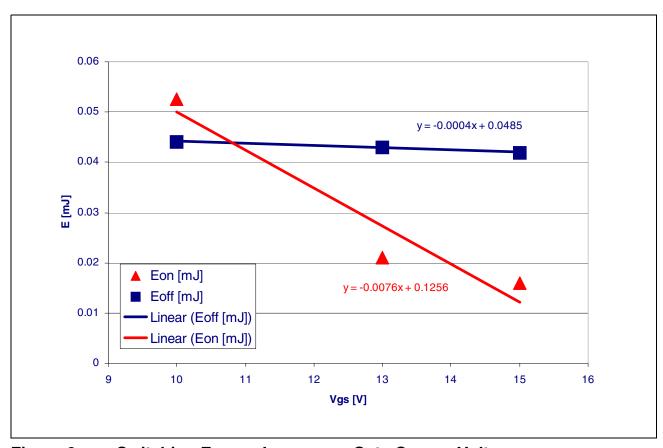

As it can be seen in **Figure 8**, the dependence of turn off energy losses on the gate-source voltage is negligibly low. Turn on behavior is dominated by the commutated diode, not by the CoolMOS. We will skip both dependencies in order to simplify the analysis.

### **Switching Losses**

Figure 8 Switching Energy Losses vs. Gate-Source Voltage (SPP11N60C3, SDP06S60,  $I_{\rm d}$  = 11 A,  $R_{\rm gate}$  = 6.8  $\Omega$ ,  $V_{\rm ds}$  = 380 V,  $T_{\rm J}$  = 125°C)

**Switching Losses**

### 11.1 Discontinuous Conduction Mode Converter

The drain current waveform:

Mathematical expression:

$$i_d = i_{peak} \cdot \frac{t}{t_{on}}$$

Turn-on energy losses is negligible:

$$E_{on} = 0 ag{24}$$

Turn-off energy losses

$$E_{off}(i_{peak}, V_{ds(off)}, R_g) = E_{off}(i_{peak}) \cdot CF_{off}(V_{DS}(off)) \cdot CF_{off}(R_{gate})$$

[25]

Since the switching energy is proportional to  $V_{\rm ds}$  and  $R_{\rm g}$ , the result is scaled by the ratio of the actual circuit voltage and gate resistance to the test voltage and the test gate resistance in the datasheet.

Total switching power losses:

$$P_{sw} = (E_{on} + E_{off}) \cdot f = E_{off}(i_{peak}) \cdot CF_{off}(V_{DS}(off)) \cdot CF_{off}(R_{gate}) \cdot f$$

[26]

**Total Power Losses**

### 11.2 Continuous and Discontinuous Conduction Mode Converter

The drain current waveform:

Mathematical expression:

$$i_d = i_{\min} + \frac{i_{peak} - i_{\min}}{t_{on}} \cdot t$$

In order to simplify the equations we will assume, that:

$$i_{min} = K_{min} \cdot i_{peak}$$

This means that the minimum drain current is a fixed percentage of the peak drain current.

Turn-on energy losses:

$$E_{on}(i_{min}, V_{ds(on)}, R_g) = E_{on}(i_{min}) \cdot CF_{on}(V_{DS}(on)) \cdot CF_{on}(R_{gate})$$

[27]

Since the switching energy is proportional to voltage, the result is scaled by the ratio of the actual circuit voltage to the test voltage in the datasheet.

Turn-off energy losses:

$$E_{off}(i_{peak}, V_{ds(off)}, R_{gate}) = E_{off}(i_{peak}) \cdot CF_{off}(V_{DS}(off)) \cdot CF_{off}(R_{gate})$$

[28]

Since the switching energy is proportional to voltage, the result is scaled by the ratio of the actual circuit voltage to the test voltage in the datasheet.

Total switching power losses:

$$P_{sw} = (E_{on} + E_{off}) \cdot f = \begin{bmatrix} (E_{on}(i_{min}) \cdot CF_{on}(V_{DS}(on)) \cdot CF_{on}(R_{gate})) \dots \\ + (E_{off}(i_{peak}) \cdot CF_{off}(V_{DS}(off)) \cdot CF_{off}(R_{gate})) \end{bmatrix} \cdot f$$

[29]

### 12 Total Power Losses

Total power losses for periodical signal can be calculated as the sum of conduction losses and switching losses:

$$P_{tot} = P_{cond} + P_{sw}$$

[30]

**Total Power Losses**

### 12.1 Discontinuous Conduction Mode Converter

$$P_{tot} = \frac{1}{3} \cdot R_{ds(ON)} \cdot i_{peak}^{2} \cdot D + E_{off}(i_{peak}) \cdot CF_{off}(V_{DS}(off)) \cdot CF_{off}(R_{gate}) \cdot f$$

[31]

#### 12.2 Continuos Current Mode Converter

$$P_{tot} = \frac{1}{3} \cdot R_{ds(ON)} \cdot D \cdot \left(i_{min}^{2} + i_{peak} \cdot i_{min} + i_{peak}^{2}\right) \dots + \left[\left(E_{on}(i_{min}) \cdot CF_{on}(V_{DS}(on)) \cdot CF_{on}(R_{gate})\right) + E_{off}(i_{peak}) \cdot CF_{off}(V_{DS}(off)) \cdot CF_{off}(R_{gate})\right] \cdot f$$

[32]

### Example for Step 4 (discontinuous conduction mode converter):

Our discontinuous conduction mode converter has following operating conditions:

$i_{\text{peak}} = 2.4 \text{ A (peak drain current)},$

D = 0.21 (duty cycle),

f = 60 kHz (switching frequency),

$R_{\text{gate}} = 12 \Omega \text{ (gate resistance)}$

$V_{\rm ds(on)}$  = 380 V (DC voltage between drain and source before the start of the turn-on transition, the bulk capacitor voltage),

$V_{\rm ds(off)}$  = 480 V (DC voltage between drain and source after the end of the turn-off transition, the bulk capacitor voltage plus the flyback voltage).

The selected CoolMOS SPP04N60C3 in **Step 3** has approximately 1.9  $\Omega$  on state resistance at junction temperature of 110°C:  $R_{\rm ds(ON)} = 1.9 \Omega$ . The turn off energy losses are  $E_{\rm off}$  ( $i_{\rm peak}$ ) = 6  $\mu$ J at  $i_{\rm peak}$  = 2.4 A and  $R_{\rm gate}$  = 18  $\Omega$ , this information can be found in the datasheet of CoolMOS.

Due to the dependence of switching energy to drain source voltage and gate resistance, this energy must be calculated for the particular conditions of SMPS. With the charts given in **Figure 6** and **Figure 7** this calculation can be easily made. The results of this calculation are valid for an 11 A device but to calculate the switching losses for our example you have to use the ratio between the energies of SMPS and the energies determined in the test circuit. This ratio is the same for all CoolMOS devices.

$$CF_{off} \left( V_{ds}(off) \right) = \frac{10^{-4} \cdot \frac{mJ}{V} \cdot V_{ds(off)} + 2.8 \cdot 10^{-3}}{0.043 \, mJ} = \frac{10^{-4} \cdot \frac{mJ}{V} \cdot 480 \, V + 2.8 \cdot 10^{-3}}{0.043 \, mJ} = 1.181$$

$$CF_{off}(R_{gate}) = \frac{E_{off}(R_{gate})}{E_{off}(R_{gate(test)})} = \frac{E_{off}(12\Omega)}{E_{off}(18\Omega)} = \frac{4.9uJ}{6.7uJ} = 0.731$$

**Total Power Losses**

Using this information we can calculate the total power losses:

$$P_{tot} = \frac{1}{3} \cdot 1.9 \Omega \cdot (2.4A)^2 \cdot 0.21 + 6uJ \cdot 1.181 \cdot 0.731 \cdot 60 \cdot kHz = 1.077 W$$

Now we know the total power losses of SPP04N60C3 in this particular design.

# Step 5 Recalculate the maximum power dissipation for a selected CoolMOS type

With the available junction to case thermal resistance of selected CoolMOS device it is possible to make the calculation of maximum allowable power dissipation more precisely. This step can help to skip one of the iterations what will be explained in Step 6.

### **Example for Step 5:**

The thermal resistance of the heat sink including the isolation material remains the same  $R_{\text{thCA}} = 40 \text{ K/W}$ .

The thermal resistance junction to case of the SPP04N60C3 is:

$$R_{\rm th,IC} = 2.5 \, \text{K/W}.$$

The maximum allowed junction temperature in our case is:

$$T_{.1} = 110^{\circ}$$

C.

The ambient temperature is:

$$T_{\rm A} = 70^{\circ}{\rm C}$$

Now using the **Equation [2]** we can calculate the maximum allowable power dissipation in our case more precise:

$$P_{max} = \frac{T_{J} - T_{A}}{R_{thJC} + R_{thCA}} = \frac{110 \text{ }^{\circ}C - 70 \text{ }^{\circ}C}{2.5 \frac{K}{W} + 40 \frac{K}{W}} = 0.941 \text{ W}$$

As we can see the maximum allowable power dissipation for SPP04N60C3 is 0.941 W.

**Total Power Losses**

# Step 6 Compare the total power losses calculated in Step 4 for a selected CoolMOS type with maximum allowable power dissipation from Step 5

At this point it is necessary to compare the total power losses calculated in step 4 with the maxi-mum allowable power dissipation resulting from the defined junction temperature and heat sink (Step 5).

If the total power losses from step 4 are lower than the maximum allowable power dissipation (**Step 1**), then the selected CoolMOS type meets the requirements. We did find the right type. As a further optimization it could be possible to check if the next CoolMOS type with higher  $R_{\rm ds(ON)}$  will do the same job. Repeat **Step 4**, **Step 5** and **Step 6** with this new selection.

In case of total power losses from **Step 4** are higher than the maximum allowable power dissipation (**Step 1**), select the next type from the CoolMOS family with lower on state resistance and repeat the **Step 4**, **Step 5** and **Step 6**. Another possibility would be to adjust the heat sink.

The right type is found, when the next CoolMOS with higher  $R_{ds(ON)}$  does not meet the requirements.

### **Example for Step 6 (discontinuous conduction mode converter):**

As we calculated in **Step 4** the SPP04N60C3 has total power losses of 1.077 W in this particular design. The maximum allowable power dissipation from **Step 5** is 0.941 W. This means the SPP04N60C3 does not meet the requirements of this particular design. Now we have two possibilities -selecting the next CoolMOS with lower on state resistance or adjusting the heat sink.

Example for CoolMOS type with lower  $R_{\rm ds(ON)}$  (discontinuous conduction mode converter):

Let us first select the next CoolMOS with lower  $R_{ds(ON)}$  and repeat the **Step 4**, **Step 5** and **Step 6**.

### Step 3 (second iteration):

We choose SPP07N60C3.

#### Step 4 (second iteration):

Our discontinuous conduction mode converter has following operating conditions:

$i_{\text{peak}} = 2.4 \text{ A (peak drain current)}$

D = 0.21 (duty cycle)

f = 60 kHz (switching frequency)

$R_{\text{qate}}$ =12  $\Omega$  (gate resistance)

#### **Total Power Losses**

$V_{\rm ds(on)}$  = 380 V (DC voltage between drain and source before the start of the turn-on transition, the bulk capacitor voltage)

$V_{\rm ds(off)}$  = 480 V (DC voltage between drain and source after the end of the turn-off transition, the bulk capacitor voltage plus the flyback voltage)

The CoolMOS SPP07N60C3 selected in **Step 3** has approximately 1.2  $\Omega$  on state resistance at junction temperature of 110°C:  $R_{\rm ds(ON)}=1.2~\Omega$ . The turn off energy losses is  $E_{\rm off}(i_{\rm peak})=7~\mu{\rm J}$  at  $i_{\rm peak}=2.4~{\rm A}$  and  $R_{\rm gate}=12~\Omega$ , this information can be found in the datasheet of CoolMOS.

The dependency of switching energy versed drain source voltage and gate resistance must be calculated with the formulas [17] and [21] for both correction factors. The correction factor for the gate resistance is 1, due to the condition of same used  $R_{\rm gate}$  for the test and for this particular SMPS.

Using all this information we can calculate the total power losses:

$$P_{tot} = \frac{1}{3} \cdot 1.2 \,\Omega \cdot (2.4 \,A)^2 \cdot 0.21 + 7uJ \cdot 1.181 \cdot 60 \,kHz = 0.98 \,W$$

### Step 5 (second iteration):

The thermal resistance of the heat sink including the isolation material remains the same  $R_{\text{thCA}} = 40 \text{ K/W}$ .

The thermal resistance junction to case of the SPP07N60C3 is:

$$R_{\rm th,IC} = 1.5 \text{ K/W}.$$

The maximum allowed junction temperature in our case is:

$$T_{.1} = 110^{\circ}$$

C.

The ambient temperature is:

$$T_{\rm A} = 70^{\circ}{\rm C}$$

Now using the **Equation [2]** we can calculate the maximum allowable power dissipation in this case more precise:

$$P_{max} = \frac{T_{J} - T_{A}}{R_{thJC} + R_{thCA}} = \frac{110 \text{ }^{\circ}C - 70 \text{ }^{\circ}C}{1.5 \frac{K}{W} + 40 \frac{K}{W}} = 0.964 \text{ } W$$

### Step 6 (second iteration):

As we can see, the total power losses from **Step 4** are higher than the maximum allowable power dissipation (**Step 5**). The SPP07N60C3 is still not the right choice.

#### **Calculation of Peak Pulse Current**

Let us now try another possibility. We will keep the SPP07N60C3, but we will slightly improve the thermal resistance of our heat sink by 3 K/W. Now we can calculate the maximum allowable power dissipation for this new heat sink (Step 5).

### **Step 5 (third iteration):**

The thermal resistance of the heat sink including the isolation material is  $R_{\text{thCA}} = 37 \text{ K/W}.$

All other parameters will remain the same.

$$P_{max} = \frac{T_J - T_A}{R_{thJC} + R_{thCA}} = \frac{110 \text{ }^{\circ}C - 70 \text{ }^{\circ}C}{1.5 \frac{K}{W} + 37 \frac{K}{W}} = 1.039 \text{ } W$$

### **Step 6 (third iteration):**

Let us compare the total power losses from **Step 4** (second iteration) and the maximum allowable power dissipation calculated in **Step 5** (third iteration). At this point we did achieve an optimum between selected CoolMOS type and adjusted heat sink. The selection of MOSFET is done.

### 13 Calculation of Peak Pulse Current

As shown in the previous section, the selection of the right MOSFET type is a complicated approach, which requires many iterations. In order to reduce the number of iterations, it is useful to select the optimal CoolMOS type for the first iteration. This section shows how to calculate the peak pulse current for the particular CoolMOS type and presents useful charts for preselection.

Combining the **Equation** [2] and [25], the information about the peak pulse current can be obtained.

#### 13.1 Discontinuous Conduction Mode Converter

From the condition that the total power losses should be lower than the maximum allowable power dissipation:

$$P_{tot} \leq P_{max}$$

[33]

and correspondingly:

$$\frac{1}{3} \cdot R_{ds(ON)} \cdot i_{peak}^{2} \cdot D + E_{off}(i_{peak}) \cdot CF_{off}(V_{DS}(off)) \cdot CF_{off}(R_{gate}) \cdot f \le \frac{T_{J} - T_{A}}{R_{thJC} + R_{thCA}}$$

[34]

Application Note 31 V1.2, 2002-01

#### **Calculation of Peak Pulse Current**

The relation between peak current and switching frequency can be expressed as:

$$f \leq \frac{T_{J} - T_{A}}{R_{thJC} + R_{thCA}} - \frac{1}{3} \cdot R_{ds(ON)} \cdot i_{peak}^{2} \cdot D$$

$$CF_{off}(V_{DS}(off)) \cdot CF_{off}(R_{gate}) \cdot E_{off}(i_{peak})$$

[35]

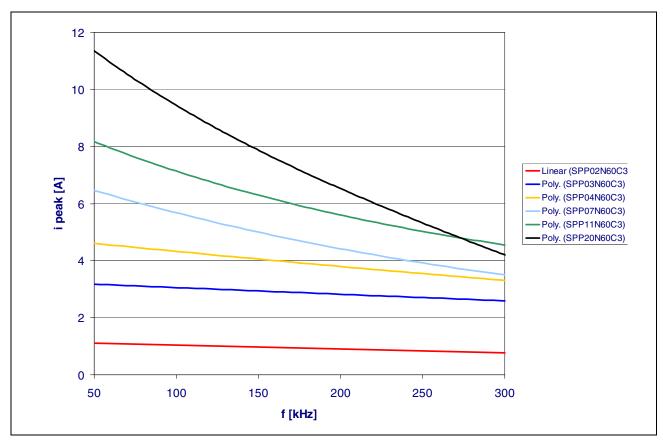

Now let us calculate what peak current can be handled by each particular CoolMOS C3 type, depending on the switching frequency. Due to the complexity of the equations and dependencies we will use the numeric solution. Next figure shows the peak drain current in a discontinuous conduction mode converter with following operating conditions:

D = 0.21 duty cycle  $V_{dc(in)} = 380 \text{ V}$  bulk capacitor voltage  $V_r = 100 \text{ V}$  reflected voltage  $T_J = 110^{\circ}\text{C}$  junction - temperature  $T_A = 70^{\circ}\text{C}$  ambient - temperature  $\eta = 0.8$  efficiency

Figure 9 Peak Current Handling Capability in Discontinuous Conduction Mode Converter (external heat sink thermal resistance is 10 K/W)

Application Note 32 V1.2, 2002-01

#### **Calculation of Peak Pulse Current**

### 13.2 Continuous Conduction Mode Converter

From the condition that the total power losses should be lower than the maximum allowable power dissipation

$$P_{tot} \leq P_{max}$$

[36]

and correspondingly:

$$\frac{1}{3} \cdot R_{ds(ON)} \cdot D \cdot \left(i_{min}^{2} + i_{peak} \cdot i_{min} + i_{peak}^{2}\right) \dots \leq \frac{T_{J} - T_{A}}{R_{thJC} + R_{thCA}} + \left(E_{on}\left(i_{min}\right) \cdot CF_{on}\left(V_{DS}(on)\right) \cdot CF_{on}\left(R_{gate}\right) + E_{off}\left(i_{peak}\right) \cdot CF_{off}\left(V_{DS}(off)\right) \cdot CF_{off}\left(R_{gate}\right)\right) \cdot f$$

$$= \frac{1}{3} \cdot R_{ds(ON)} \cdot D \cdot \left(i_{min}^{2} + i_{peak} \cdot i_{min} + i_{peak}^{2}\right) \dots \left(E_{on}^{2}\left(i_{peak}\right) \cdot CF_{off}\left(V_{DS}(off)\right) \cdot CF_{off}\left(R_{gate}\right)\right) \cdot f$$

$$f \leq \frac{\left[\frac{T_{J} - T_{A}}{R_{thJC} + R_{thCA}} - \frac{1}{3} \cdot R_{ds(ON)} \cdot D \cdot \left(i_{min}^{2} + i_{peak} \cdot i_{min} + i_{peak}^{2}\right)\right]}{E_{on}(i_{min}) \cdot CF_{on}(V_{DS}(on)) \cdot CF_{on}(R_{gate}) + E_{off}(i_{peak}) \cdot CF_{on}(V_{DS}(on)) \cdot CF_{on}(R_{gate})}$$

[38]

$$K_{min} = \frac{i_{min}}{i_{peak}}$$

[39]

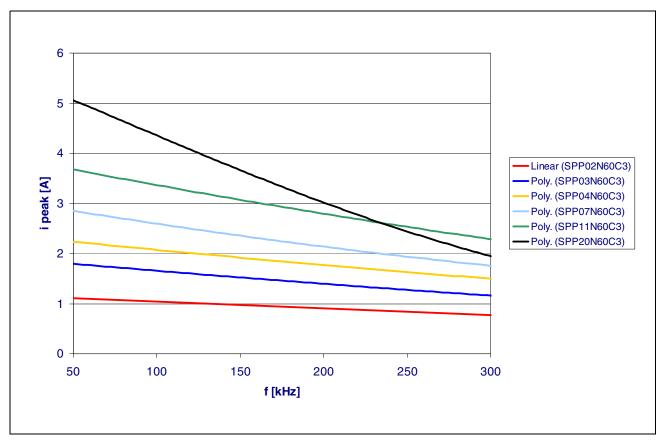

Now let us calculate what peak current can be handled by each particular CoolMOS C3 type depending on the switching frequency.

Due to the complexity of the equations and dependencies the numeric solution has being used. Next figure shows the peak drain current in a continuous conduction mode converter with following operating conditions:

$\begin{array}{lll} \text{D} = 0.45 & \text{duty cycle} \\ V_{\text{dc(in)}} = 380 \text{ V} & \text{bulk capacitor voltage} \\ T_{\text{J}} = 110^{\circ}\text{C} & \text{junction - temperature} \\ T_{\text{A}} = 70^{\circ}\text{C} & \text{ambient - temperature} \\ \eta = 0.8 & \text{efficiency} \\ K_{\text{min}} = 0.72 & \text{factor } I_{\text{min}}, I_{\text{max}} \end{array}$

Application Note 33 V1.2, 2002-01

### **Maximum Output Power Capability**

Figure 10 Peak Current Handling Capability in Continuous Conduction Mode Converter (external heat sink thermal resistance is 10 K/W)

### 14 Maximum Output Power Capability

#### 14.1 Discontinuous Conduction Mode Converter

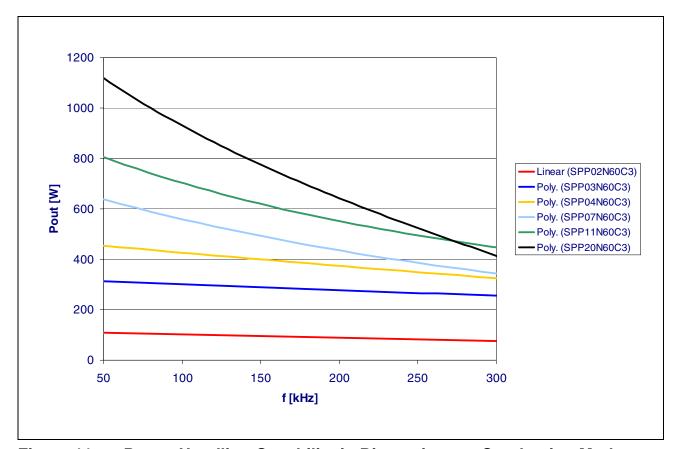

To make a first selection, which CoolMOS is best for a particular application, it is more interesting to know the output power capability for each device. But that is not a problem at all, with the formulas given in the above section because of a linear relation between the primary peak current and the output power.

Maximum output power:

$$P_{out} = \eta \cdot P_{in} = \eta \cdot V_{in(DC)} \cdot I_{in(DC)} = \eta \cdot V_{in(DC)} \cdot \frac{1}{2} \cdot i_{peak}$$

[40]

where  $\eta$  is efficiency of power converter.

Now let us calculate what output power can be handled by each particular CoolMOS C3 type, depending on the switching frequency. Due to the complexity of the equations and

### **Maximum Output Power Capability**

dependencies we will use the numeric solution. Next figure shows the output power in a discontinuous conduction mode converter with following operating conditions:

D = 0.21 duty cycle  $V_{dc(in)} = 380 \text{ V}$  bulk capacitor voltage  $V_r = 100 \text{ V}$  reflected voltage  $T_J = 110^{\circ}\text{C}$  junction - temperature  $T_A = 70^{\circ}\text{C}$  ambient - temperature  $T_A = 0.8$  efficiency

Figure 11 Power Handling Capability in Discontinuous Conduction Mode Converter (external heat sink thermal resistance is 10 K/W)

#### 14.2 Continuous Conduction Mode Converter

For a continuous conduction mode converter exists also a linear relation between the primary peak current and the output power of the SMPS. We can also use the formulas for the peak pulse current for continuous conduction mode converter, and multiply them with a linear transformation factor in order to achieve a diagram, where the ratio between the power handling capability and the frequency are shown.

Application Note 35 V1.2, 2002-01

### **Maximum Output Power Capability**

Maximum output power:

$$P_{out} = \eta \cdot P_{in} = \eta \cdot V_{in(DC)} \cdot I_{in(DC)} = \eta \cdot V_{in(DC)} \cdot \frac{1}{2} \cdot \left(i_{min} + i_{peak}\right) \cdot D$$

[41]

where  $\eta$  is efficiency of power converter.

Now let us calculate what output power can be handled by each particular CoolMOS C3 type depending on the switching frequency. Due to the complexity of the equations and dependencies we will use the numeric solution. Next figure shows the output power in a continuous conduction mode converter with following operating conditions:

D = 0.45 duty cycle  $V_{dc(in)} = 380 \text{ V}$  bulk capacitor voltage  $T_J = 110^{\circ}\text{C}$  junction - temperature  $T_A = 70^{\circ}\text{C}$  ambient - temperature  $\eta = 0.8$  efficiency  $K_{minn} = 0.72$  factor  $I_{min}$ ,  $I_{max}$

Figure 12 Power Handling Capability in Continuous Conduction Mode Converter (external heat sink thermal resistance is 10 K/W)

Application Note 36 V1.2, 2002-01

Conclusion

### 15 Conclusion

Due to different MOSFET technologies from several semiconductor manufacturers and significant differences in the way the datasheet is done selecting the right MOSFET for the particular design becomes a complicated task. This application note shows a way to design in the CoolMOS in continuous and discontinuous conduction mode converters.

The introduced iteration approach is based on the calculation of the power losses in the transistor itself. The power losses could be divided into two main parts, the conduction losses and the switching losses. Conduction losses depend on the on state resistance and are simple to calculate. Whereas the switching losses can be influenced by a lot of parameters like nonlinear output drain-source capacitance, total gate resistance, parasitic inductances and capacitances of the circuit layout. These are difficult to handle. Calculation of the switching losses mentioned in this application note are based on measured values.

The cooling condition of the system and the heat sink design limits the maximum allowable power dissipation of the MOSFET in an SMPS. Based on this limitation and on the calculated power losses it is possible to select an optimal transistor type.

Drain current versus the switching frequency charts, as well as output power versus the switching frequency charts can be used as a pre-selection of the MOSFET type for discontinuous and continuous conduction mode converters. It is possible to skip some initial iterations using these charts.

The described approach helps to reduce the number of experimental iterations and thus reduce the design cycle time.

### Infineon goes for Business Excellence

"Business excellence means intelligent approaches and clearly defined processes, which are both constantly under review and ultimately lead to good operating results.

Better operating results and business excellence mean less idleness and wastefulness for all of us, more professional success, more accurate information, a better overview and, thereby, less frustration and more satisfaction."

Dr. Ulrich Schumacher

www.infineon.com