#### **User guide**

EiceDRIVER™ Power EVAL-2EP130R-PR

Full-bridge transformer driver for isolated gate driver power supply for IGBT and MOSFETs

#### **About this document**

#### **Scope and purpose**

This user guide is intended to provide information about the Infineon evaluation board EiceDRIVER™ Power EVAL-2EP130R-PR. It describes the start-up, measurements, and parameter adjustments of the 2EP1xxR (2EP100R, 2EP101R, 2EP110R, and 2EP130R) product family. The 2EP1xxR is a full-bridge transformer driver IC to design isolated gate driver supplies for IGBT and SiC MOSFETs.

#### **Intended audience**

This document is intended for electrical engineers who are knowledgeable about isolated gate driver supply with open loop architecture.

#### **Evaluation board**

This board is used for evaluating and measuring 2EP130R.

This user guide is intended to help adapt the evaluation board EVAL-2EP130R-PR to the supply needs of a large variety of switches. The board supports isolated supply voltages for two gate driver ICs, for example, a high-side and a low-side gate driver IC.

**Note**: The PCB and auxiliary circuits are NOT optimized for final customer design.

**User guide**

Important notice

### **Important notice**

"Evaluation Boards and Reference Boards" shall mean products embedded on a printed circuit board (PCB) for demonstration and/or evaluation purposes, which include, without limitation, demonstration, reference and evaluation boards, kits and design (collectively referred to as "Reference Board").

Environmental conditions have been considered in the design of the Evaluation Boards and Reference Boards provided by Infineon Technologies. The design of the Evaluation Boards and Reference Boards has been tested by Infineon Technologies only as described in this document. The design is not qualified in terms of safety requirements, manufacturing and operation over the entire operating temperature range or lifetime.

The Evaluation Boards and Reference Boards provided by Infineon Technologies are subject to functional testing only under typical load conditions. Evaluation Boards and Reference Boards are not subject to the same procedures as regular products regarding returned material analysis (RMA), process change notification (PCN) and product discontinuation (PD).

Evaluation Boards and Reference Boards are not commercialized products, and are solely intended for evaluation and testing purposes. In particular, they shall not be used for reliability testing or production. The Evaluation Boards and Reference Boards may therefore not comply with CE or similar standards (including but not limited to the EMC Directive 2004/EC/108 and the EMC Act) and may not fulfill other requirements of the country in which they are operated by the customer. The customer shall ensure that all Evaluation Boards and Reference Boards will be handled in a way which is compliant with the relevant requirements and standards of the country in which they are operated.

The Evaluation Boards and Reference Boards as well as the information provided in this document are addressed only to qualified and skilled technical staff, for laboratory usage, and shall be used and managed according to the terms and conditions set forth in this document and in other related documentation supplied with the respective Evaluation Board or Reference Board.

It is the responsibility of the customer's technical departments to evaluate the suitability of the Evaluation Boards and Reference Boards for the intended application, and to evaluate the completeness and correctness of the information provided in this document with respect to such application.

The customer is obliged to ensure that the use of the Evaluation Boards and Reference Boards does not cause any harm to persons or third party property.

The Evaluation Boards and Reference Boards and any information in this document is provided "as is" and Infineon Technologies disclaims any warranties, express or implied, including but not limited to warranties of non-infringement of third party rights and implied warranties of fitness for any purpose, or for merchantability.

Infineon Technologies shall not be responsible for any damages resulting from the use of the Evaluation Boards and Reference Boards and/or from any information provided in this document. The customer is obliged to defend, indemnify and hold Infineon Technologies harmless from and against any claims or damages arising out of or resulting from any use thereof.

Infineon Technologies reserves the right to modify this document and/or any information provided herein at any time without further notice.

**User guide**

**Safety precautions**

### **Safety precautions**

**Note**: Please note the following warnings regarding the hazards associated with development systems.

#### Table 1

#### **Safety precautions**

**Warning:** The isolated output voltages provide a creepage/clearance of 4 mm between output 1 and output 2. Ensure proper protection and coverage in case of use for voltages above SELV level.

**Warning:** The input to output isolation is built for reinforced applications. However the board has not a hipot-test and can therefore not be declared as proven reinforced isolation.

**Warning:** Remove or disconnect power from the drive before you disconnect or reconnect wires, or perform maintenance work. Wait five minutes after removing power to discharge the bus capacitors. Do not attempt to service the drive until the bus capacitors have discharged to zero. Failure to do so may result in personal injury or death.

**Caution:** The heat sink and device surfaces of the evaluation or reference board may become hot during testing. Hence, necessary precautions are required while handling the board. Failure to comply may cause injury.

**Caution:** Only personnel familiar with the drive, power electronics and associated machinery should plan, install, commission and subsequently service the system. Failure to comply may result in personal injury and/or equipment damage.

**Caution:** The evaluation or reference board contains parts and assemblies sensitive to electrostatic discharge (ESD). Electrostatic control precautions are required when installing, testing, servicing or repairing the assembly. Component damage may result if ESD control procedures are not followed. If you are not familiar with electrostatic control procedures, refer to the applicable ESD protection handbooks and guidelines.

**Caution:** A drive that is incorrectly applied or installed can lead to component damage or reduction in product lifetime. Wiring or application errors such as undersizing the motor, supplying an incorrect or inadequate AC supply, or excessive ambient temperatures may result in system malfunction.

**Caution:** The evaluation or reference board is shipped with packing materials that need to be removed prior to installation. Failure to remove all packing materials that are unnecessary for system installation may result in overheating or abnormal operating conditions.

#### **Table of contents**

### **Table of contents**

|     | About this document                                 | 1  |

|-----|-----------------------------------------------------|----|

|     | Important notice                                    | 2  |

|     | Safety precautions                                  | 3  |

|     | Table of contents                                   | 4  |

| 1   | The board at a glance                               | 5  |

| 2   | System and functional description                   | 8  |

| 2.1 | Theory of 2EP1xxR using peak rectification topology | 8  |

| 2.2 | Getting started                                     | 10 |

| 2.3 | Resistor based operating parameter adjustment       | 11 |

| 2.4 | Bypass mode operation                               | 12 |

| 2.5 | Use case: SiC MOSFET supply example                 | 12 |

| 3   | System design                                       | 14 |

| 3.1 | Schematics                                          | 14 |

| 3.2 | Layout                                              | 14 |

| 3.3 | Bill of material                                    | 15 |

| 3.4 | Connector details                                   | 15 |

| 4   | System performance                                  | 17 |

| 5   | Additional information                              | 21 |

|     | Revision history                                    | 22 |

|     | Disclaimer                                          | 23 |

#### 1 The board at a glance

#### The board at a glance 1

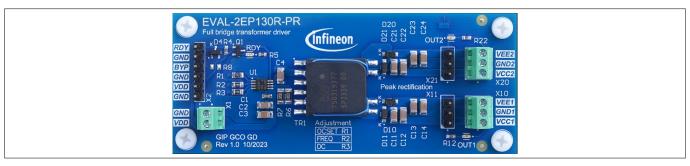

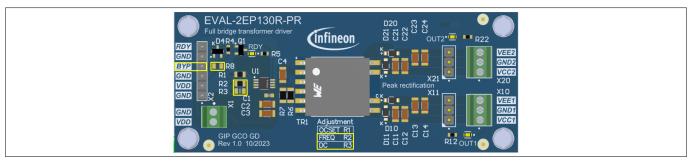

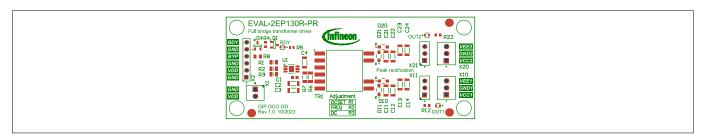

This user guide (UG-2024-02) describes the evaluation board, EVAL-2EP130R-PR. This board has been designed as a validation board that can be used by design engineers to evaluate the family of full-bridge transformer driver ICs - 2EP1xxR.

The board is partially populated and needs final assembly at the position R3 and TR1 according to the target configuration of the output voltage.

Details about the transformer driver IC is available in the datasheet of the EiceDRIVER™ Power 2EP1xxR family.

**Evaluation board EVAL-2EP130R-PR** Figure 1

This image includes the originally not assembled components R3 and TR1.

#### **Delivery content**

The delivery contains:

- One EVAL-2EP130R-PR, 90 × 37 mm<sup>2</sup> in size

- Three transformers for custom assembly at position TR1

- WE 750319375: TTR=1.25:1, with VDD=15 V, DC=33% provides +15/-7.5 V for IGBTs

- WE 750319376: TTR=1.5:1, with VDD=15 V, DC=22% provides +15/-4 V for SiC MOSFETs

- WE 750319377: TTR=1.4:1, with VDD=15 V, DC=14% provides +18/-2.5 V for SiC MOSFETs

#### **Simplified schematic**

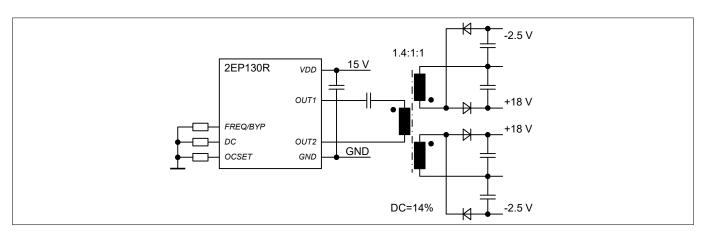

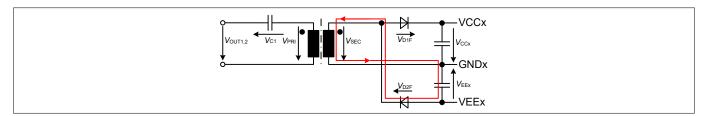

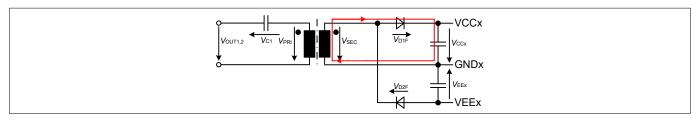

Figure 2 Peak rectifier schematic for 2EP130R

This simplified schematic shows the peak rectification for two separated rails, each with a positive and negative output voltage.

#### **Main features**

The evaluation board, EVAL-2EP130R-PR, is designed for easy evaluation of the full-bridge transformer driver IC. The following table shows the product variants in the EiceDRIVER™ Power 2EP1xxR family and their differentiating features.

#### 1 The board at a glance

Table 2 2EP1xxR product variants

| Product name | Frequency         | Duty cycle | Average overcurrent protection | Bypass input |

|--------------|-------------------|------------|--------------------------------|--------------|

| 2EP100R      | 66 kHz or 100 kHz | 33% or 50% | Level 4                        | no           |

| 2EP101R      | 50 kHz or 66 kHz  | 12% or 17% | Level 4                        | no           |

| 2EP110R      | 50 kHz or 66 kHz  | 10% 50%    | Level 4                        | no           |

| 2EP130R      | 50 kHz 695 kHz    | 10% 50%    | Level 1-5                      | yes          |

All product variants are pin compatible and can be used with matching configuration settings in customerspecific designs. 2EP130R is pre-assembled on EVAL-2EP130R-PR for complete feature evaluation.

The evaluation board provides all the necessary supply, load, and signal connections for an application. It offers the following features:

- Wide input supply range V<sub>VDD</sub> from 5 V to 20 V

- Output power of up to 5 W (depending on duty cycle)

- Dual isolated output supply rails with peak rectification topology and duty cycle adjustable output voltage

- Wide frequency operating range from 50 kHz to 695 kHz using the internal oscillator or an external pulse width modulation (PWM)

- Adjustable overcurrent threshold

- Short circuit protection of power outputs

- Overtemperature protection

- RDY status output indication for normal operation

#### **Board parameters and technical data**

Parameters of the evaluation board, EVAL-2EP130R-PR, must respect the absolute maximum ratings listed below and should be operated within the recommended operating range.

**Absolute maximum ratings** Table 3

| Parameter                            | Symbol                                                                        | Values |     | Unit | Note/conditions                                                        |  |

|--------------------------------------|-------------------------------------------------------------------------------|--------|-----|------|------------------------------------------------------------------------|--|

|                                      |                                                                               | Min    | Max |      |                                                                        |  |

| Supply voltage                       | $V_{ m VDD}$                                                                  | 0      | 22  | V    | Referenced to GND                                                      |  |

| Positive output voltage              | V <sub>VCC1</sub> ,V <sub>VCC2</sub>                                          | 0      | 35  | V    | Limited by capacitor and diode voltage rating, referenced to GND1/GND2 |  |

| Negative output voltage              | $V_{\text{VEE1}}, V_{\text{VEE2}}$                                            | -35    | 0   | V    | Limited by capacitor and diode voltage rating, referenced to GND1/GND2 |  |

| Input to output/between output rails | V <sub>ISO</sub>                                                              | -800   | 800 | V    | Functional isolation, no HiPot test performed                          |  |

| Output current                       | I <sub>VCC1</sub> , I <sub>VCC2</sub> , I <sub>VEE1</sub> , I <sub>VEE2</sub> | 2      | 400 | mA   | Depending on configuration, limited by IC                              |  |

| RDY sink current                     | I <sub>RDY</sub>                                                              | 0      | 10  | mA   | Referenced to GND                                                      |  |

| RDY voltage                          | $V_{RDY}$                                                                     | 0      | 6.5 | V    | Referenced to GND                                                      |  |

#### 1 The board at a glance

Table 4 Recommended operating range

| Parameter               | Symbol                                                                        | Values          |     | Unit | Note/conditions                                                        |  |

|-------------------------|-------------------------------------------------------------------------------|-----------------|-----|------|------------------------------------------------------------------------|--|

|                         |                                                                               | Min             | Max | ]    |                                                                        |  |

| Supply voltage          | $V_{ m VDD}$                                                                  | 5               | 20  | V    | Referenced to <i>GND</i> , depending on configuration                  |  |

| Positive output voltage | V <sub>VCC1</sub> ,V <sub>VCC2</sub>                                          | 0               | 35  | V    | Limited by capacitor and diode voltage rating, referenced to GND1/GND2 |  |

| Negative output voltage | $V_{\text{VEE1}}, V_{\text{VEE2}}$                                            | -35             | 0   | V    | Limited by capacitor and diode voltage rating, referenced to GND1/GND2 |  |

| Bypass signal voltage   | $V_{BYP}$                                                                     | 0               | 5.5 | V    | Referenced to GND                                                      |  |

| Bypass signal frequency | $f_{BYP}$                                                                     | 50              | 695 | kHz  | Transformer and duty-cycle dependent                                   |  |

| Output current          | I <sub>VCC1</sub> , I <sub>VCC2</sub> , I <sub>VEE1</sub> , I <sub>VEE2</sub> | 2 <sup>1)</sup> | 150 | mA   | Depending on configuration, limited by IC                              |  |

| RDY sink current        | I <sub>RDY</sub>                                                              | 0               | 10  | mA   | Referenced to GND                                                      |  |

<sup>1)</sup> Minimal load for stable operation

#### 2 System and functional description

#### System and functional description 2

#### 2.1 Theory of 2EP1xxR using peak rectification topology

This section describes the theory behind the full-bridge power stage of 2EP1xxR and the peak rectification topology to provide two isolated output voltages. Each transformer output winding supports a positive and negative output voltage. The ratio between the positive voltage and negative voltage is defined by the duty cycle.

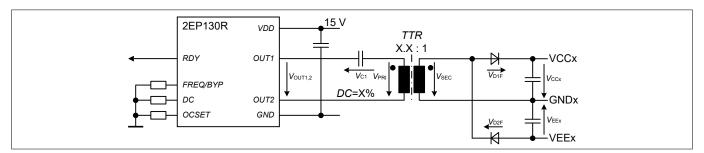

Figure 3 Simplified schematic of 2EP130R using peak rectification topology

The voltage arrows indicate the polarity of the corresponding symbol for use in the equations provided later.  $V_{PRI}$  and  $V_{SEC}$  represent the transformer voltages,  $V_{DxF}$  the individual diode forward voltages,  $V_{C1}$  the voltage across the primary DC blocking capacitor, and  $V_{CCx}/V_{FFx}$  the output voltage.

The following sections describe how to determine the output voltages of a peak rectification according to:

- the applied input voltage to 2EP

- the applied duty cycle by chopping the input voltage

- the level-shift (offset) of the serial capacitor

- the transformer turn ratio

- the peak current rectification

DC offset voltage and influence of transformer turn ratio output voltage

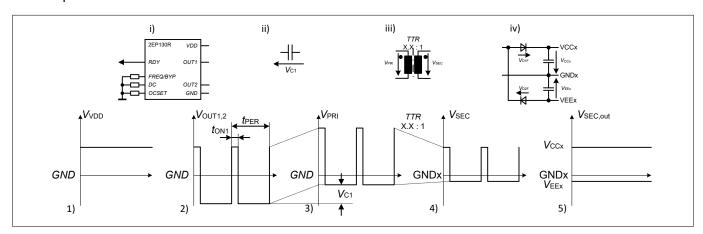

The figure visualizes the idealized voltage wave forms at each step (1-5) and the involved components at the intermediate step (i-iv). The input supply voltage  $V_{VDD}$  (1) is applied to 2EP130R (i). It provides the output voltage  $V_{OUT1,2}$  (2) to the serial capacitor (ii). This results in the shifted input voltage  $V_{PRI}$  (3) for the transformer (iii). The transformer scales the input voltage to the secondary side as  $V_{SEC}$  (4). The last step is peak current rectification (iv) and its output voltages (5).

#### Full-bridge transformer driver 2EP130R

2EP130R chops the applied supply voltage,  $V_{VDD}$ , according to the configured switching frequency and duty cycle (DC). The output of OUT1 is switched between VDD and GND. The same is valid for OUT2. However, its

#### **User guide**

#### 2 System and functional description

switching pattern is inverted. This results in twice the amplitude of  $V_{\rm VDD}$  across the outputs  $V_{\rm OUT1,2}$  or with a GND reference:

$$V_{OUT1,2} = \pm V_{VDD}$$

The duty cycle is calculated as:  $DC = \frac{t_{\rm ON1}}{t_{\rm PER}}$  with the on duration of output 1,  $t_{\rm ON1}$ , and the period time,  $t_{\rm PER}$ , of the switching frequency. The duty cycle for OUT2 always complements that of OUT1. The duty cycle always refers to OUT1.

#### Serial capacitor C1

The serial capacitor creates an offset derived from the duty cycle. The DC offset voltage,  $V_{C1}$ , is therefore an integral component for calculating output voltages. The capacitor voltage level during steady state operation is calculated as:

$$V_{\rm C1} = V_{\rm VDD} \left( 1 - \frac{2 \cdot DC}{100 \%} \right)$$

The offset voltage  $V_{C1}$  varies between 80% of  $V_{VDD}$  at 10% and 0% of  $V_{VDD}$  at 50% duty cycle. Since 2EP130R only allows duty cycles between 10% to 50%, the resulting offset voltage is positive according to its indicated polarity. Any waveform with a duty cycle not equal to 50% has a DC offset voltage component. The serial capacitor basically removes the direct component from the chopped supply voltage. Due to this, the asymmetric duty cycle converts the symmetric peak, V<sub>OUT1.2</sub>, into asymmetric peak voltages:

$$V_{\text{RPI}} = \pm V_{\text{VDD}} + V_{\text{C1}}$$

The primary transformer voltage alternates between  $(+V_{VDD}+V_{C1})$  and  $(-V_{VDD}+V_{C1})$  due to the full-bridge output stage of 2EP130R and the aforementioned offset voltage stored within  $V_{C1}$ .

#### Transformer, transformer turn ratio (TTR), and transformer saturation

The transformer transforms the primary input voltage,  $V_{PRI}$ , according to the transformer turn ratio (TTR) to the secondary side. The secondary transformer voltage,  $V_{\text{SEC}}$ , is calculated as:

$$V_{\text{SEC}} = \frac{V_{\text{PRI}}}{TTR} = \pm \frac{V_{\text{DD}}}{TTR} + \frac{V_{\text{C1}}}{TTR}$$

The aforementioned V<sub>C1</sub> offset voltage ensures an equal voltage \* time product below and above ground potential for the primary winding. This equal voltage \* time product prevents the transformer from saturating, even when driven with asymmetric peak voltages.

#### **Peak current rectification**

Due to the diodes in the peak rectification circuit, individual current paths must be considered separately. The matching voltage polarity of the secondary transformer voltage should be taken into account when calculating the expected output capacitor voltages.

#### Current path of negative voltage rail

The current path to charge the negative voltage rail requires  $V_{\text{SEC}}$  to be in reverse polarity. The current charges the negative output voltage capacitor and closes the circuit via the diode, D2, in forward direction resulting in the  $V_{\rm D2F}$  voltage drop.

The negative output voltage then results in:  $V_{\rm EEx} = V_{\rm SEC(neg)} + V_{\rm D2F}$

As the secondary transformer voltage is negative at that half-wave, the resulting output voltage is also negative, but reduced by the diode forward voltage.

The positive output voltage behaves similar to the negative output voltage.

(1)

(2)

#### 2 System and functional description

#### Figure 6 Current path of positive voltage rail

The current path to charge the positive voltage rail requires  $V_{\rm SEC}$  to be in the indicated polarity (positive half-wave). The current charges the positive output voltage capacitor and closes the circuit via the diode, D1, in forward direction resulting in the  $V_{\rm D1F}$  voltage drop.

The positive output voltage then results in:  $V_{\rm CCx} = V_{\rm SEC(pos)} - V_{\rm D1F}$

Both output voltages can be written as:

Assumption 1: All forward voltages are equal:

$$V_{\rm F} = V_{

m D1F} = V_{

m D2F}$$

Assumption 2: Amplitudes of both the positive and negative half-waves experience the same offset:

$$V_{\rm SEC} = \pm \frac{V_{\rm DD}}{TTR} + \frac{V_{\rm C1}}{TTR}$$

Positive output voltage:

$$V_{\text{CCx}} = \left(\frac{V_{\text{DD}}}{TRR} + \frac{V_{\text{C1}}}{TRR} - V_{\text{F}}\right)$$

Negative output voltage

$$V_{\text{EEx}} = -\left(\frac{V_{\text{DD}}}{TRR} - \frac{V_{\text{C1}}}{TRR} - V_{\text{F}}\right)$$

Note:

Equal load at positive and negative voltage rails result in asymmetric currents for positive and negative half-waves. This can result in output voltages different from the ones calculated using the equations given in this section. When designing a peak rectifier circuit with dual output rails, use the same winding polarity for both rails to ensure that the offset gets applied in the same manner.

Inserting the  $V_{CI}$  equation into the output voltage equations results in:

Positive output voltage:

$$V_{\text{CCx}} = \frac{2 \cdot V_{\text{VDD}}}{TRR} (1 - DC) - V_{\text{F}}$$

Negative output voltage:

$$V_{\text{EEx}} = \frac{2 \cdot V_{\text{VDD}}}{TRR} (-DC) + V_{\text{F}}$$

#### 2.2 Getting started

This section describes the prerequisites to fully assemble the evaluation board and how to power it up.

#### **Prerequisites**

- 1. Select a transformer and a matching duty cycle configuration resistor for the intended output voltages, see Chapter 2.5

- **2.** Assemble the selected transformer at the position TR1.

- **3.** Assemble the selected duty cycle configuration resistor at the position R3.

#### **User guide**

#### 2 System and functional description

- 4. Verify the OCset level configuration of R1. The default is 5.

- 5. Verify the switching frequency configuration of R2. The default is 65 kHz, which is generated internally.

#### Steps to power up EVAL-2EP130R-PR with its default configuration

- 1. Connect a load to the isolated transformer output terminals of X10/X11 and X20/X21 connectors.

- Consider the polarities of VCC1/GND1/VEE1 and VCC2/GND2/VEE2

- The LEDs OUT1 and OUT2 also act as a minimal base load. Without any external load, the output voltages will be higher than calculated in Chapter 2.5

- 2. Connect a positive supply voltage between VDD and GND at the corresponding terminals of the X1/X2 connectors. Select the voltage according to the output voltage calculation.

- The RDY LED indicates the ready status of 2EP130R. 3.

After the supply voltage is applied at VDD, 2EP130R performs a soft start. The voltage at the isolated outputs increases and the RDY status LED lights up. If the status LED does not light up, the transformer driver is either not powered correctly, is still in the start-up mode (soft start), or is in the fault mode (overcurrent or overtemperature).

#### 2.3 Resistor based operating parameter adjustment

2EP130R offers three input pins to configure the switching frequency, the duty cycle, and the average overcurrent protection during an operation.

- Resistor R1 sets the overcurrent threshold at pin OCSET; default:  $R1 = 47500 \Omega$ , OCset level: 5

- Resistor R2 sets the frequency at pin FREQ/BYP; default: R2 = 698, switching frequency: 65 kHz

- Resistor R3 sets the duty cycle at pin DC; default: R3 is not assembled

You can use the following table to select an individual resistor value from the column **E96 series** and match it to OCSET, FREQ, and DC column values in the same row.

Parameter adjustments of resistor value to functional value Table 5

| Resistor   | R1    | R2   | R3 | Resistor   | R1    | R2   | R3 |

|------------|-------|------|----|------------|-------|------|----|

| E96 series | OCSET | FREQ | DC | E96 series | OCSET | FREQ | DC |

| Ω          | -     | kHz  | %  | Ω          | -     | kHz  | %  |

| 332        | 1     | 50   | 10 | 5760       | 3     | 199  | 31 |

| 412        | 1     | 53   | 11 | 6980       | 3     | 213  | 32 |

| 499        | 1     | 57   | 12 | 8250       | 3     | 227  | 33 |

| 590        | 1     | 61   | 13 | 9530       | 4     | 243  | 34 |

| 698        | 1     | 65   | 14 | 11000      | 4     | 259  | 35 |

| 806        | 1     | 70   | 15 | 12700      | 4     | 277  | 36 |

| 931        | 1     | 74   | 16 | 14700      | 4     | 295  | 37 |

| 1070       | 1     | 79   | 17 | 16500      | 4     | 316  | 38 |

| 1210       | 2     | 85   | 18 | 18700      | 4     | 337  | 39 |

| 1370       | 2     | 90   | 19 | 21000      | 4     | 360  | 40 |

| 1540       | 2     | 97   | 20 | 23700      | 4     | 384  | 41 |

| 1740       | 2     | 103  | 21 | 26700      | 5     | 410  | 42 |

| 1960       | 2     | 110  | 22 | 30100      | 5     | 438  | 43 |

| 2210       | 2     | 118  | 23 | 34000      | 5     | 468  | 44 |

| 2490       | 2     | 126  | 24 | 38300      | 5     | 500  | 45 |

(table continues...)

#### **User guide**

#### 2 System and functional description

Table 5 (continued) Parameter adjustments of resistor value to functional value

| Resistor   | R1    | R2   | R3 | Resistor   | R1    | R2   | R3 |

|------------|-------|------|----|------------|-------|------|----|

| E96 series | OCSET | FREQ | DC | E96 series | OCSET | FREQ | DC |

| 2800       | 2     | 134  | 25 | 42200      | 5     | 534  | 46 |

| 3160       | 3     | 143  | 26 | 47500      | 5     | 570  | 47 |

| 3480       | 3     | 153  | 27 | 52300      | 5     | 609  | 48 |

| 3920       | 3     | 163  | 28 | 57600      | 5     | 651  | 49 |

| 4320       | 3     | 175  | 29 | 63400      | 5     | 695  | 50 |

| 4750       | 3     | 186  | 30 |            |       |      |    |

#### 2.4 Bypass mode operation

2EP130R supports bypass mode operation. In this mode, 2EP130R follows an externally applied pulse width modulation (PWM) signal at FREQ/BYP pin for frequency and duty cycle during operation.

During start-up, the IC follows the internal soft start sequence. Therefore, the frequency and individual pulse length deviate from the externally applied PWM signal during the soft start. The applied switching frequency should be kept constant during start-up. The transformer driver syncs up with that frequency in the final moments of the start-up sequence. For further information, see EiceDRIVER™ 2EP1xxR family datasheet.

Modification for bypass mode operation Figure 7

Modify the default assembly to operate the evaluation board in bypass mode:

- Resistor R3 at DC pin: change to  $0 \Omega$  to enable bypass mode

- Resistor R2 at FREQ/BYP pin: remove resistor

- Resistor R8: assemble a 0  $\Omega$  resistor to connect the X2.BYP pin to the FREQ/BYP pin

Ensure that the external frequency stays within the 2EP130R frequency, duty cycle, and voltage range.

#### 2.5 Use case: SiC MOSFET supply example

The calculations in this section are based on the equations from Chapter 2.1. They have been re-arranged to calculate the duty cycle and transformer turn ratio (TTR) from the requested voltages. The purpose for this example is to get an output voltage suitable for SiC MOSFETs.

#### **Application parameters (input)**

User guide

- Input supply voltage for 2EP130R:  $V_{DD}$  = 15 V

- Nominal target positive output voltage after peak rectification:  $V_{CCX} = 18 \text{ V}$

- Nominal target negative output voltage after peak rectification:  $V_{\text{FFx}} = -2.5 \text{ V}$

- Expected diode forward voltage:  $V_F = 0.4 \text{ V}$

The output voltages provided here are considered nominal when increase in light load output voltage and drop in load-dependent output voltage are negligible. For the transformer suggested in this example, the nominal

v1.00

#### **User guide**

#### 2 System and functional description

load is approximately 15 mA. To consider the impact of the diode forward voltage on the output voltages a more accurate calculation of parameters is required.

#### Calculating and selecting the duty cycle

To calculate the duty cycle (DC) for 2EPxxR, the positive output voltage  $V_{CCx}$  should be put relative to the total output voltage. The voltage at the transformer should be one forward voltage drop higher then each of the expected output voltages. The whole value then needs to be subtracted from 1 to get the duty cycle for OUT1:

$$DC = 1 - \frac{V_{\text{CCx}} + V_{\text{F}}}{2 \cdot V_{\text{F}} + V_{\text{CCx}} - V_{\text{EEx}}}$$

$$DC = 1 - \frac{18 V + 0.4 V}{2 \cdot 0.4 V + 18 V - (-2.5 V)}$$

$$DC = 0.136 \Rightarrow DC_{selected} = 14 \%$$

The percentage value needs to be a whole number to be compatible with 2EP. The selected duty cycle, in this example, is rounded to 14%. According to the resistor selection table given in the 2EP1xxR datasheet, this duty cycle setting requires a resistor value of 698  $\Omega$  at the DC pin. It introduces a slight offset in the actual output voltage compared to the target value.

2EP1xxR supports duty cycles in the range of 10% and 50%. Note:

#### Calculating and selecting the transformer turn ratio

To calculate the transformer turn ratio (TTR), the total primary transformer voltage needs to be put relative to the total output voltage of the transformer on the secondary side as required by the application. As 2EP1xxR is a full-bridge transformer driver, the total voltage at the primary transformer winding is twice the input supply voltage of 2EP1xxR. The serial capacitor between 2EP1xxR and the transformer does not influence the total input voltage of the transformer. Its offset is applied to both polarities so that the absolute voltage remains

$$\begin{split} TTR &= \frac{2 \cdot V_{DD}}{2 \cdot V_F + V_{CCx} - V_{EEx}} \\ TRR &= \frac{2 \cdot 15 \ V}{2 \cdot 0.4 \ V + 18 \ V - (-2.5 \ V)} \\ TTR &= 1.41 \Rightarrow TTR_{selected} = 1.4 \end{split}$$

In this example, the calculated transformer turn ratio is very close to that of the Würth Elektronik transformer (part number 750319377) that has a transformer turn ratio of 1.4:1. The calculation and selection of a matching transformer again introduces an offset from the target values. It is therefore, recommended that the selection be verified as the last step.

#### Verifying the selection

After all required parameters are identified and matched to their components, the resulting output voltage can be calculated and compared to the target voltages:

$$V_{CC} = \frac{2 \cdot V_{DD} \cdot (1 - DC_{selected})}{TRR_{selected}} - V_F \Rightarrow V_{CC} = 18.03 V$$

$$V_{EE} = \frac{2 \cdot V_{DD} \cdot (-DC_{selected})}{TRR_{selected}} + V_F \Rightarrow V_{EE} = -2.60 V$$

In this example, the output voltages match with the target values quite well and only deviate by 0.2% for the positive and 4% for the negative output voltage. Considering that 2EP1xxR is an open loop transformer driver, the actual output voltages also depend on the stability of the input voltages and the load condition of these output voltages.

#### 3 System design

### 3 System design

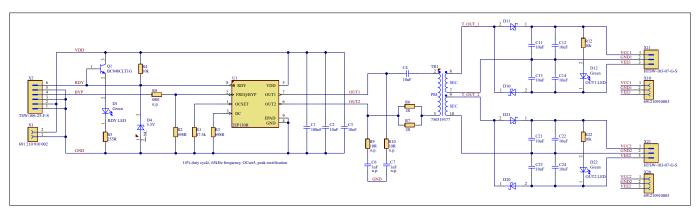

#### 3.1 Schematics

Figure 8 Schematic

The schematic uses default resistor values for average overcurrent setting level 5 and a target switching frequency of 65 kHz. The resistor for the duty cycle adjustment and the transformer are not assembled by default. Assuming a transformer turn ratio of 1.4:1 and a duty cycle of 14%, an input voltage of 15 V will result in a positive output voltage of approximately 18 V and a negative output voltage of -2.6 V.

### 3.2 Layout

Figure 9 Component side assembly

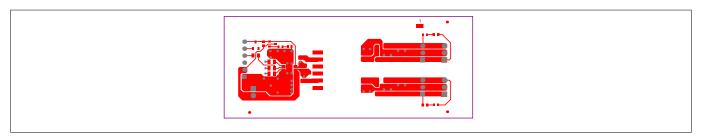

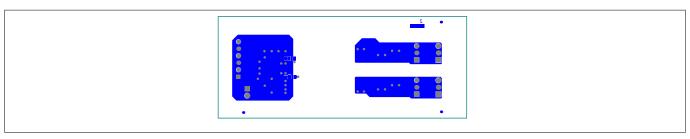

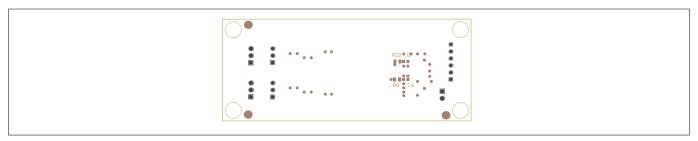

The EVAL-2EP130R-PR evaluation board has an approximate size of 91 × 37 mm<sup>2</sup>. The two-layer PCB uses a standard copper thickness of 1 oz. The top layer is used for routing. The bottom layer mainly consists of three GND planes. A single-layer design is possible.

Figure 10 Top layer

**User guide**

#### 3 System design

Figure 11 **Bottom layer**

Solder side assembly Figure 12

#### 3.3 **Bill of material**

The complete bill of material is available in the download section of Infineon's homepage. Login credentials are required to download this material.

BOM of the most important parts of the evaluation board Table 6

| S. No. | <b>Ref Designator</b> | Description                                                                              | Manufacturer     | Manufacturer P/N | Populated |

|--------|-----------------------|------------------------------------------------------------------------------------------|------------------|------------------|-----------|

| 1      | R1                    | RES SMD 47.5 kΩ<br>125 mW 1% 0805                                                        | Vishay           | CRCW080547K5FK   | Yes       |

| 1      | R2                    | RES SMD 698 Ω<br>125 mW 1% 0805                                                          | Vishay           | CRCW0805698RFK   | Yes       |

| 1      | R3                    | RES SMD 698 Ω<br>125 mW 1% 0805                                                          | Vishay           | CRCW0805698RFK   | No        |

| 1      | TR1                   | Transformer,<br>1 mH, Turn Ratio<br>1.4:1                                                | Wurth Elektronik | 750319377 r00    | No        |

| 1      | U1                    | Full-bridge<br>transformer<br>driver for IGBT<br>and SiC MOSFET<br>gate driver<br>supply | Infineon         | 2EP130R          | Yes       |

#### 3.4 **Connector details**

Table 7 **Connector X1 - Input supply (alternate connector)**

| PIN  | Label | Function                                            |  |

|------|-------|-----------------------------------------------------|--|

| X1.1 | GND   | Primary input ground reference                      |  |

| X1.2 | VDD   | Input supply voltage for transformer driver 2EP130R |  |

#### 3 System design

#### Table 8 Connector X2 - Input side signals and supply

| PIN  | Label | Function                                            |  |

|------|-------|-----------------------------------------------------|--|

| X2.1 | GND   | Primary input ground reference                      |  |

| X2.2 | VDD   | Input supply voltage for transformer driver 2EP130R |  |

| X2.3 | GND   | Primary input ground reference                      |  |

| X2.4 | ВҮР   | External PWM input pin for bypass operation mode    |  |

| X2.5 | GND   | Primary input ground reference                      |  |

| X2.6 | RDY   | Ready status output pin, open drain                 |  |

#### Table 9 Connectors X10 and X11 - Output supply rail 1

| PIN          | Label | Function                              |  |

|--------------|-------|---------------------------------------|--|

| X10.1, X11.1 | VCC1  | Positive supply voltage output rail 1 |  |

| X10.2, X11.2 | GND1  | Ground reference output rail 1        |  |

| X10.3, X11.3 | VEE1  | Negative supply voltage output rail 1 |  |

#### Table 10 Connectors X20 and X21 - Output supply rail 2

| PIN          | Label | Function                              |  |

|--------------|-------|---------------------------------------|--|

| X20.1, X21.1 | VCC2  | Positive supply voltage output rail 2 |  |

| X20.2, X21.2 | GND2  | Ground reference output rail 2        |  |

| X20.3, X21.3 | VEE2  | Negative supply voltage output rail 2 |  |

#### 4 System performance

#### System performance 4

This section shows measurement results of the EVAL-2EP130R-PR evaluation board on efficiency, switching wave forms, start-up behavior of output voltages, and output voltage ripple.

#### **Efficiency**

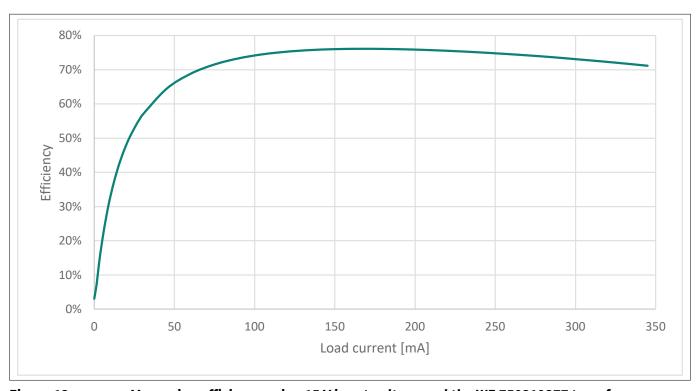

Figure 13 Measuring efficiency using 15 V input voltage and the WE 750319377 transformer

The efficiency measurement records the output voltages and currents and puts them relative to the 2EP input voltage and current during a steady state operation. This measurement was repeated for each individual load current point and drawn on this graph. The efficiency curve varies under different operating conditions such as input voltage, switching frequency, duty cycle and component selection of the transformer. This measurement was performed at 15 V, 80 kHz, 12% duty cycle, and using Würth Elektronik's transformer 750319377.

#### 4 System performance

#### Switching waveform at start-up

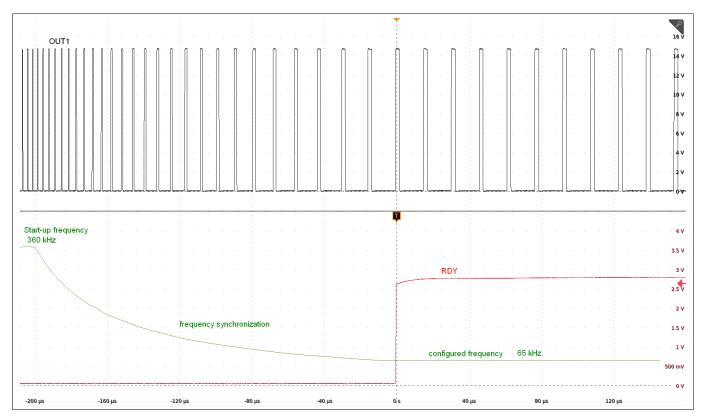

Figure 14 OUT1 switching waveform

The upper diagram shows the *OUT1* switching waveform. From left to right, 2EP1xxR is operating in the start-up peak current mode. When it reaches the target duty cycle without triggering the peak current limits, it synchronizes the switching frequency with the configured frequency. On reaching the target frequency, 2EP1xxR releases the *RDY* pin to indicate a successful start-up.

#### 4 System performance

#### Start-up behavior of the output voltages

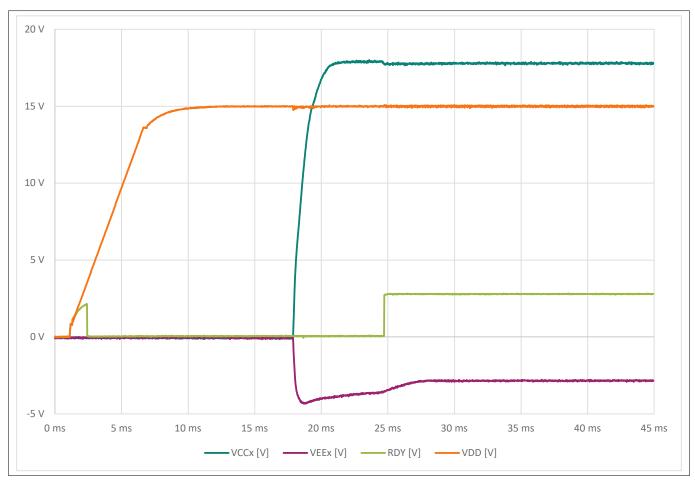

Figure 15 Start-up behavior

This diagram shows the input voltage ramp up at VDD together with the generated output voltages, VCCX and VEEX, and the RDY signal of the evaluation board.

The RDY signal briefly follows the input supply voltage, VDD, until the internal under voltage lockout (UVLO) circuit activates and pulls the RDY signal down to GND level. 2EP1xxR releases the RDY signal after the internal start-up phase.

# infineon

#### 4 System performance

#### **Output voltage ripple**

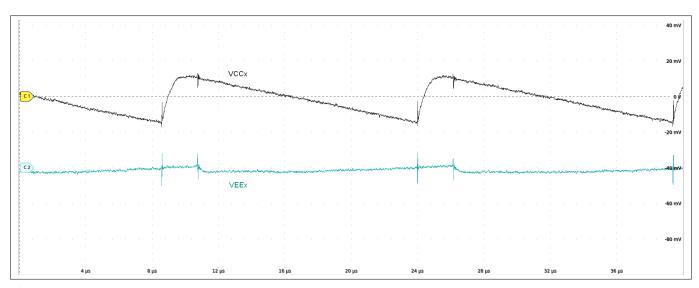

Figure 16 VCCx and VEEx output voltage ripple

The output voltage ripple of *VCCx* has a higher amplitude due to the selected duty cycle. At a constant load on both output levels, 2EP1xxR needs to recharge the output capacitor for *VCCx* within a shorter period of time compared to the output capacitor for *VEEx*. This measurement shows the output ripple for a load current of approximately 30 mA.

### **User guide**

#### 5 Additional information

#### **Additional information** 5

#### Table 11 Orderable part numbers

| Evaluation board    | OPN                   | Description                                              |

|---------------------|-----------------------|----------------------------------------------------------|

| EVAL-2EP130R-PR     | EVAL2EP130RPRTOBO1    | 2EP130R board with peak rectification and 3 transformers |

| EVAL-2EP130R-PR-SiC | EVAL2EP130RPRSICTOBO1 | 2EP130R board with peak rectification for SiC MOSFETs    |

| EVAL-2EP130R-VD     | EVAL2EP130RVDTOBO1    | 2EP130R board with voltage doubler for IGBTs             |

#### Compatible gate driver evaluation boards Table 12

| Evaluation board      | OPN                      | Description                                                                       |

|-----------------------|--------------------------|-----------------------------------------------------------------------------------|

| EVAL-1ED3121MX12H     | EVAL1ED3121MX12HTOBO1    | 1ED3121MX12H board - 2300 V, 5.5 A, 5.7 kV (rms) with separate output             |

| EVAL-1ED3122MX12H     | EVAL1ED3122MX12HTOBO1    | 1ED3122MX12H board - 2300 V, 10 A, 5.7 kV (rms) with active Miller clamp          |

| EVAL-1ED3124MX12H     | EVAL1ED3124MX12HTOBO1    | 1ED3124MX12H board - 2300 V, 14 A, 5.7 kV (rms) with separate output              |

| EVAL-1ED3142MU12F-SIC | EVAL1ED3142MU12FSICTOBO1 | 1ED3142MU12F board - 2300 V, 6.5 A, 3 kV (rms) with separate output               |

| EVAL-1ED3241MC12H     | EVAL1ED3241MC12HTOBO1    | 1ED3241MC12H board - 2300 V, 18 A, 5.7 kV (rms) with two-level slew-rate control  |

| EVAL-1ED3251MC12H     | EVAL1ED3251MC12HTOBO1    | 1ED3251MC12H board - 2300 V, 18 A, 5.7 kV (rms) with slew-rate control and clamp  |

| EVAL-1ED3321MC12N     | EVAL1ED3321MC12NTOBO1    | 1ED3321MC12N board - 2300 V, 8.5 A, 5.7 kV (rms) with DESAT and Soft-off          |

| EVAL-1ED3491MX12M     | EVAL1ED3491MX12MTOBO1    | 1ED3491MX12M board - 2300 V, 9 A, 5.7 kV (rms) with adjustable DESAT and Soft-off |

| EVAL-1ED3890MX12M     | EVAL1ED3890MX12MTOBO1    | 1ED3890MX12M board - 2300 V, 9 A, 5.7 kV (rms) with I2C configurable behavior     |

**User guide**

**Revision history**

## **Revision history**

| Document version | Date of release | Description of changes |

|------------------|-----------------|------------------------|

| v1.00            | 2024-02-26      | initial version        |

|                  |                 | •                      |

#### Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2024-02-26 Published by Infineon Technologies AG 81726 Munich, Germany

© 2024 Infineon Technologies AG All Rights Reserved.

Do you have a question about any aspect of this document?

Email: erratum@infineon.com

Document reference IFX-akc1703078346547

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com)

#### Warnings

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.