# Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

# Continuity of document content

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

# Continuity of ordering part numbers

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

# PSoC CY8C20xx7/S TRM

# PSoC<sup>®</sup> CY8C20xx7/S

# Technical Reference Manual (TRM)

Document No. 001-74066 Rev. \*F

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 Phone: +1.408.943.2600 http://www.cypress.com

### Copyrights

Copyright © 2011-2015 Cypress Semiconductor Corporation. All rights reserved.

PSoC® is a registered trademark and PSoC Designer<sup>™</sup>, and Programmable System-on-Chip<sup>™</sup> are trademarks of Cypress Semiconductor Corporation (Cypress), along with Cypress® and Cypress Semiconductor<sup>™</sup>. All other trademarks or registered trademarks referenced herein are the property of their respective owners.

Purchase of I<sup>2</sup>C components from Cypress or one of its sublicensed Associated Companies conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips. As from October 1st, 2006 Philips Semiconductors has a new trade name - NXP Semiconductors.

The information in this document is subject to change without notice and should not be construed as a commitment by Cypress. While reasonable precautions have been taken, Cypress assumes no responsibility for any errors that may appear in this document. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Cypress.

#### Disclaimer

CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PAR-TICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

#### **Flash Code Protection**

Note the following details of the Flash code protection features on Cypress devices.

Cypress products meet the specifications contained in their particular Cypress Data Sheets. Cypress believes that its family of products is one of the most secure families of its kind on the market today, regardless of how they are used. There may be methods, unknown to Cypress, that can breach the code protection features. Any of these methods, to our knowledge, would be dishonest and possibly illegal. Neither Cypress nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Cypress is willing to work with the customer who is concerned about the integrity of their code. Code protection is constantly evolving. We at Cypress are committed to continuously improving the code protection features of our products.

# Content Overview

|      | -   | A: Overview                         | 13  |

|------|-----|-------------------------------------|-----|

|      | 1.  | Pin Information                     |     |

| Sect | ion | B: PSoC Core                        | 25  |

|      | 2.  | CPU Core (M8C)                      |     |

| ć    | 3.  | Supervisory ROM (SROM)              |     |

| 4    | 4.  | RAM Paging                          |     |

| Į    | 5.  | Interrupt Controller                |     |

| (    | 6.  | General Purpose I/O (GPIO)          |     |

| -    | 7.  | System Performance Controller (SPC) |     |

| 8    | 8.  | Internal Main Oscillator (IMO)      |     |

| ę    | 9.  | Internal Low Speed Oscillator (ILO) |     |

|      | 10. | External Crystal Oscillator (ECO)   | 73  |

|      | 11. | Sleep and Watchdog                  | 77  |

| Cast |     | C: CapSense <sup>®</sup> System     | 07  |

|      |     | • •                                 | 87  |

|      |     | CapSense Module                     |     |

|      |     | I/O Analog Multiplexer              |     |

|      | 14. | Comparators                         |     |

| Sect | ion | D: System Resources                 | 113 |

|      | 15. | Digital Clocks                      | 117 |

|      | 16. | I <sup>2</sup> C Slave              |     |

|      |     | System Resets                       |     |

|      |     | POR and LVD                         |     |

|      |     | SPI                                 |     |

|      |     | Programmable Timer                  |     |

| Seat | ion | E. Degistero                        | 171 |

|      |     | E: Registers                        |     |

|      |     | Register Reference                  |     |

| Sect | ion | F: Glossary                         | 263 |

| Inde | х   |                                     | 279 |

Contents Overview

#### PSoC® CY8C20xx7/S Technical Reference Manual, Document No. 001-74066 Rev. \*F

| 1.      | Pin Ir | nforma | ation      |                                                         | 19 |

|---------|--------|--------|------------|---------------------------------------------------------|----|

|         | 1.1    | Pinou  | ts         |                                                         | 19 |

|         |        | 1.1.1  |            | 237, CY8C20247/S PSoC 16-Pin SOIC (8K, 16K) Part Pinout |    |

|         |        | 1.1.2  |            | 237, CY8C20247/S 16-Pin QFN Part Pinout                 |    |

|         |        |        |            | 337, CY8C20347/S PSoC 24-Pin Part Pinout                |    |

|         |        | 1.1.4  |            | 437, CY8C20447/S, CY8C20467/S PSoC 32-Pin Part Pinout   |    |

|         |        | 1.1.5  |            | 637, CY8C20647/S, CY8C20667/S PSoC 48-Pin Part Pinout   |    |

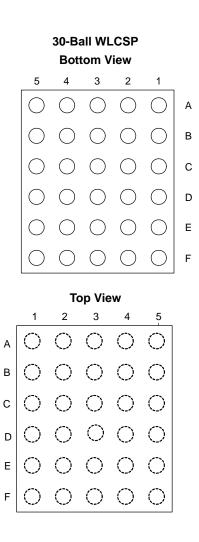

|         |        | 1.1.6  |            | 747, CY8C20767 PSoC 30-Ball Part Pinout                 |    |

| Section | B: PS  | oC Co  | re         |                                                         | 25 |

| 2.      | CPU    | Core ( | M8C)       |                                                         | 29 |

|         | 2.1    | -      | -          |                                                         | -  |

|         | 2.1    |        |            | ۶                                                       |    |

|         | 2.2    |        |            | 5                                                       |    |

|         | 2.4    |        |            | Summary                                                 |    |

|         | 2.5    |        |            | ats                                                     |    |

|         | 2.0    | 2.5.1  |            | e Instructions                                          |    |

|         |        | 2.5.2  |            | Instructions                                            |    |

|         |        | 2.5.3  |            | /te Instructions                                        |    |

|         | 2.6    | Regis  |            | ons                                                     |    |

|         |        | 2.6.1  | CPU_F F    | Register                                                | 34 |

|         |        | 2.6.2  | Related F  | Registers                                               | 34 |

| 3.      | Supe   | rvisor | y ROM (    | SROM)                                                   | 35 |

|         | 3.1    | Archit | ectural De | scription                                               | 35 |

|         |        | 3.1.1  |            | al SROM Feature                                         |    |

|         |        | 3.1.2  | SROM F     | unction Descriptions                                    | 36 |

|         |        |        | 3.1.2.1    | SWBootReset Function                                    | 36 |

|         |        |        | 3.1.2.2    | ReadBlock Function                                      | 37 |

|         |        |        | 3.1.2.3    | WriteBlock Function                                     | 37 |

|         |        |        | 3.1.2.4    | EraseBlock Function                                     | 38 |

|         |        |        | 3.1.2.5    | ProtectBlock Function                                   | 38 |

|         |        |        | 3.1.2.6    | TableRead Function                                      |    |

|         |        |        | 3.1.2.7    | EraseAll Function                                       |    |

|         |        |        | 3.1.2.8    | Checksum Function                                       |    |

|         |        |        | 3.1.2.9    | Calibrate0 Function                                     |    |

|         |        |        |            | Calibrate1 Function                                     |    |

|         |        |        |            | WriteAndVerify Function                                 |    |

|         |        |        | 3.1.2.12   | HWBootReset Function                                    | 40 |

## Section A: Overview

Contents

13

|    | 3.2    | Register Definitions                   | 40 |

|----|--------|----------------------------------------|----|

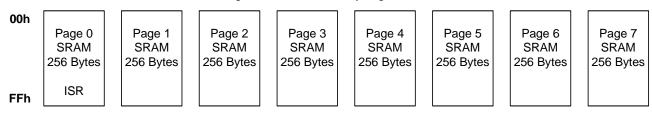

| 4. | RAM    | Paging                                 | 41 |

|    | 4.1    | Architectural Description              | 41 |

|    |        | 4.1.1 Basic Paging                     |    |

|    |        | 4.1.2 Stack Operations                 | 41 |

|    |        | 4.1.3 Interrupts                       |    |

|    |        | 4.1.4 MVI Instructions                 |    |

|    |        | 4.1.5 Current Page Pointer             |    |

|    |        | 4.1.6 Index Memory Page Pointer        |    |

|    | 4.2    | Register Definitions                   |    |

|    |        | 4.2.1 TMP_DRx Registers                |    |

|    |        | 4.2.2 CUR_PP Register                  |    |

|    |        | 4.2.3 STK_PP Register                  |    |

|    |        | 4.2.4 IDX_PP Register                  |    |

|    |        | 4.2.5 MVR_PP Register                  |    |

|    |        | 4.2.6 MVW_PP Register                  |    |

|    |        | 4.2.7 Related Registers                |    |

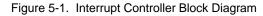

| 5. | Interi | rupt Controller                        | 47 |

|    | 5.1    | Architectural Description              |    |

|    | ••••   | 5.1.1 Posted versus Pending Interrupts |    |

|    | 5.2    | Application Overview                   |    |

|    | 5.3    | Register Definitions                   |    |

|    |        | 5.3.1 INT_CLR0 Register                |    |

|    |        | 5.3.2 INT_CLR1 Register                |    |

|    |        | 5.3.3 INT_CLR2 Register                |    |

|    |        | 5.3.4 INT_MSK0 Register                |    |

|    |        | 5.3.5 INT_MSK1 Register                |    |

|    |        | 5.3.6 INT_MSK2 Register                |    |

|    |        | 5.3.7 INT_SW_EN Register               |    |

|    |        | 5.3.8 INT_VC Register                  |    |

|    |        | 5.3.9 Related Registers                |    |

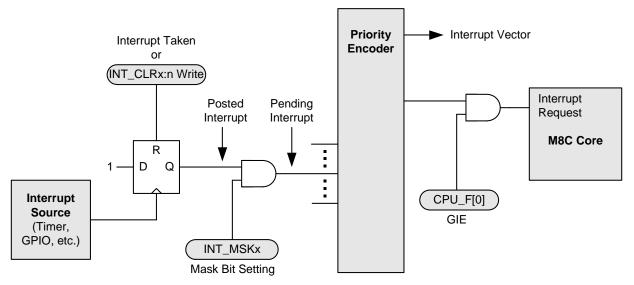

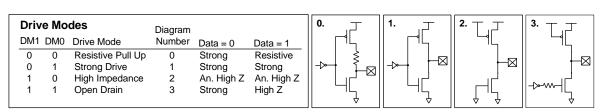

| 6. | Gene   | eral Purpose I/O (GPIO)                | 55 |

|    | 6.1    | Architectural Description              |    |

|    |        | 6.1.1 General Description              |    |

|    |        | 6.1.2 Digital I/O                      |    |

|    |        | 6.1.3 Analog and Digital Inputs        |    |

|    |        | 6.1.4 Port 1 Distinctions              |    |

|    |        | 6.1.5 Port 0 Distinctions              | 57 |

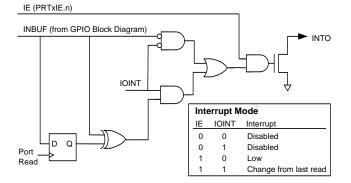

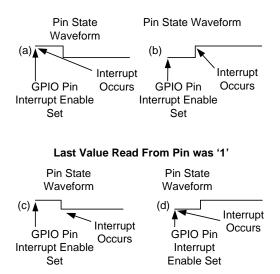

|    |        | 6.1.6 GPIO Block Interrupts            | 57 |

|    |        | 6.1.6.1 Interrupt Modes                | 57 |

|    |        | 6.1.7 Data Bypass                      |    |

|    | 6.2    | Register Definitions                   | 59 |

|    |        | 6.2.1 PRTxDR Registers                 | 59 |

|    |        | 6.2.2 PRTxIE Registers                 |    |

|    |        | 6.2.3 PRTxDMx Registers                |    |

|    |        | 6.2.4 IO_CFG1 Register                 | 61 |

|    |        | 6.2.5 IO_CFG2 Register                 | 61 |

|    |        |                                        |    |

| 7.  | Syste  | em Performance Controller (SPC)           | 63 |

|-----|--------|-------------------------------------------|----|

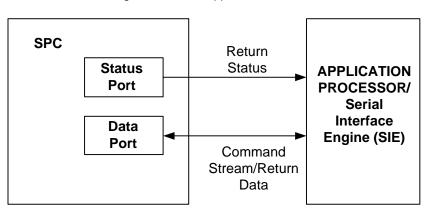

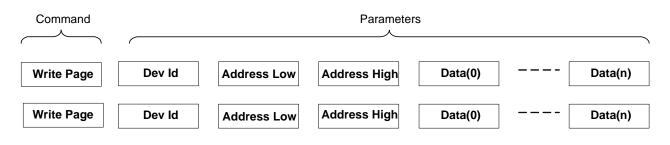

|     | 7.1    | Architectural Description                 | 63 |

|     | 7.2    | Application Overview                      |    |

|     |        | 7.2.1 Use of the Application Interface    |    |

|     |        | 7.2.2 Status Codes                        | 64 |

|     |        | 7.2.3 ADC User Module Usage               | 65 |

| 8.  | Intern | nal Main Oscillator (IMO)                 | 67 |

| •   | 8.1    | Architectural Description                 | -  |

|     | 8.2    | Application Overview                      |    |

|     | 0.2    | 8.2.1 Trimming the IMO                    |    |

|     |        | 8.2.2 Engaging Slow IMO                   |    |

|     | 8.3    | Register Definitions                      |    |

|     | 0.0    | 8.3.1 IMO_TR Register                     |    |

|     |        | 8.3.2 CPU_SCR1 Register                   |    |

|     |        | 8.3.3 OSC_CR2 Register                    |    |

|     |        | 8.3.4 Related Registers                   |    |

| _   | _      |                                           |    |

| 9.  |        | nal Low Speed Oscillator (ILO)            | 71 |

|     | 9.1    | Architectural Description                 |    |

|     | 9.2    | Register Definitions                      |    |

|     |        | 9.2.1 ILO_TR Register                     |    |

| 10. | Exter  | nal Crystal Oscillator (ECO)              | 73 |

|     | 10.1   | Architectural Description                 | 73 |

|     | 10.2   | •                                         |    |

|     | 10.3   | Register Definitions                      | 75 |

|     |        | 10.3.1 ECO_ENBUS Register                 | 75 |

|     |        | 10.3.2 ECO_TRIM Register                  | 75 |

|     |        | 10.3.3 ECO_CFG Register                   | 75 |

|     |        | 10.3.4 Related Registers                  |    |

|     | 10.4   | Usage Modes and Guidelines                | 76 |

| 11. | Sleep  | and Watchdog                              | 77 |

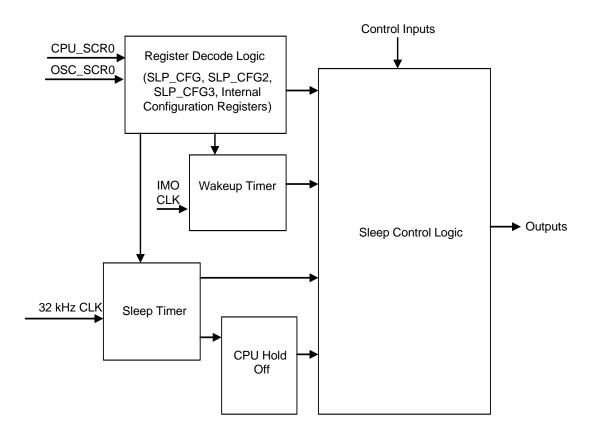

|     | 11.1   | Architectural Description                 |    |

|     |        | 11.1.1 Sleep Control Implementation Logic |    |

|     |        | 11.1.1.1 Wakeup Logic                     |    |

|     |        | 11.1.2 Sleep Timer                        |    |

|     | 11.2   | Application Overview                      |    |

|     |        | Register Definitions                      |    |

|     |        | 11.3.1 RES_WDT Register                   |    |

|     |        | 11.3.2 SLP_CFG Register                   |    |

|     |        | 11.3.3 SLP_CFG2 Register                  |    |

|     |        | 11.3.4 SLP_CFG3 Register                  |    |

|     |        | 11.3.5 Related Registers                  |    |

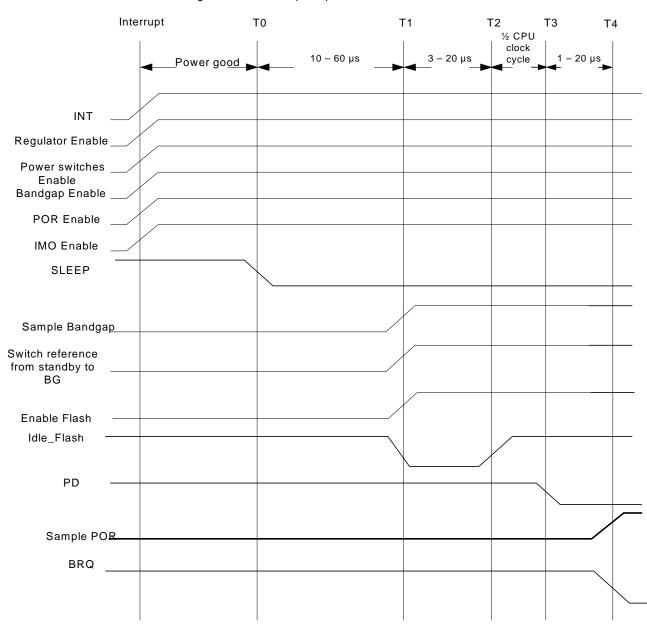

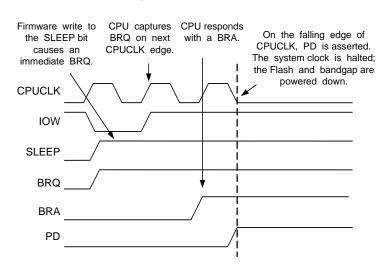

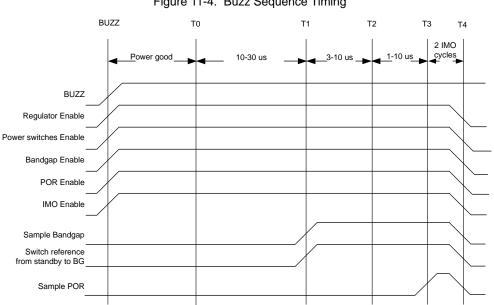

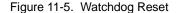

|     | 11.4   | Timing Diagrams                           | 83 |

|     |        | 11.4.1 Sleep Sequence                     |    |

|     |        | 11.4.2 Wakeup Sequence                    | 84 |

|     |        | 11.4.3 Bandgap Refresh                    |    |

|     |        | 11.4.4 Watchdog Timer                     |    |

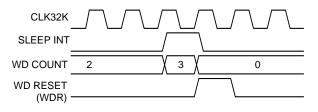

# Section C: CapSense<sup>®</sup> System

| 12. Ca     | apSense Module                       | 89  |

|------------|--------------------------------------|-----|

|            | 12.1 Architectural Description       |     |

|            | 12.1.1 Types of CapSense Approaches  |     |

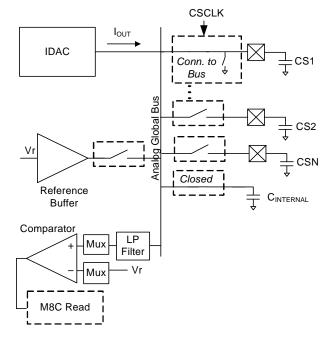

|            | 12.1.1.1 Positive Charge Integration |     |

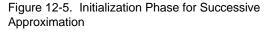

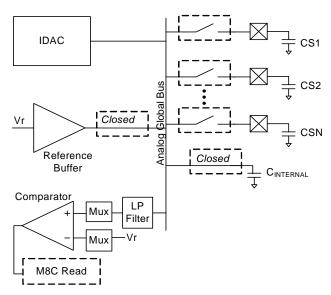

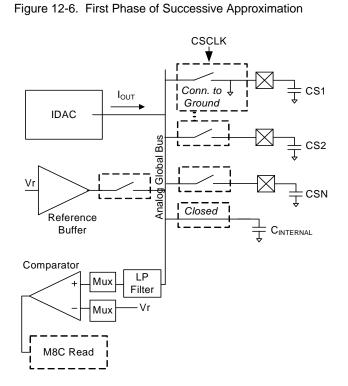

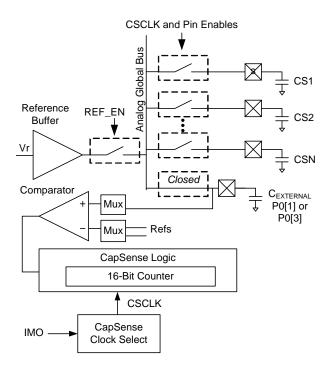

|            | 12.1.1.2 Successive Approximation    |     |

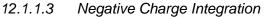

|            | 12.1.1.3 Negative Charge Integration |     |

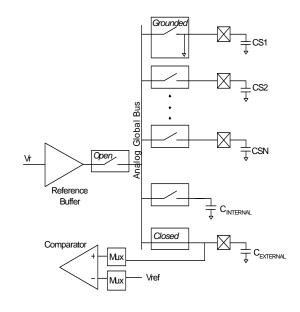

|            | 12.1.1.4 Sigma Delta                 |     |

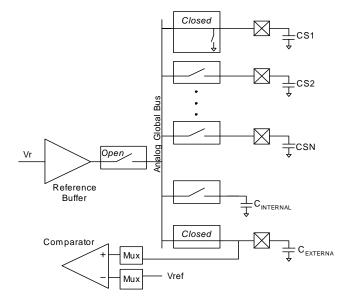

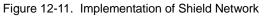

|            | 12.1.2 Shield support for CSD        |     |

|            | 12.1.3 IDAC                          |     |

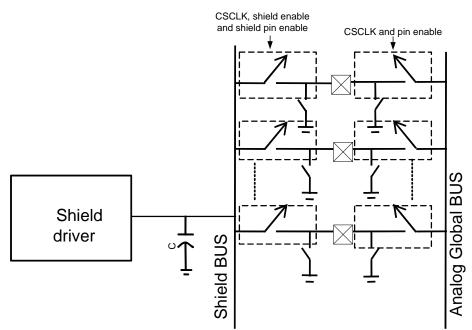

|            | 12.1.4 CapSense Counter              | 94  |

|            | 12.1.4.1 Operation                   |     |

|            | 12.2 Register Definitions            |     |

|            | 12.2.1 CS_CR0 Register               |     |

|            | 12.2.2 CS_CR1 Register               |     |

|            | 12.2.3 CS_CR2 Register               |     |

|            | 12.2.4 CS_CR3 Register               |     |

|            | 12.2.5 CS_CNTL Register              |     |

|            | 12.2.6 CS_CNTH Register              |     |

|            | 12.2.7 CS_STAT Register              |     |

|            | 12.2.8 CS_TIMER Register             |     |

|            | 12.2.9 CS_SLEW Register              |     |

|            | 12.2.10PRS_CR Register               |     |

|            | 12.2.11IDAC1_CODE Register           |     |

|            | 12.2.12IDAC0_CODE                    |     |

|            | 12.2.13IDAC_SHLD_DFT Register        |     |

|            | 12.2.14IDAC_BYPASS Register          |     |

|            | 12.2.15SHLD_CR Register              |     |

|            | 12.3 Timing Diagrams                 |     |

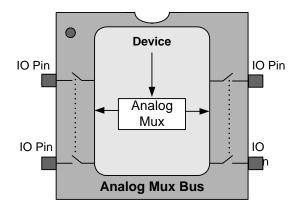

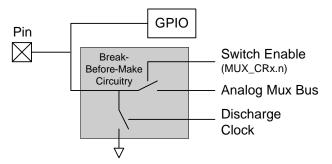

| 13. I/0    | O Analog Multiplexer                 | 105 |

|            | 13.1 Architectural Description       |     |

|            | 13.2 Register Definitions            |     |

|            | 13.2.1 MUX_CRx Registers             |     |

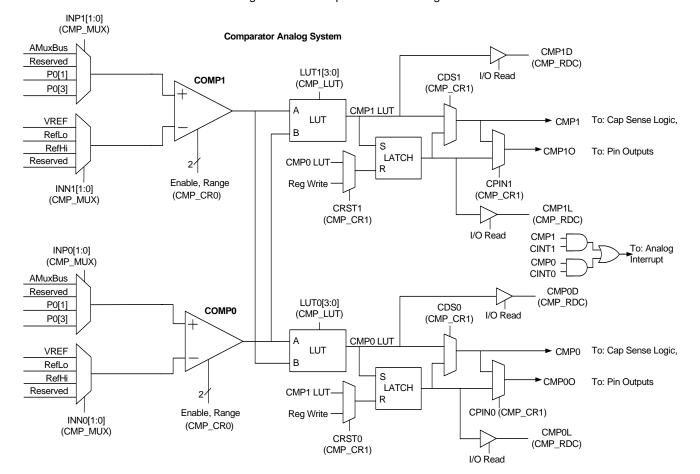

| 14. C      | omparators                           | 107 |

|            | 14.1 Architectural Description       | 107 |

|            | 14.2 Register Definitions            |     |

|            | 14.2.1 CMP_RDC Register              |     |

|            | 14.2.2 CMP_MUX Register              |     |

|            | 14.2.3 CMP_CR0 Register              |     |

|            | 14.2.4 CMP_CR1 Register              |     |

|            | 14.2.5 CMP_LUT Register              |     |

| Section D: | System Resources                     | 113 |

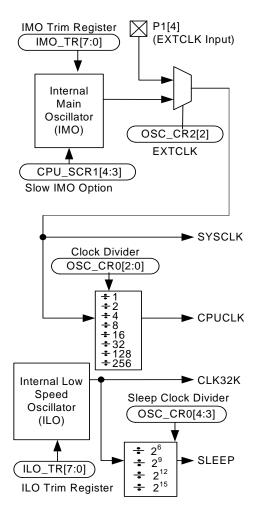

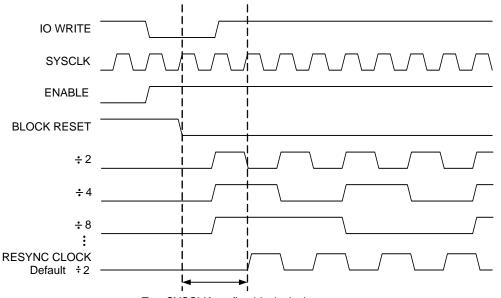

| 15. Di     | igital Clocks                        | 117 |

|            | 15.1 Architectural Description       |     |

|            | 15.1 Architectural Description       |     |

|            |                                      |     |

|            | 15.1.2 Internal Low Speed Oscillator |     |

|            |                                      |     |

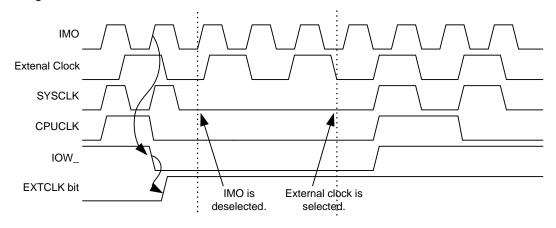

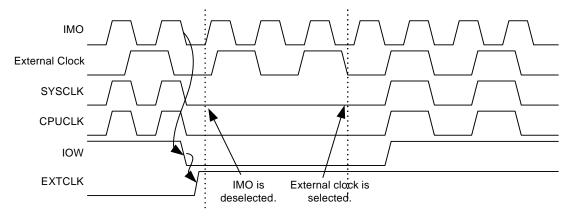

|      | 15.1.3 External Clock     |     |

|------|---------------------------|-----|

|      | 15.1.3.1 Switch Operation | 118 |

| 15.2 | Register Definitions      | 120 |

|      | 15.2.1 MISC_CR Register   |     |

|      | 15.2.2 OUT_P0 Register    |     |

|      | 15.2.3 OUT_P1 Register    | 120 |

|      | 15.2.4 OSC_CR0 Register   | 121 |

|      | 15.2.5 OSC_CR2 Register   | 122 |

|      | -                         |     |

| 16. I <sup>2</sup> C SI | ave                                                   | 123 |

|-------------------------|-------------------------------------------------------|-----|

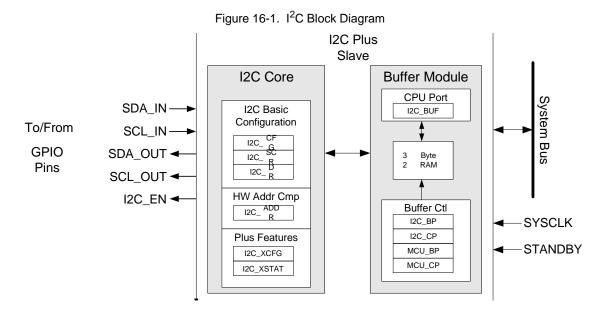

| 16.1                    | Architectural Description                             | 123 |

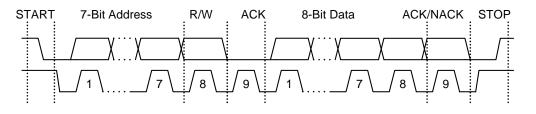

|                         | 16.1.1 Basic I <sup>2</sup> C Data Transfer           | 124 |

| 16.2                    | Application Overview                                  | 125 |

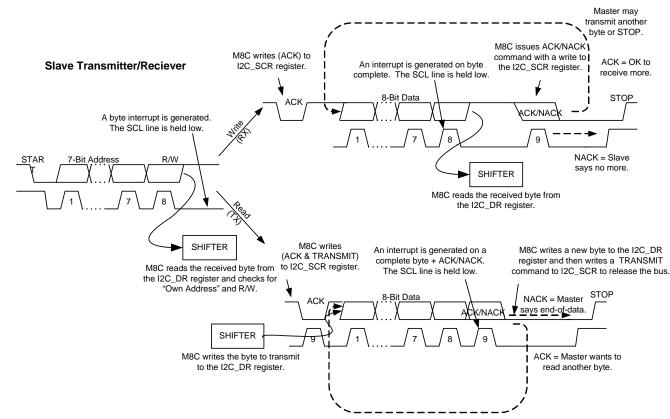

|                         | 16.2.1 Slave Operation                                | 125 |

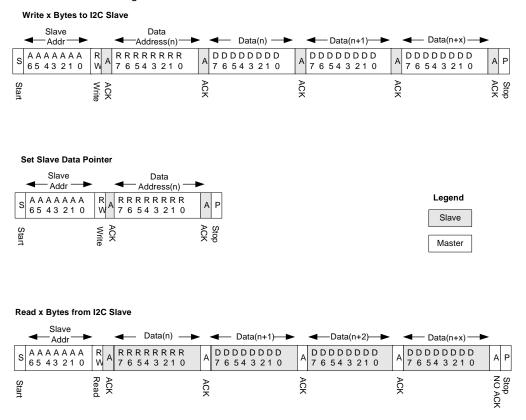

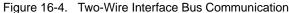

|                         | 16.2.2 EZI2C Mode                                     | 125 |

| 16.3                    | Register Definitions                                  | 129 |

|                         | 16.3.1 I2C_XCFG Register                              | 129 |

|                         | 16.3.2 I2C_XSTAT Register                             | 130 |

|                         | 16.3.3 I2C_ADDR Register                              | 131 |

|                         | 16.3.4 I2C_BP_EZ_CFG Register                         | 131 |

|                         | 16.3.5 I2C_CP Register                                | 131 |

|                         | 16.3.6 CPU_BP Register                                | 132 |

|                         | 16.3.7 CPU_CP Register                                | 132 |

|                         | 16.3.8 I2C_BUF Register                               | 132 |

|                         | 16.3.9 I2C_CFG Register                               | 133 |

|                         | 16.3.10I2C_SCR Register                               | 134 |

|                         | 16.3.11I2C_DR Register                                | 136 |

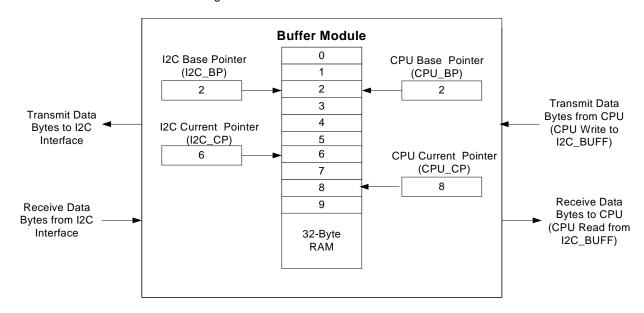

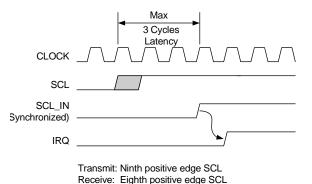

| 16.4                    | Timing Diagrams                                       | 137 |

|                         | 16.4.1 Clock Generation                               | 137 |

|                         | 16.4.2 Status Timing                                  | 138 |

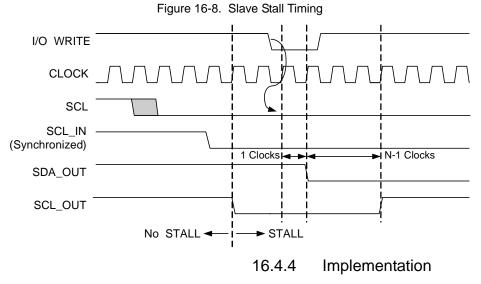

|                         | 16.4.3 Slave Stall Timing                             | 138 |

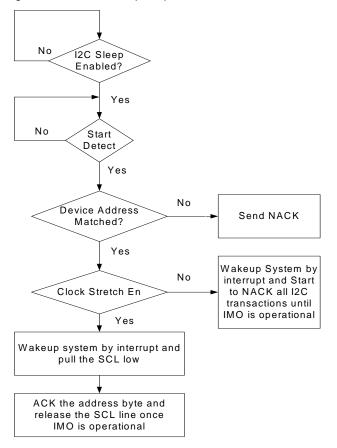

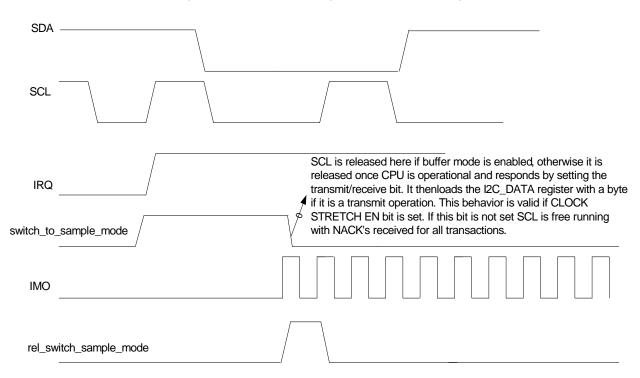

|                         | 16.4.4 Implementation                                 | 138 |

|                         | 16.4.4.1 Recommended I2C Implementation in Sleep Mode | 139 |

|                         | 16.4.5 Compatibility Mode Configuration               | 139 |

|                         |                                                       |     |

## 17. System Resets

### 141

|     |      | Architectural Description              |     |

|-----|------|----------------------------------------|-----|

|     | 17.2 | Pin Behavior During Reset              | 141 |

|     |      | 17.2.1 GPIO Behavior on Power Up       | 141 |

|     |      | 17.2.2 Powerup External Reset Behavior |     |

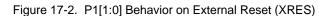

|     |      | 17.2.3 GPIO Behavior on External Reset |     |

|     | 17.3 | Register Definitions                   |     |

|     |      | 17.3.1 CPU_SCR1 Register               |     |

|     |      | 17.3.2 CPU_SCR0 Register               |     |

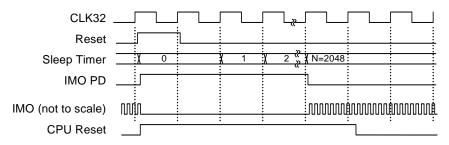

|     | 17.4 | Timing Diagrams                        |     |

|     |      | 17.4.1 Power On Reset                  |     |

|     |      | 17.4.2 External Reset                  |     |

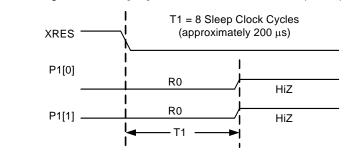

|     |      | 17.4.3 Watchdog Timer Reset            |     |

|     |      | 17.4.4 Reset Details                   |     |

|     | 17.5 | Power Modes                            | 148 |

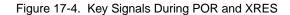

| 18. | POR  | and LVD                                | 149 |

|     | 18.1 | Architectural Description              |     |

|     | 18.2 | · · ·                                  |     |

|     |      |                                        |     |

|               | 18.2.1 VLT_CR Register                          |     |

|---------------|-------------------------------------------------|-----|

|               | 18.2.2 VLT_CMP Register                         | 151 |

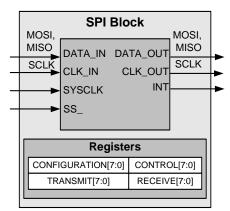

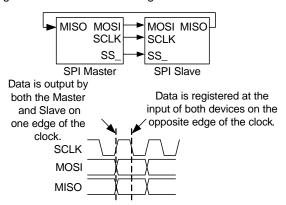

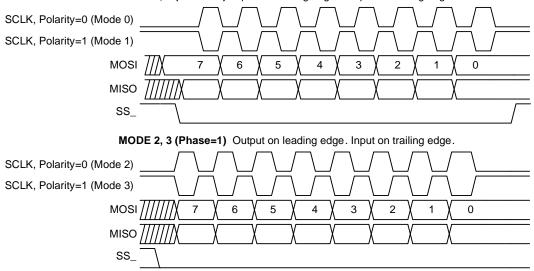

| 19. SPI       |                                                 | 153 |

| 19.1          | Architectural Description                       |     |

| 10.1          | 19.1.1 SPI Protocol Function                    |     |

|               | 19.1.1.1 SPI Protocol Signal Definitions        |     |

|               | 19.1.2 SPI Master Function                      |     |

|               | 19.1.2.1 Usability Exceptions                   |     |

|               | 19.1.2.2 Block Interrupt                        |     |

|               | 19.1.3 SPI Slave Function                       |     |

|               | 19.1.3.1 Usability Exceptions                   |     |

|               | 19.1.3.2 Block Interrupt                        |     |

|               | 19.1.4 Input Synchronization                    |     |

| 19.2          |                                                 |     |

|               | 19.2.1 SPI_TXR Register                         |     |

|               | 19.2.2 SPI_RXR Register                         |     |

|               | 19.2.2.1 SPI Master Data Register Definitions   |     |

|               | 19.2.2.2 SPI Slave Data Register Definitions    |     |

|               | 19.2.3 SPI_CR Register                          |     |

|               | 19.2.3.1 SPI Control Register Definitions       |     |

|               | 19.2.4 SPI_CFG Register                         |     |

|               | 19.2.4.1 SPI Configuration Register Definitions |     |

|               | 19.2.5 Related Registers                        |     |

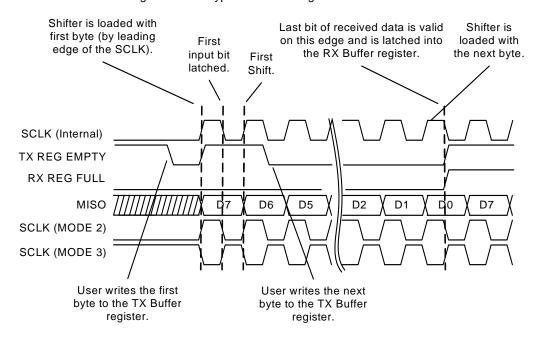

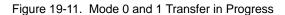

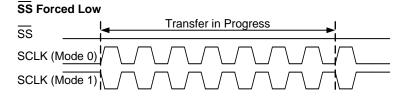

| 19.3          | Timing Diagrams                                 |     |

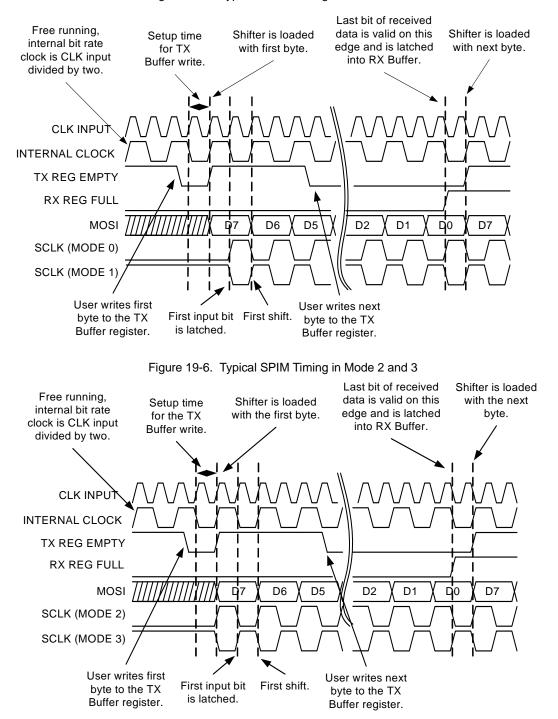

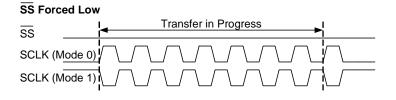

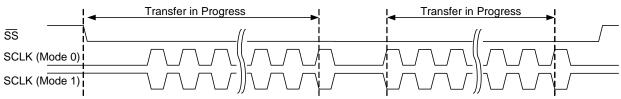

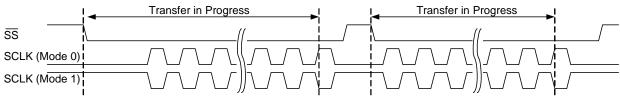

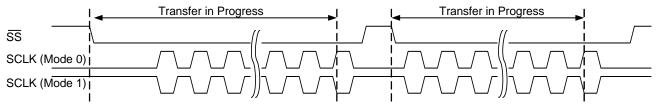

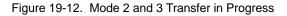

|               | 19.3.1 SPI Mode Timing                          |     |

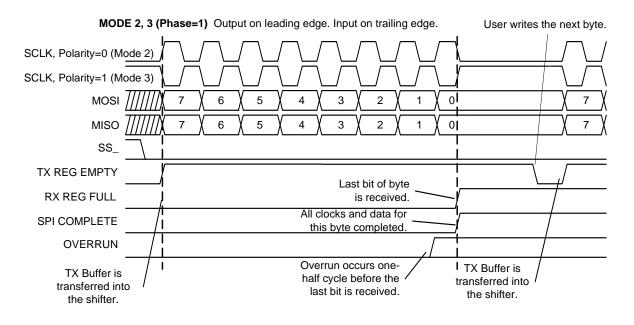

|               | 19.3.2 SPIM Timing                              |     |

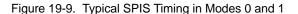

|               | 19.3.3 SPIS Timing                              |     |

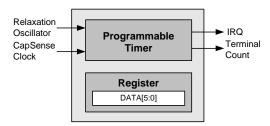

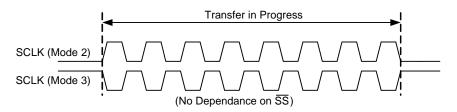

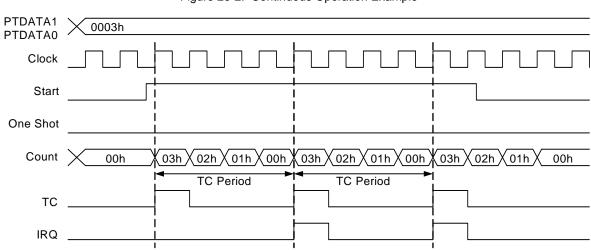

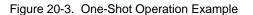

| 20. Progr     | rammable Timer                                  | 167 |

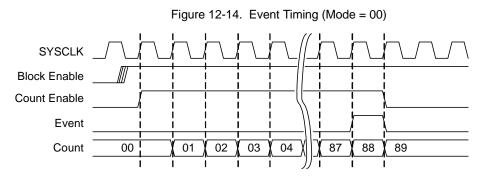

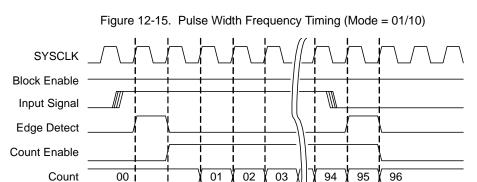

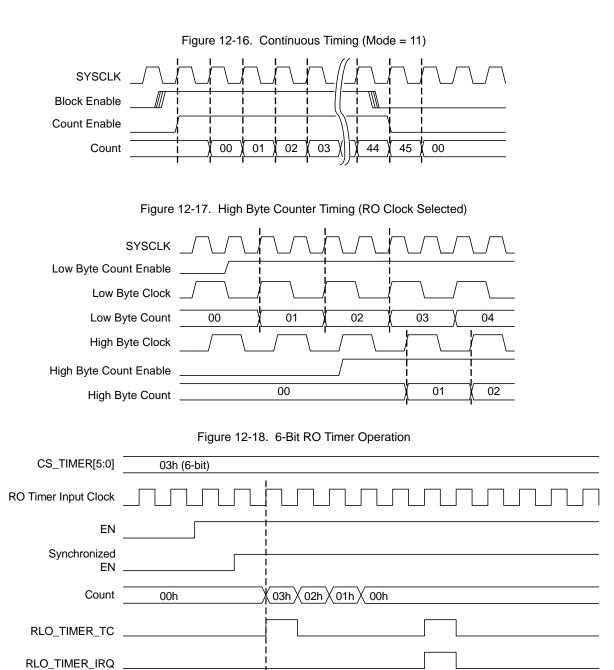

| •             | Architectural Description                       | 167 |

| 20.1          | 20.1.1 Operation                                |     |

| 20.2          | Register Definitions                            |     |

| 20.2          | 20.2.1 PT0_CFG Register                         |     |

|               | 20.2.2 PT1_CFG Register                         |     |

|               | 20.2.3 PT2_CFG Register                         |     |

|               | 20.2.4 PTx_DATA0 Register                       |     |

|               | 20.2.5 PTx_DATA1 Register                       |     |

| Section E: Re | gisters                                         | 171 |

| 21 Pogia      | stor Poforonco                                  | 175 |

| •             | Ster Reference                                  | 175 |

| 21.1          |                                                 |     |

|               | Register Conventions                            |     |

| 21.3          | Bank 0 Registers                                |     |

|               | 21.3.1 PRTxDR                                   |     |

|               | 21.3.2 PRTxIE                                   |     |

|               | 21.3.3 SPI_TXR                                  |     |

|               | 21.3.4 SPI_RXR                                  |     |

|               | 21.3.5 SPI_CR                                   |     |

|               | 21.3.6 IDAC0_CODE                               |     |

|               | 21.3.7 AMUX_CFG                                 |     |

|      | 21.3.8 CMP_RDC       |      |

|------|----------------------|------|

|      | 21.3.9 CMP_MUX       | .184 |

|      | 21.3.10CMP_CR0       | .185 |

|      | 21.3.11CMP CR1       | .186 |

|      | 21.3.12CMP_LUT       |      |

|      | 21.3.13CS CR0        |      |

|      | 21.3.14CS CR1        |      |

|      | 21.3.15CS CR2        |      |

|      | 21.3.16CS_CR2        |      |

|      |                      |      |

|      | 21.3.17CS_CNTL       |      |

|      | 21.3.18CS_CNTH       |      |

|      | 21.3.19CS_STAT       |      |

|      | 21.3.20CS_TIMER      |      |

|      | 21.3.21CS_SLEW       | .197 |

|      | 21.3.22PRS_CR        | .198 |

|      | 21.3.23PT0 CFG       | .199 |

|      | 21.3.24PTx DATA1     | .200 |

|      | 21.3.25PTx DATA0     |      |

|      | 21.3.26PT1 CFG       | -    |

|      | 21.3.27PT2 CFG       |      |

|      | 21.3.28I2C XCFG      |      |

|      | 21.3.29I2C_XCFG      | -    |

|      | _                    |      |

|      | 21.3.30I2C_ADDR      |      |

|      | 21.3.31I2C_BP_EZ_CFG |      |

|      | 21.3.32I2C_CP        |      |

|      | 21.3.33CPU_BP        |      |

|      | 21.3.34CPU_CP        |      |

|      | 21.3.35I2C_BUF       | .212 |

|      | 21.3.36CUR_PP        | .213 |

|      | 21.3.37STK PP        | .214 |

|      | 21.3.38IDX PP        | .215 |

|      | 21.3.39MVR PP        |      |

|      | 21.3.40MVW PP        |      |

|      | 21.3.41I2C CFG       |      |

|      | 21.3.42I2C SCR       |      |

|      | 21.3.43I2C DR        |      |

|      | —                    |      |

|      | 21.3.44INT_CLR0      |      |

|      |                      | .223 |

|      | 21.3.46INT_CLR2      |      |

|      | 21.3.47INT_MSK2      |      |

|      | 21.3.48INT_MSK1      |      |

|      | 21.3.49INT_MSK0      | .227 |

|      | 21.3.50INT_SW_EN     | .228 |

|      | 21.3.51INT_VC        | .229 |

|      | 21.3.52RES_WDT       | .230 |

|      | 21.3.53CPU_F         |      |

|      | 21.3.54IDAC1 CODE    |      |

|      | 21.3.55CPU_SCR1      |      |

|      | 21.3.56CPU_SCR0      |      |

| 01 A |                      |      |

| 21.4 | Bank 1 Registers     |      |

|      | 21.4.1 PRTxDM0       |      |

|      | 21.4.2 PRTxDM1       |      |

|      | 21.4.3 SPI_CFG       |      |

|      | 21.4.4 MISC_CR1      |      |

|      | 21.4.5 TMP_DRx       | .240 |

| 21.4.6 OUT_P0                     | 241 |

|-----------------------------------|-----|

| 21.4.6 OUT_P0<br>21.4.7 ECO_ENBUS |     |

| 21.4.8 ECO_TRIM                   |     |

| 21.4.9 MUX_CRx                    |     |

| 21.4.10IO_CFG1                    |     |

| 21.4.11OUT_P1                     |     |

| 21.4.12IO_CFG2                    |     |

| 21.4.13OSC_CR0                    |     |

| 21.4.14ECO_CFG                    |     |

| 21.4.15OSC_CR2                    |     |

| 21.4.16VLT_CR                     |     |

| 21.4.17VLT_CMP                    |     |

| 21.4.18IMO_TR                     |     |

| 21.4.19ILO_TR                     |     |

| 21.4.20SLP_CFG                    |     |

| 21.4.21SLP_CFG2                   |     |

| 21.4.22SLP_CFG3                   |     |

| 21.4.23SHLD_CR                    |     |

| 21.4.24IDAC_SHLD_DFT              |     |

| 21.4.25IDAC_BYPASS                |     |

|                                   |     |

# Section F: Glossary

Index

263

279

# Section A: Overview

The PSoC family consists of many Programmable System-on-Chip with On-Chip Controller devices. The CapSensePLUS CY8C20X37, CY8C20X47, and CY8C20X67 devices have fixed analog and digital resources in addition to a fast CPU, Flash program memory, and SRAM data memory to support various CapSense<sup>®</sup> algorithms.

For the most up-to-date ordering, pinout, packaging, or electrical specification information, refer to the datasheet. For the most current technical reference manual information and newest product documentation, go to the Cypress web site at http://www.cypress.com >> Documentation.

This section contains:

Pin Information on page 19.

# **Document Organization**

This manual is organized into sections and chapters, according to functionality. Each section contains a top-level architectural diagram and a register summary (if applicable). Most chapters within the sections have an introduction, an architectural/application description, register definitions, and timing diagrams. The sections are as follows:

- Overview Presents the top-level architecture, helpful information to get started, and document history and conventions. The PSoC device *pinouts* are detailed in the chapter Pin Information, on page 19.

- Core Describes the heart of the device in various chapters, beginning with an architectural overview and a summary list of registers pertaining to the core.

- CapSense System Describes the configurable PSoC CapSense system in various chapters, beginning with an architectural overview and a summary list of registers pertaining to the CapSense system.

- System Resources Presents additional system resources, beginning with an overview and a summary list of registers pertaining to system resources.

- Registers Lists all PSoC device registers in register mapping tables, and presents bit-level detail of each register in its own Register Reference chapter. Where applicable, detailed register descriptions are also located in each chapter.

- Glossary Defines the specialized terminology used in this manual. Glossary terms are presented in *bold, italic font* throughout this manual.

- Index Lists the location of key topics and elements that constitute and empower the devices.

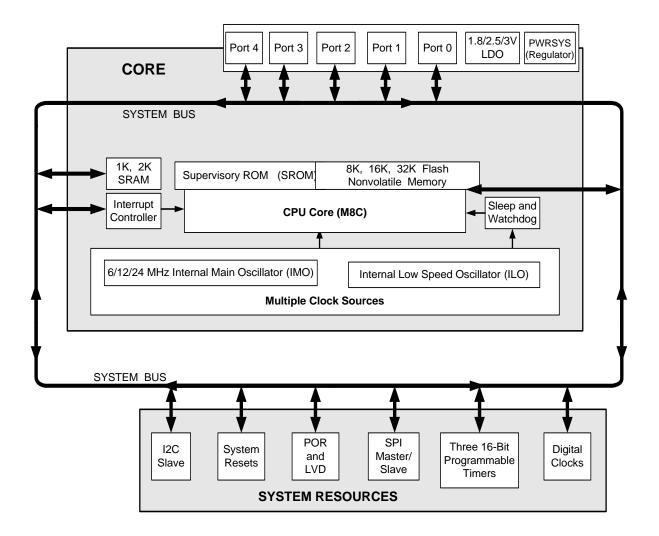

# **Top Level Architecture**

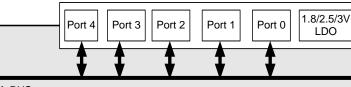

The PSoCblock diagram on the next page illustrates the toplevel architecture of the CapSensePLUS CY8C20X37, CY8C20X47, CY8C20X67devices. Each major grouping in the diagram is covered in this manual in its own section: PSoCCore, CapSense System, and the System Resources. Banding these three main areas together is the communication network of the system **bus**.

## **PSoCCore**

The PSoC Core is a powerful engine that supports a rich instruction set. It encompasses the **SRAM** for data storage, an *interrupt* controller for easy program execution to new addresses, sleep and watchdog timers, a regulated 3.0V output option is provided for Port 1 I/Os, and multiple *clock* sources that include the IMO (internal main oscillator) and ILO (internal low speed oscillator) for precision, programmable clocking.

The CPU core, called the M8C, is a powerful processor with speeds up to 24 MHz. The M8C is a four MIPS 8-*bit* Harvard architecture microprocessor. Within the CPU core are the **SROM** and **Flash** memory components that provide flexible programming.

PSoC GPIOs provide connection to the CPU and the CapSense resources of the device. Each pin's drive mode is selectable from four options, allowing great flexibility in external interfacing. Every pin also has the capability to generate a system interrupt on low level and change from last read.

## CapSense<sup>®</sup> System

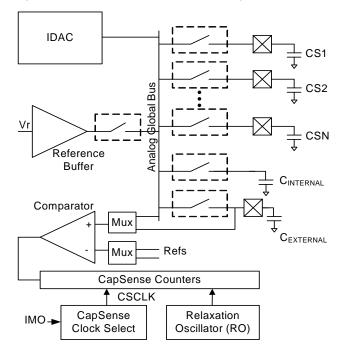

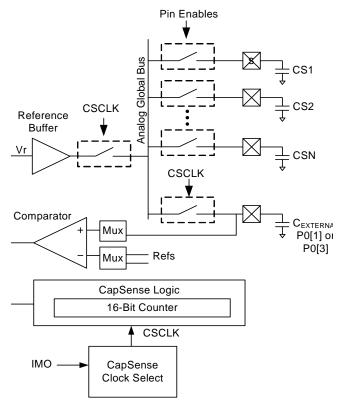

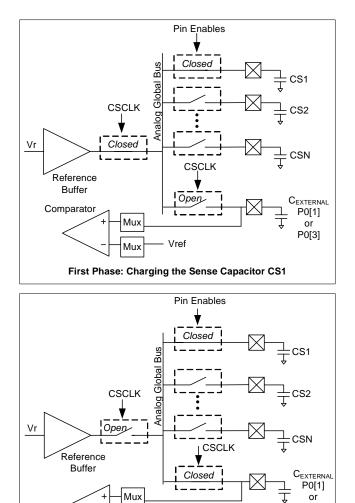

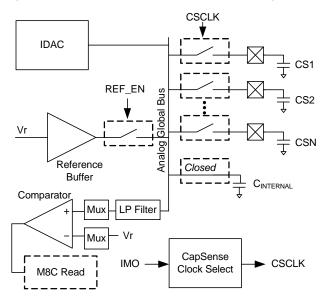

The CapSense System is composed of comparators, reference drivers, I/O multiplexers, and digital logic to support various capacitive sensing algorithms. Various reference selections are provided. Digital logic is mainly comprised of counters and timers.

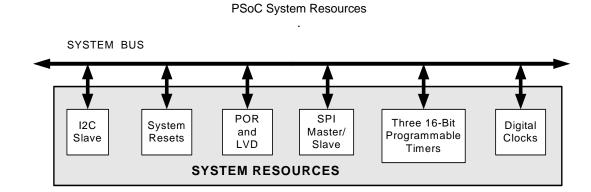

## System Resources

The System Resources provide additional PSoCcapability. These system resources include:

- Digital clocks to increase the flexibility of the PSoC programmable system-on-chip.

- I2C functionality with "no bus stalling."

- Various system resets supported by the M8C.

- Power-On-Reset (POR) circuit protection.

- SPI master and slave functionality.

- A programmable timer to provide periodic interrupts.

- Clock boost network providing a stronger signal to switches.

#### Top-Level Block Diagram

# **Getting Started**

The quickest path to understanding PSoC is by reading the datasheet and using PSoC Designer<sup>™</sup> Integrated Development Environment (IDE). This manual is useful for understanding the details of the PSoC integrated circuit.

**Important Note** For the most up-to-date Ordering, Packaging, or Electrical Specification information, refer to the individual PSoC device's datasheet or go to http://www.cypress.com.

### Support

Free support for PSoC products is available online at <a href="http://www.cypress.com">http://www.cypress.com</a>. Resources include Training Seminars, Discussion Forums, Application Notes, TightLink Technical Support Email/Knowledge Base, and Application Support Technicians.

Technical Support can be reached at http://www.cypress.com/support.

## Product Upgrades

Cypress provides scheduled upgrades and version enhancements for PSoC Designer free of charge. You can order the upgrades from your distributor on CD-ROM or download them directly from http://www.cypress.com under Software. Also provided are critical updates to system documentation under http://www.cypress.com >> Documentation.

## **Development Kits**

Development Kits are available from the following distributors: Digi-Key, Avnet, Arrow, and Future. The Cypress Online Store contains development kits, **C** compilers, and all accessories for PSoC development.

# **Document History**

This section serves as a chronicle of the PSoC® CY8C20xx7/S Family Technical Reference Manual.

| Version/<br>Release Date | Originator  | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **                       | SSTM        | New Technical Reference Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| *A                       | DST         | Added RO_TR Register, Updated I2C_XCFG Register on page 129, Updated EZI2C Mode on page 125.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| *В                       | DST         | Fixed typo in IDAC0_CODE, on page 181.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| *C                       | SSTM        | Updated Conditions for entering the sleep modes in Sleep Control Implementation Logic on page 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| *D                       | BVI         | Document name changes for consistency CY8C20xx7/S.<br>Corrected pinlist Description errors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| *E                       | SSTM        | Renamed RO_TR register as SHLD_CR register; replaced reference to the IDAC_D register with IDAC1_CODE. Added information on usage of external clock mode in External Clock on page 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| *F June 2015             | ASRI / RJVB | <ul> <li>a. Updated OSC_CR2 register in Core Register Summary on page 26.</li> <li>b. Updated the number of blocks per bank in Table 3-6 on page 37.</li> <li>c. Added explanation on BLOCKID parameter in Checksum Function on page 39.</li> <li>d. Updated description in Architectural Description on page 67.</li> <li>e. Updated OSC_CR2 register in System Resources Register Summary on page 114.</li> <li>f. Updated description in External Clock on page 118.</li> <li>g. Updated Figure 15-2, Figure 15-3, and description in Switch Operation on page 118.</li> <li>h. Updated description for OSC_CR2 Register on page 71, 124 and 253.</li> </ul> |

#### Technical Reference Manual History

## **Documentation Conventions**

There are only four distinguishing font types used in this manual, besides those found in the headings.

- The first is the use of *italics* when referencing a document title or file name.

- The second is the use of *bold italics* when referencing a term described in the Glossary of this manual.

- The third is the use of Times New Roman font, distinguishing equation examples.

- The fourth is the use of Courier New font, distinguishing code examples.

## **Register Conventions**

The following table lists the register conventions that are specific to this manual. A more detailed set of register conventions is located in the Register Reference chapter on page 175.

#### **Register Conventions**

| Convention                       | Example | Description                                                 |

|----------------------------------|---------|-------------------------------------------------------------|

| 'x' in a register<br>name        | PRTxIE  | Multiple instances/address ranges of the same register      |

| R                                | R : 00  | Read register or bit(s)                                     |

| W                                | W : 00  | Write register or bit(s)                                    |

| 0                                | RO : 00 | Only a read/write register or bit(s).                       |

| L                                | RL:00   | Logical register or bit(s)                                  |

| С                                | RC : 00 | Clearable register or bit(s)                                |

| 00                               | RW : 00 | Reset value is 0x00 or 00h                                  |

| ХХ                               | RW : XX | Register is not reset                                       |

| 0,                               | 0,04h   | Register is in bank 0                                       |

| 1,                               | 1,23h   | Register is in bank 1                                       |

| х,                               | x,F7h   | Register exists in register bank 0 and reg-<br>ister bank 1 |

| Empty, grayed-<br>out table cell |         | Reserved bit or group of bits, unless otherwise stated      |

## Numeric Naming

Hexadecimal numbers are represented with all letters in uppercase with an appended lowercase 'h' (for example, '14h' or '3Ah') and *hexadecimal* numbers may also be represented by a '0x' prefix, the *C* coding convention. Binary numbers have an appended lowercase 'b' (for example, 01010100b' or '01000011b'). Numbers not indicated by an 'h' or 'b' are *decimal*.

## Units of Measure

This table lists the units of measure used in this manual.

#### Units of Measure

| Symbol | Unit of Measure               |  |  |  |

|--------|-------------------------------|--|--|--|

| °C     | degrees Celsius               |  |  |  |

| dB     | decibels                      |  |  |  |

| fF     | femtofarads                   |  |  |  |

| Hz     | hertz                         |  |  |  |

| k      | kilo, 1000                    |  |  |  |

| к      | 2 <sup>10</sup> , 1024        |  |  |  |

| КВ     | 1024 bytes                    |  |  |  |

| Kbit   | 1024 bits                     |  |  |  |

| kHz    | kilohertz (32.000)            |  |  |  |

| kΩ     | kilohms                       |  |  |  |

| MHz    | megahertz                     |  |  |  |

| MΩ     | megaohms                      |  |  |  |

| μΑ     | microamperes                  |  |  |  |

| μF     | microfarads                   |  |  |  |

| μs     | microseconds                  |  |  |  |

| μV     | microvolts                    |  |  |  |

| μVrms  | microvolts root-mean-square   |  |  |  |

| mA     | milliamperes                  |  |  |  |

| ms     | milliseconds                  |  |  |  |

| mV     | millivolts                    |  |  |  |

| nA     | nanoampheres                  |  |  |  |

| ns     | nanoseconds                   |  |  |  |

| nV     | nanovolts                     |  |  |  |

| Ω      | ohms                          |  |  |  |

| pF     | picofarads                    |  |  |  |

| рр     | peak-to-peak                  |  |  |  |

| ppm    | parts per million             |  |  |  |

| sps    | samples per second            |  |  |  |

| σ      | sigma: one standard deviation |  |  |  |

| V      | volts                         |  |  |  |

## Acronyms

This table lists the acronyms that are used in this manual.

### Acronyms

| Acronym | Description                        |  |  |  |  |  |

|---------|------------------------------------|--|--|--|--|--|

| ABUS    | analog output bus                  |  |  |  |  |  |

| AC      | alternating current                |  |  |  |  |  |

| ADC     | analog-to-digital converter        |  |  |  |  |  |

| API     | Application Programming Interface  |  |  |  |  |  |

| BC      | broadcast clock                    |  |  |  |  |  |

| BR      | bit rate                           |  |  |  |  |  |

| BRA     | bus request acknowledge            |  |  |  |  |  |

| BRQ     | bus request                        |  |  |  |  |  |

| CBUS    | comparator bus                     |  |  |  |  |  |

| CI      | carry in                           |  |  |  |  |  |

| CMP     | compare                            |  |  |  |  |  |

| со      | carry out                          |  |  |  |  |  |

| CPU     | central processing unit            |  |  |  |  |  |

| CRC     | cyclic redundancy check            |  |  |  |  |  |

| СТ      | continuous time                    |  |  |  |  |  |

| DAC     | digital-to-analog converter        |  |  |  |  |  |

| DC      | direct current                     |  |  |  |  |  |

| DI      | digital or data input              |  |  |  |  |  |

| DMA     | direct memory access               |  |  |  |  |  |

| DO      | digital or data output             |  |  |  |  |  |

| ECO     | external crystal oscillator        |  |  |  |  |  |

| FB      | feedback                           |  |  |  |  |  |

| GIE     | global interrupt enable            |  |  |  |  |  |

| GPIO    | general purpose I/O                |  |  |  |  |  |

| ICE     | in-circuit emulator                |  |  |  |  |  |

| IDE     | integrated development environment |  |  |  |  |  |

| ILO     | internal low speed oscillator      |  |  |  |  |  |

| IMO     | internal main oscillator           |  |  |  |  |  |

| I/O     | input/output                       |  |  |  |  |  |

| IOR     | I/O read                           |  |  |  |  |  |

| IOW     | I/O write                          |  |  |  |  |  |

| IPOR    | imprecise power on reset           |  |  |  |  |  |

| IRQ     | interrupt request                  |  |  |  |  |  |

| ISR     | interrupt service routine          |  |  |  |  |  |

| ISSP    | in system serial programming       |  |  |  |  |  |

| IVR     | interrupt vector read              |  |  |  |  |  |

| LFSR    | linear feedback shift register     |  |  |  |  |  |

| LRb     | last received bit                  |  |  |  |  |  |

| LRB     | last received byte                 |  |  |  |  |  |

| LSb     | least significant bit              |  |  |  |  |  |

| LSB     | least significant byte             |  |  |  |  |  |

| LUT     | look-up table                      |  |  |  |  |  |

| MISO    | master-in-slave-out                |  |  |  |  |  |

| MOSI    | master-out-slave-in                |  |  |  |  |  |

| MSb     | most significant bit               |  |  |  |  |  |

| MSB     | most significant byte              |  |  |  |  |  |

| PC      | program counter                    |  |  |  |  |  |

### Acronyms (continued)

| Acronym | Description                           |  |  |  |

|---------|---------------------------------------|--|--|--|

| PCH     | program counter high                  |  |  |  |

| PCL     | program counter low                   |  |  |  |

| PD      | power down                            |  |  |  |

| PMA     | PSoC® memory arbiter                  |  |  |  |

| POR     | power on reset                        |  |  |  |

| PPOR    | precision power on reset              |  |  |  |

| PRS     | pseudo random sequence                |  |  |  |

| PSoC®   | Programmable System-on-Chip           |  |  |  |

| PSSDC   | power system sleep duty cycle         |  |  |  |

| PWM     | pulse width modulator                 |  |  |  |

| RAM     | random access memory                  |  |  |  |

| RETI    | return from interrupt                 |  |  |  |

| RO      | relaxation oscillator                 |  |  |  |

| ROM     | read only memory                      |  |  |  |

| RW      | read/write                            |  |  |  |

| SAR     | successive approximation register     |  |  |  |

| SC      | switched capacitor                    |  |  |  |

| SIE     | serial interface engine               |  |  |  |

| SE0     | single-ended zero                     |  |  |  |

| SOF     | start of frame                        |  |  |  |

| SP      | stack pointer                         |  |  |  |

| SPI     | serial peripheral interconnect        |  |  |  |

| SPIM    | serial peripheral interconnect master |  |  |  |

| SPIS    | serial peripheral interconnect slave  |  |  |  |

| SRAM    | static random access memory           |  |  |  |

| SROM    | supervisory read only memory          |  |  |  |

| SSADC   | single slope ADC                      |  |  |  |

| SSC     | supervisory system call               |  |  |  |

| тс      | terminal count                        |  |  |  |

| WDT     | watchdog timer                        |  |  |  |

| WDR     | watchdog reset                        |  |  |  |

| XRES    | external reset                        |  |  |  |

PERFORM

This chapter lists, describes, and illustrates all pins and pinout configurations for the CY8C20x67/S, CY8C20x47/S, and CY8C20x37/S PSoC devices. For up-to-date ordering, pinout, and packaging information, refer to the individual PSoC device's data sheet or go to http://www.cypress.com.

## 1.1 Pinouts

1.

The PSoC devices are available in a variety of packages. Every *port* pin (labeled with a "P"), except for *Vss*, *Vdd*, and XRES in the following tables and illustrations, is capable of Digital I/O.

## 1.1.1 CY8C20237, CY8C20247/S PSoC 16-Pin SOIC (8K, 16K) Part Pinout

| Pin | Туре    |        |                 |                                                                     |  |  |  |  |  |

|-----|---------|--------|-----------------|---------------------------------------------------------------------|--|--|--|--|--|

| No. | Digital | Analog | Name            | Description                                                         |  |  |  |  |  |

| 1   | I/O     | I      | P0[3]           | Integrating Input                                                   |  |  |  |  |  |

| 2   | I/O     | I      | P0[1]           | Integrating Input                                                   |  |  |  |  |  |

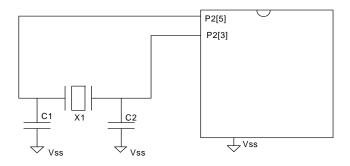

| 3   | I/O     | I      | P2[5]           | Crystal Output (XOut)                                               |  |  |  |  |  |

| 4   | I/O     | I      | P2[3]           | Crystal Input (XIn)                                                 |  |  |  |  |  |

| 5   | I/O     | 1      | P1[7]           | I <sup>2</sup> C SCL, SPISS                                         |  |  |  |  |  |

| 6   | I/O     | 1      | P1[5]           | I <sup>2</sup> C SDA, SPI MISO                                      |  |  |  |  |  |

| 7   | I/O     | I      | P1[3]           |                                                                     |  |  |  |  |  |

| 8   | I/O     | I      | P1[1]           | ISSP CLK <sup>1</sup> , I <sup>2</sup> C SCL, SPI MOSI              |  |  |  |  |  |

| 9   | Power   |        | V <sub>SS</sub> | Ground connection                                                   |  |  |  |  |  |

| 10  | I/O     | /O I   |                 | ISSP DATA <sup>1</sup> , I <sup>2</sup> C SDA, SPI CLK <sup>2</sup> |  |  |  |  |  |

| 11  | I/O     | I      | P1[2]           | Driven Shield Output (optional)                                     |  |  |  |  |  |

| 12  | I/O     | I      |                 | Optional external clock (EXTCLK)                                    |  |  |  |  |  |

| 13  | INPUT   |        | XRES            | Active high external reset with internal<br>pull-down               |  |  |  |  |  |

| 14  | I/O     | I      | P0[4]           |                                                                     |  |  |  |  |  |

| 15  | Power   |        | V <sub>DD</sub> | Supply voltage                                                      |  |  |  |  |  |

| 16  | I/O     | I      | P0[7]           |                                                                     |  |  |  |  |  |

**Pin Information**

#### Table 1-1. 16-Pin SOIC (8K, 16K) Part Pinout

#### CY8C20237, CY8C20247/S PSoC Device

|                                                     |   | $\bigcirc$ |    |                                                      |

|-----------------------------------------------------|---|------------|----|------------------------------------------------------|

| AI, P0[3] 🗖                                         | 1 |            | 16 | P0[7], AI                                            |

| AI, P0[1] 🗖                                         | 2 |            | 15 | Vod                                                  |

| AI, P2[5]                                           | 3 |            | 14 | P0[4], AI                                            |

| Al, P2[3] 🗖                                         | 4 | SOIC       | 13 | XRES                                                 |

| Al, P1[7] 🗖                                         | 5 | 3010       | 12 | P1[4], EXTCLK                                        |

| AI, P1[5] 🗖                                         | 6 |            | 11 | P1[2], AI                                            |

| Al, P1[3] 🗖                                         | 7 |            | 10 | P1[10], ISSP DATA, I <sup>2</sup> C SDA, SPI CLK, AI |

| AI, ISSP CLK, I <sup>2</sup> C SCL, SPI MOSI, P1[1] | 8 |            | 9  | Vss                                                  |

|                                                     | - |            |    |                                                      |

LEGEND A = Analog, I = Input, O = Output, OH = 5 mA High Output Drive, R = Regulated Output.

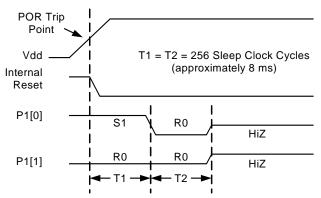

<sup>1</sup> On power-up, the SDA(P1[0]) drives a strong high for 256 sleep clock cycles and drives resistive low for the next 256 sleep clock cycles. The SCL(P1[1])line drives resistive low for 512 sleep clock cycles and both the pins transition to high impedance state. On reset, after XRES de-asserts, the SDA and the SCL lines drive resistive low for 8 sleep clock cycles and transition to high impedance state. Hence, during power-up or reset event, P1[1] and P1[0] may disturb the I2C bus. Use alternate pins if you encounter issues.

<sup>2</sup> Alternate SPI clock.

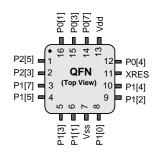

# 1.1.2 CY8C20237, CY8C20247/S 16-Pin QFN Part Pinout

| Pin | Туре     |        | Name  | Description                                        |  |  |

|-----|----------|--------|-------|----------------------------------------------------|--|--|

| No. | Digital  | Analog | Name  | Description                                        |  |  |

| 1   | 10       | I      | P2[5] | XTAL Out                                           |  |  |

| 2   | 10       | I      | P2[3] | XTAL In                                            |  |  |

| 3   | IOHR     | I      | P1[7] | I2C SCL, SPI SS                                    |  |  |

| 4   | IOHR     | I      | P1[5] | I2C SDA, SPI MISO                                  |  |  |

| 5   | IOHR     | I      | P1[3] | SPI CLK                                            |  |  |

| 6   | IOHR     | I      | P1[1] | TC CLK <sup>1</sup> , I2C SCL, SPI MOSI            |  |  |

| 7   | 7 Power  |        | Vss   | Ground pin                                         |  |  |

| 8   | IOHR     | I      | P1[0] | TC DATA <sup>1</sup> , I2C SDA, SPI CLK            |  |  |

| 9   | IOHR     | I      | P1[2] | Driven Shield Output (Optional)                    |  |  |

| 10  | IOHR     | I      | P1[4] | EXTCLK                                             |  |  |

| 11  | Inp      | out    | XRES  | Active high external reset with internal pull down |  |  |

| 12  | IOH      | I      | P0[4] |                                                    |  |  |

| 13  | 13 Power |        | Vdd   | Power pin                                          |  |  |

| 14  | IOH      | I      | P0[7] |                                                    |  |  |

| 15  | IOH      | I      | P0[3] | Integrating input                                  |  |  |

| 16  | IOH      | I      | P0[1] | Integrating input                                  |  |  |

#### Table 1-2. 16-Pin QFN/COL Part Pinout

#### CY8C20237, CY8C20247 Devices

LEGEND A = Analog, I = Input, O = Output, H = 5 mA High Output Drive, R = Regulated Output Option.

<sup>1</sup> These are the ISSP pins, which are not High Z at POR (Power On Reset).

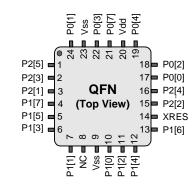

## 1.1.3 CY8C20337, CY8C20347/S PSoC 24-Pin Part Pinout

|  | Table 1-3. | 24-Pin ( | QFN Part | Pinout <sup>2</sup> |

|--|------------|----------|----------|---------------------|

|--|------------|----------|----------|---------------------|

| Pin | Ту      | ре         | Name  | Description                                        |  |  |  |

|-----|---------|------------|-------|----------------------------------------------------|--|--|--|

| No. | Digital | Analog     | Name  | •                                                  |  |  |  |

| 1   | 10      | I          | P2[5] | XTAL Out                                           |  |  |  |

| 2   | 10      | I          | P2[3] | XTAL In                                            |  |  |  |

| 3   | 10      | I          | P2[1] |                                                    |  |  |  |

| 4   | IOHR    | I          | P1[7] | I2C SCL, SPI SS                                    |  |  |  |

| 5   | IOHR    | I          | P1[5] | I2C SDA, SPI MISO                                  |  |  |  |

| 6   | IOHR    | I          | P1[3] | SPI CLK                                            |  |  |  |

| 7   | IOHR    | I          | P1[1] | TC CLK <sup>1</sup> , I2C SCL, SPI MOSI            |  |  |  |

| 8   |         |            | NC    | No connection                                      |  |  |  |

| 9   | Po      | wer        | Vss   | Ground pin                                         |  |  |  |

| 10  | IOHR    | I          | P1[0] | TC DATA <sup>1</sup> , I2C SDA, SPI CLK            |  |  |  |

| 11  | IOHR    | I          | P1[2] | Driven Shield Output (optional)                    |  |  |  |

| 12  | IOHR    | I          | P1[4] | EXTCLK                                             |  |  |  |

| 13  | IOHR    | Ι          | P1[6] |                                                    |  |  |  |

| 14  | Inj     | Input XRES |       | Active high external reset with internal pull down |  |  |  |

| 15  | ю       | Ι          | P2[2] | Driven Shield Output (optional)                    |  |  |  |

| 16  | IOH     | Ι          | P2[4] | Driven Shield Output (optional)                    |  |  |  |

| 17  | IOH     | I          | P0[0] | Driven Shield Output (optional)                    |  |  |  |

| 18  | IOH     | Ι          | P0[2] | Driven Shield Output (optional)                    |  |  |  |

| 19  | IOH     | Ι          | P0[4] |                                                    |  |  |  |

| 20  | Po      | wer        | Vdd   | Power pin                                          |  |  |  |

| 21  | IOH     | Ι          | P0[7] |                                                    |  |  |  |

| 22  | IOH     | I          | P0[3] | Input                                              |  |  |  |

| 23  | IOH     | I          | Vss   | Ground pin                                         |  |  |  |

| 24  | IOH     | I          | P0[1] | Integrating input                                  |  |  |  |

#### CY8C20337, CY8C20347/S PSoC Device

**LEGEND** A = Analog, I = Input, O = Output, H = 5 mA High Output Drive, R = Regulated Output Option.

- <sup>1</sup> These are the ISSP pins, which are not High Z at POR (Power On Reset).

- <sup>2</sup> The center pad on the QFN package must be connected to ground (Vss) for best mechanical, thermal, and electrical performance. If not connected to ground, it must be electrically floated and not connected to any other signal.

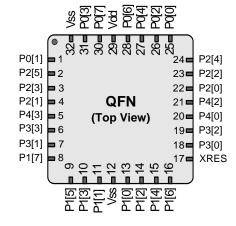

## 1.1.4 CY8C20437, CY8C20447/S, CY8C20467/S PSoC 32-Pin Part Pinout

#### Table 1-4. 32-Pin QFN Part Pinout<sup>2</sup>

| Pin<br>No. | Digital    | Analog     | Name  | Description                                        |  |

|------------|------------|------------|-------|----------------------------------------------------|--|

| 1          | IOH        | Ι          | P0[1] | Integrating input                                  |  |

| 2          | 10         | Ι          | P2[5] | Crystal output (XOut)                              |  |

| 3          | 10         | Ι          | P2[3] | Crystal input (XIn)                                |  |

| 4          | 10         | Ι          | P2[1] |                                                    |  |

| 5          | 10         | Ι          | P4[3] |                                                    |  |

| 6          | 10         | Ι          | P3[3] |                                                    |  |

| 7          | 10         | Ι          | P3[1] |                                                    |  |

| 8          | IOHR       | Ι          | P1[7] | I2C SCL, SPI SS                                    |  |

| 9          | IOHR       | Ι          | P1[5] | I2C SDA, SPI MISO                                  |  |

| 10         | IOHR       | Ι          | P1[3] | SPI CLK                                            |  |

| 11         | IOHR       | Ι          | P1[1] | TC CLK <sup>1</sup> , I2C SCL, SPI MOSI            |  |

| 12         | Pov        | ver        | Vss   | Ground pin                                         |  |

| 13         | IOHR       | Ι          | P1[0] | TC DATA <sup>1</sup> , I2C SDA, SPI CLK            |  |

| 14         | IOHR       | Ι          | P1[2] | Driven Shield Output (optional)                    |  |

| 15         | IOHR       | Ι          | P1[4] | EXTCLK                                             |  |

| 16         | IOHR       | Ι          | P1[6] |                                                    |  |

| 17         | Input XRES |            | XRES  | Active high external reset with internal pull down |  |

| 18         | 10         | IO I P3[0] |       |                                                    |  |

| 19         | 10         | Ι          | P3[2] |                                                    |  |

| 20         | 10         | -          | P4[0] |                                                    |  |

| 21         | 10         | -          | P4[2] |                                                    |  |

| 22         | 10         | -          | P2[0] |                                                    |  |

| 23         | 10         | -          | P2[2] | Driven Shield Output (optional)                    |  |

| 24         | IOH        | -          | P2[4] | Driven Shield Output (optional)                    |  |

| 25         | IOH        | Ι          | P0[0] | Driven Shield Output (optional)                    |  |

| 26         | IOH        | Ι          | P0[2] | Driven Shield Output (optional)                    |  |

| 27         | IOH        | Ι          | P0[4] |                                                    |  |

| 28         | IOH        | Ι          | P0[6] |                                                    |  |

| 29         | Pov        | ver        | Vdd   | Power pin                                          |  |

| 30         | IOH        | Ι          | P0[7] |                                                    |  |

| 31         | IOH        | Ι          | P0[3] | Integrating input                                  |  |

| 32         | Pov        | ver        | Vss   | Ground pin                                         |  |

#### CY8C20437, CY8C20447/S, CY8C20467/S Devices

LEGEND A = Analog, I = Input, O = Output, NC = No Connection, H = 5 mA High Output Drive, R = Regulated Output Option.

<sup>1</sup> These are the ISSP pins, which are not High Z at POR (Power On Reset).

<sup>2</sup> The center pad on the QFN package must be connected to ground (Vss) for best mechanical, thermal, and electrical performance. If not connected to ground, it must be electrically floated and not connected to any other signal.

# 1.1.5 CY8C20637, CY8C20647/S, CY8C20667/S PSoC 48-Pin Part Pinout

### Table 1-5. 48-Pin Part Pinout<sup>2</sup>

| Pin<br>No. | Digital | Analog   | Name  | Description                                        | CY8 | C206    | 37, C          |                               | 47/S, CY8C20667/S PSoC Devices                                     |

|------------|---------|----------|-------|----------------------------------------------------|-----|---------|----------------|-------------------------------|--------------------------------------------------------------------|

| 1          | -       | ٩        | NC    | No connection                                      |     |         |                | P0[<br>Vss<br>P0[             | NUC<br>NUC<br>NUC<br>Vdd<br>PO[6]<br>PO[4]<br>PO[2]                |

| 2          | 10      | 1        | P2[7] |                                                    |     |         | NO (           | 8 / 8                         | NC 33 33 40 47 47 47 47 47 47 47 47 47 47 47 47 47                 |

| 3          | 10      |          | P2[5] | XTAL Out                                           |     | -       |                |                               | 4 4 4 4 4 α α α α36 <b>E</b> NC<br>35 <b>E</b> P2[4]               |

| 4          | 10      | 1        | P2[3] | XTAL In                                            |     |         | 2[7]<br>2[5]   |                               | 33 <b>4 P</b> 2[4]<br>34 <b>4 P</b> 2[2]                           |

| 5          | IO      | Ι        | P2[1] |                                                    | 1   |         | 2[3]           |                               | 33 <b>=</b> P2[0]                                                  |

| 6          | Ю       | Ι        | P4[3] |                                                    |     |         | 2[1]           |                               | 32 <b>=</b> P4[2]                                                  |

| 7          | IO      | Ι        | P4[1] |                                                    | 1   |         | P4[3]          |                               | QFN 31 = P4[0]                                                     |

| 8          | Ю       | Ι        | P3[7] |                                                    | 1   |         | P4[1]          |                               | (Top View) 30 = P3[6]                                              |

| 9          | IO      | Ι        | P3[5] |                                                    |     |         | 23[7]<br>23[5] |                               | 29 <b>e</b> P3[4]<br>28 <b>e</b> P3[2]                             |

| 10         | IO      | Ι        | P3[3] |                                                    | 1   |         | 2[3]<br>23[3]  |                               | 20 <b>– – – – – – – – – –</b>                                      |

| 11         | IO      | Ι        | P3[1] |                                                    | 1   | F       | P3[1]          | <b>1</b> 1                    | 26 🖬 XRES                                                          |

| 12         | IOHR    | Ι        | P1[7] | I2C SCL, SPI SS                                    |     | F       | P1[7]          | ∎12 <u>ლ</u> <u>+</u> <u></u> | [6]P1[6]                                                           |

| 13         | IOHR    | Ι        | P1[5] | I2C SDA, SPI MISO                                  |     |         | U              |                               |                                                                    |

| 14         |         |          | NC    | No connection                                      |     |         |                | 1[5]<br>NC NC                 | P1[3]<br>VSS<br>NC<br>NC<br>NC<br>P1[0]<br>P1[2]<br>P1[2]<br>P1[2] |

| 15         |         |          | NC    | No connection                                      |     |         |                | д.                            |                                                                    |

| 16         | IOHR    | I        | P1[3] | SPI CLK                                            |     |         |                |                               |                                                                    |

| 17         | IOHR    | Ι        | P1[1] | TC CLK <sup>1</sup> , I2C SCL, SPI MOSI            |     |         |                |                               |                                                                    |

| 18         | Pow     | /er      | Vss   | Ground pin                                         |     |         |                |                               |                                                                    |

| 19         |         |          | NC    | No connection                                      |     |         |                |                               |                                                                    |

| 20         |         |          | NC    | No connection                                      |     |         |                |                               |                                                                    |

| 21         | Pow     | /er      | Vdd   | Power pin                                          |     |         |                |                               |                                                                    |

| 22         | IOHR    | Т        | P1[0] | TC DATA <sup>1</sup> , I2C SDA, SPI CLK            |     |         |                |                               |                                                                    |

| 23         | IOHR    | Ι        | P1[2] | Driven Shield Output (optional)                    |     |         |                |                               |                                                                    |

| 24         | IOHR    | Ι        | P1[4] | EXTCLK                                             |     |         |                |                               |                                                                    |

| 25         | IOHR    | Ι        | P1[6] |                                                    |     |         |                |                               |                                                                    |

| 26         | Inp     | ut       | XRES  | Active high external reset with internal pull down |     |         |                |                               |                                                                    |

| 27         | 10      | Ι        | P3[0] |                                                    |     |         |                |                               |                                                                    |

| 28         | 10      | Ι        | P3[2] |                                                    |     |         |                |                               |                                                                    |

| 29         | 10      | I        | P3[4] |                                                    |     |         |                |                               |                                                                    |

| 30         | IO      | I        | P3[6] |                                                    | Pin | a       | bo             |                               |                                                                    |

| 31         | IO      | I        | P4[0] |                                                    | No. | Digital | Analog         | Name                          | Description                                                        |

| 32         | IO      | I        | P4[2] |                                                    |     |         |                |                               |                                                                    |