#### **Datasheet**

**Trusted Platform Module**

Document release reference: Z8F80723108-A

## **Key features**

- Optimized TPM device for IoT and ICT applications

- Compliant with TCG TPM Library specification revision 1.59 and PC Client Platform TPM Profile (PTP) version 1.05

- PQC-protected firmware update mechanism

- Certifications:

- Common Criteria, level EAL4+, AVA\_VAN.4 (moderate) according to TCG PC Client TPM Protection Profile (targeted) (9 October 2024) Certificate number CC-1245

- FIPS 140-2 Level 2 (7 April 2023) Certificate Number 4467

- I2C interface (using clock stretching)

- Random Number Generator (RNG) implemented according to NIST SP 800-90A using entropy source according to NIST SP 800-90B

- Provisioned with 4 Endorsement Keys (EK) and EK certificates (RSA 2048, RSA 3072, ECC NIST P256, ECC NIST P384)

- Enhanced (-40°C .. +85°C) or extended (-40°C .. +105°C) temperature range

- PG-UQFN-32-1,-2 package

- Optimized for battery operated devices: low standby power consumption (typ. 120 μA)

- 24 PCRs (SHA-1, SHA-256 or SHA384)

- 51 kByte NV memory

- Unlimited amount of NV counters (only depending on NV memory utilization)

- Up to 3 loaded sessions (TPM PT HR LOADED MIN)

- Up to 64 active sessions (TPM\_PT\_ACTIVE\_SESSIONS\_MAX)

- Up to 3 loaded transient Objects (TPM PT HR TRANSIENT MIN)

- Up to 7 loaded persistent Objects (TPM PT HR PERSISTENT MIN)

- · Pre-generation of up to 7 RSA key pairs

- RSA (1024, 2048, 3072 and 4096 bit)

- ECC (NIST P256, NIST P384, BN P256)

- SHA-1, SHA-256, SHA-384

- AES-128, AES-192, AES-256

#### **Product validation**

Qualified for applications according to the test conditions in the relevant tests of JEDEC JESD22 and J-STD-020.

# **Ordering information**

| Device name           | Package         | Remarks                                  |

|-----------------------|-----------------|------------------------------------------|

| SLB 9673XU2.0 FW26.xx | PG-UQFN-32-1,-2 | Enhanced temperature range -40°C - 85°C  |

| SLB 9673AU2.0 FW26.xx | PG-UQFN-32-1,-2 | Extended temperature range -40°C - 105°C |

#### **Datasheet**

#### **About this document**

# **About this document**

## **Scope and purpose**

This datasheet describes the SLB 9673 TPM 2.0 FW26.xx Trusted Platform Module together with its features, functionality and programming interface.

#### **Intended audience**

This datasheet is primarily intended for system developers.

## **Datasheet**

## **Table of contents**

## **Table of contents**

|           | Product validation                        | 1  |

|-----------|-------------------------------------------|----|

|           | Ordering information                      | 1  |

|           | About this document                       |    |

|           | Table of contents                         | 3  |

|           | List of tables                            | 5  |

|           | List of figures                           | 7  |

| 1         | Introduction                              | 8  |

| 1.1       | Product description                       |    |

| 1.2       | Power management                          |    |

| 1.3       | Device address and clock stretching       | 8  |

| 2         | Delivery forms and ordering               |    |

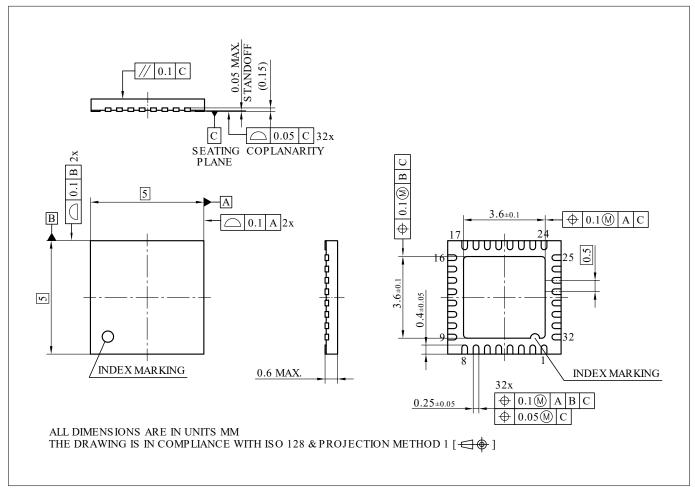

| 2.1       | Package dimensions (UQFN)                 |    |

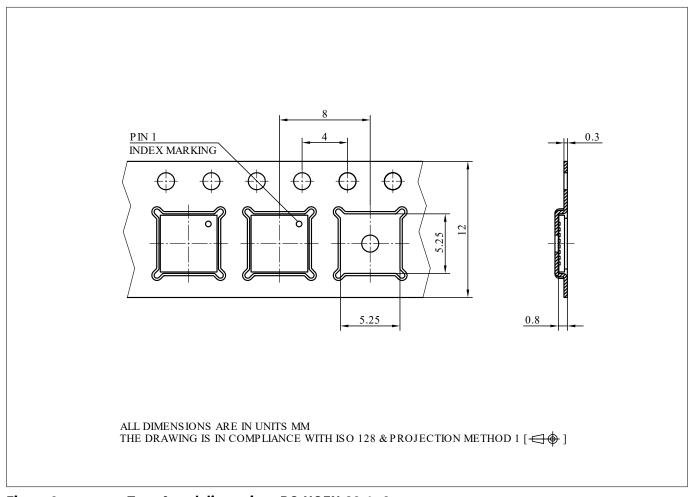

| 2.1.1     | Packing type                              |    |

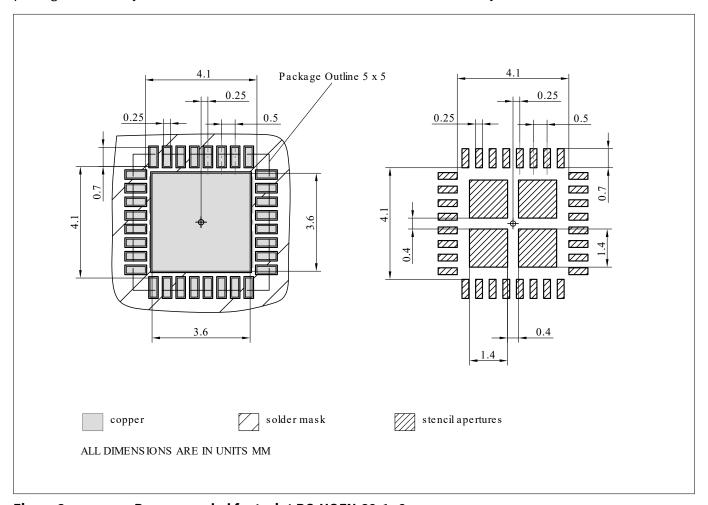

| 2.1.2     | Recommended footprint                     | 11 |

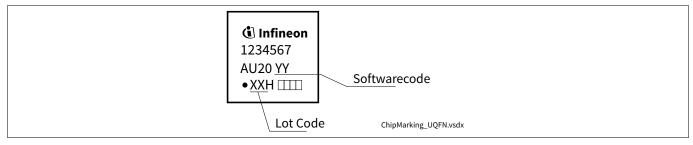

| 2.1.3     | Chip marking                              |    |

| 2.2       | Ordering information                      |    |

| 3         | Solution details                          | 13 |

| 3.1       | Hardware                                  | 13 |

| 3.1.1     | Electrical characteristics                | 13 |

| 3.1.1.1   | Absolute maximum ratings                  | 13 |

| 3.1.1.2   | Functional operating range                | 13 |

| 3.1.1.3   | DC characteristics                        | 14 |

| 3.1.1.4   | AC characteristics                        | 14 |

| 3.1.1.4.1 | I2C Interface Characteristics             | 15 |

| 3.1.1.5   | Timing                                    | 17 |

| 3.1.2     | Pin description                           | 17 |

| 3.1.3     | Typical schematic                         | 19 |

| 3.2       | TPM embedded software                     | 21 |

| 3.2.1     | Implemented algorithms                    | 21 |

| 3.2.2     | Available resources                       | 21 |

| 3.2.3     | Command ordinal list                      | 23 |

| 3.2.4     | Generation of RSA keys                    | 27 |

| 3.2.4.1   | Pre-generation of RSA keys                | 27 |

| 3.2.4.2   | Generation of RSA 3072- and 4096-bit keys | 27 |

| 3.2.5     | Non-volatile storage                      | 28 |

| 3.2.5.1   | Predefined NV indices                     | 28 |

| 3.2.6     | Vendor-specific functionality             | 29 |

## **Datasheet**

## Table of contents

| 3.2.6.1    | Power saving mode                    | 29 |

|------------|--------------------------------------|----|

| 3.2.6.2    | TPM and vendor properties            | 29 |

| 3.2.6.3    | Selftest operations                  | 31 |

| 3.2.6.3.1  | TPM2_SelfTest                        | 31 |

| 3.2.6.3.2  | TPM2_FullFipsSelfTestVendor          | 31 |

| 3.2.6.3.3  | TPM2_GetTestResult                   | 31 |

| 3.2.6.4    | Dictionary attack default values     | 32 |

| 3.2.6.5    | RSA signing scheme                   | 33 |

| 3.2.6.6    | NV index attribute TPMA_NV_WRITTEN   | 33 |

| 3.2.6.7    | Allocation of PCR banks              | 33 |

| 3.2.6.8    | General purpose I/O (GPIO)           | 33 |

| 3.2.6.8.1  | TPM2_NV_DefineSpace                  | 33 |

| 3.2.6.8.2  | TPM2_NV_Write                        | 34 |

| 3.2.6.8.3  | TPM2_NV_Read                         | 34 |

| 3.2.6.8.4  | TPM2_NV_UndefineSpace                | 34 |

| 3.2.6.9    | TPM2_SetCapabilityVendor             | 34 |

| 3.2.6.10   | Field upgrade                        | 36 |

| 3.2.6.10.1 | Structures and definitions           | 36 |

| 3.2.6.10.2 | TPM2B_MAX_BUFFER_VENDOR              | 36 |

| 3.2.6.10.3 | TPML_MAX_BUFFER                      | 36 |

| 3.2.6.10.4 | Commands in TPM operational mode     | 37 |

| 3.2.6.10.5 | Commands in TPM firmware update mode | 39 |

| 3.2.7      | TPM unique identifier                | 42 |

| 3.2.8      | NACK handling                        | 42 |

| 3.2.9      | TPM register polling                 | 42 |

| 3.2.10     | Configuration of I2C device address  | 43 |

| 3.2.11     | Reset timing                         | 44 |

| 3.2.12     | Firmware version mapping             | 45 |

| 4          | Licenses and notices                 | 46 |

|            | References                           | 47 |

|            | Revision history                     | 48 |

|            | D. 1.                                | 40 |

## **Datasheet**

## List of tables

## **List of tables**

| Table 1  | Sales order code                                                            | 12 |

|----------|-----------------------------------------------------------------------------|----|

| Table 2  | Absolute maximum ratings                                                    | 13 |

| Table 3  | Functional operating range                                                  | 13 |

| Table 4  | Current consumption                                                         | 14 |

| Table 5  | DC characteristics of I2C interface pins (SCL, SDA, TEST#, RST#, I2C_PIRQ#) | 14 |

| Table 6  | DC characteristics of GPIO pins                                             | 14 |

| Table 7  | Power supply                                                                | 15 |

| Table 8  | Device reset                                                                | 15 |

| Table 9  | I2C Standard Mode Interface Characteristics                                 | 15 |

| Table 10 | I2C Fast Mode Interface Characteristics                                     | 16 |

| Table 11 | I2C Fast Mode plus Interface Characteristics                                | 16 |

| Table 12 | Buffer types                                                                | 17 |

| Table 13 | I/O Signals                                                                 | 18 |

| Table 14 | Power supply                                                                | 18 |

| Table 15 | Not connected                                                               | 19 |

| Table 16 | Implemented algorithms                                                      | 21 |

| Table 17 | Available resources                                                         | 21 |

| Table 18 | Command code list                                                           |    |

| Table 19 | Vendor-specific TPM_CC constants                                            | 25 |

| Table 20 | Predefined NV indices                                                       | 28 |

| Table 21 | Attributes of predefined NV indices                                         | 28 |

| Table 22 | Infineon TPM property values                                                | 29 |

| Table 23 | Infineon vendor-specific property constants                                 |    |

| Table 24 | Infineon vendor-specific property values                                    | 30 |

| Table 25 | TPM operation modes                                                         | 30 |

| Table 26 | FIFO configuration registers                                                | 31 |

| Table 27 | TPM_RID register value description                                          | 31 |

| Table 28 | Incoming operands and sizes                                                 | 31 |

| Table 29 | Outgoing operands and sizes                                                 |    |

| Table 30 | TPM2_SelfTest bit mapping of TPM2_SelfTest                                  |    |

| Table 31 | TPM2_SelfTest bit mapping of TPM2_FullFipsSelfTestVendor                    |    |

| Table 32 | TPM2_SelfTest result                                                        |    |

| Table 33 | Mapping of GPIO indices                                                     |    |

| Table 34 | Default capability settings                                                 |    |

| Table 35 | Incoming operands and sizes                                                 |    |

| Table 36 | Outgoing operands and sizes                                                 |    |

| Table 37 | Error return codes                                                          |    |

| Table 38 | TPM2B_MAX_BUFFER_VENDOR structure definition                                |    |

| Table 39 | TPML_MAX_BUFFER structure definition                                        |    |

| Table 40 | Incoming operands and sizes                                                 |    |

| Table 41 | Outgoing operands and sizes                                                 |    |

| Table 42 | Error return codes                                                          |    |

| Table 43 | Incoming operands and sizes                                                 | 38 |

## **Datasheet**

## List of tables

| Table 44 | Outgoing operands and sizes                           |    |

|----------|-------------------------------------------------------|----|

| Table 45 | Error return codes                                    |    |

| Table 46 | Incoming operands and sizes                           | 39 |

| Table 47 | Outgoing operands and sizes                           |    |

| Table 48 | Error return codes                                    |    |

| Table 49 | Incoming operands and sizes                           | 40 |

| Table 50 | Outgoing operands and sizes                           |    |

| Table 51 | Error return codes                                    |    |

| Table 52 | Incoming operands and sizes                           | 40 |

| Table 53 | Outgoing operands and sizes                           | 40 |

| Table 54 | Error return codes                                    |    |

| Table 55 | Incoming operands and sizes                           | 41 |

| Table 56 | Outgoing operands and sizes                           |    |

| Table 57 | TPM2_GetTestResult bit mapping in TPM firmware update |    |

| Table 58 | Definition of the firmware version fields             |    |

| Table 59 | Mapping of the firmware versions                      |    |

## **Datasheet**

**List of figures**

# List of figures

| Figure 1 | Package dimensions PG-UQFN-32-1,-2                                 | . 9  |

|----------|--------------------------------------------------------------------|------|

| Figure 2 | Tape & reel dimensions PG-UQFN-32-1,-2                             | .10  |

| Figure 3 | Recommended footprint PG-UQFN-32-1,-2                              | 11   |

| Figure 4 | Chip marking                                                       | . 11 |

| Figure 5 | Reset timing                                                       | . 15 |

| Figure 6 | Pinout of the SLB 9673 TPM 2.0 (PG-UQFN-32-1,-2 package, top view) |      |

| Figure 7 | Typical schematic                                                  | . 20 |

#### **Datasheet**

#### 1 Introduction

## 1 Introduction

## 1.1 Product description

The SLB 9673 TPM 2.0 is a Trusted Platform Module. It is available in PG-UQFN-32-1,-2 package. It supports an I2C interface with a transfer rate of up to 1 MHz (typical). The SLB 9673 TPM 2.0 is compliant with TCG TPM Library specification revision 1.59 [1] and PC Client Platform TPM Profile (PTP) version 1.05 [2], including Errata (see [3] and [4]).

This TPM product is targeted to be certified, using the Common Criteria for Information Technology Security Evaluation (CC), Version 3.1 Rev.5, in the level EAL4+, AVA\_VAN.4 (moderate), ALC\_FLR.1 according to the Protection Profile PC Client Specific TPM, TPM Library Specification Family "2.0" Level 0 Revision 1.59 (CERTIFICATE <tbd>>1/2).

## 1.2 Power management

In the SLB 9673 TPM 2.0, power management is handled internally; no explicit power-down or standby mode is available. The device automatically enters a low-power state after each successful command/response transaction. If a transaction is started on the I2C bus from the host platform, the device will wake up immediately and will return to the low-power mode after the transaction has been finished.

## 1.3 Device address and clock stretching

The I2C interface uses 7-bit addressing. The default address of the device is 0x2E (also see [4]). The device uses clock stretching on the I2C interface (this implies that the I2C controller must support this).

Exact reference not yet available at document generation time

# infineon

2 Delivery forms and ordering

# 2 Delivery forms and ordering

The SLB 9673 TPM 2.0 product family features devices using an UQFN package.

## 2.1 Package dimensions (UQFN)

All dimensions are given in millimeters (mm) unless otherwise noted. The packages are "green" and RoHS compliant.

Figure 1 Package dimensions PG-UQFN-32-1,-2

## 2 Delivery forms and ordering

## 2.1.1 Packing type

PG-UQFN-32-1,-2: Tape & Reel (reel diameter 330mm), 5000 pcs. per reel

Figure 2 Tape & reel dimensions PG-UQFN-32-1,-2

# infineon

#### 2 Delivery forms and ordering

## 2.1.2 Recommended footprint

The figure below shows the recommended footprint for the PG-UQFN-32-1,-2 package. The exposed pad of the package is internally connected to GND. It shall be connected to GND externally as well.

Figure 3 Recommended footprint PG-UQFN-32-1,-2

# 2.1.3 Chip marking

Line 1: SLB 9673

Line 2: XU20 yy or AU20 yy (see Ordering information), the <yy> is an internal FW indication (only at manufacturing due to field upgrade option)

Line 3: <Lot number> H <datecode>

Figure 4 Chip marking

For details and recommendations regarding assembly of packages on PCBs, please refer to https://www.infineon.com/cms/en/product/packages/

## **Datasheet**

## 2 Delivery forms and ordering

# 2.2 Ordering information

## Table 1 Sales order code

| Sales code (Sales name/<br>Product) | Ordering code | Software code | Status       |

|-------------------------------------|---------------|---------------|--------------|

| SLB 9673AU2.0 FW26.00               | SP005676412   | 18            | Discontinued |

| SLB 9673XU2.0 FW26.00               | SP005676407   | 18            | Discontinued |

| SLB 9673AU2.0 FW26.10               | SP005722392   | 20            | Discontinued |

| SLB 9673XU2.0 FW26.10               | SP005722390   | 20            | Discontinued |

| SLB 9673XU2.0 FW26.13               | SP005919748   | 29            | Active       |

| SLB 9673AU2.0 FW26.13               | SP005919748   | 30            | Active       |

| SLB 9673XU2.0 FW26.24               | SP006026288   | 44            | Active       |

| SLB 9673AU2.0 FW26.24               | SP006026290   | 44            | Active       |

#### 3 Solution details

## 3 Solution details

#### 3.1 Hardware

#### 3.1.1 Electrical characteristics

This chapter lists the maximum and operating ranges for various electrical and timing parameters.

#### 3.1.1.1 Absolute maximum ratings

Table 2 Absolute maximum ratings

| Parameter                                                    | Symbol               | Values |      |      | Unit | Note or test condition                                   |

|--------------------------------------------------------------|----------------------|--------|------|------|------|----------------------------------------------------------|

|                                                              |                      | Min.   | Тур. | Max. |      |                                                          |

| Supply Voltage                                               | V <sub>DD</sub>      | -0.3   | _    | 4.1  | V    | -                                                        |

| Voltage on any pin                                           | V <sub>max</sub>     | -0.5   | _    | 4.1  | V    | -                                                        |

| Ambient temperature                                          | T <sub>A</sub>       | -40    | _    | 85   | °C   | Enhanced temperature<br>SLB 9673XU2.0 devices            |

| Ambient temperature                                          | T <sub>A</sub>       | -40    | _    | 105  | °C   | Extended temperature<br>SLB 9673AU2.0 devices            |

| Storage temperature                                          | T <sub>S</sub>       | -40    | _    | 125  | °C   | -                                                        |

| ESD robustness HBM: $1.5 \text{ k}\Omega$ , $100 \text{ pF}$ | V <sub>ESD,HBM</sub> | _      | _    | 2000 | V    | According to EIA/JESD22-A114-B                           |

| ESD robustness                                               | V <sub>ESD,CDM</sub> | -      | -    | 500  | V    | According to ESD Association<br>Standard STM5.3.1 - 1999 |

| Latchup immunity                                             | I latch              |        |      | 100  | mA   | According to EIA/JESD78                                  |

Attention: Stresses above the maximum values listed here may cause permanent damage to the device.

Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Maximum ratings are absolute ratings; exceeding only one of these values may cause irreversible damage to the integrated circuit.

## 3.1.1.2 Functional operating range

Table 3 Functional operating range

| Parameter                 | Symbol          |      | Values |      |    | Note or test condition                        |

|---------------------------|-----------------|------|--------|------|----|-----------------------------------------------|

|                           |                 | Min. | Тур.   | Max. |    |                                               |

| Supply Voltage            | V <sub>DD</sub> | 3.0  | 3.3    | 3.6  | V  | -                                             |

|                           |                 | 1.65 | 1.8    | 1.95 | V  | -                                             |

| Ambient temperature       | T <sub>A</sub>  | -40  | -      | 85   | °C | Enhanced temperature<br>SLB 9673XU2.0 devices |

| Ambient temperature       | T <sub>A</sub>  | -40  | -      | 105  | °C | Extended temperature<br>SLB 9673AU2.0 devices |

| Useful lifetime           |                 | _    | _      | 10   | у  |                                               |

| Operating lifetime        |                 | _    | _      | 10   | у  |                                               |

| Average T A over lifetime |                 | _    | 55     | _    | °C |                                               |

#### **Datasheet**

#### 3 Solution details

#### 3.1.1.3 DC characteristics

$T_A$  = 25°C,  $V_{DD}$  = 3.3 V ± 0.3 V or  $V_{DD}$  = 1.8 V ± 0.15 V unless otherwise noted.

Table 4 Current consumption

| Parameter                            | Symbol Values Unit Note or test co |      | Note or test condition |      |    |                                                                                                    |

|--------------------------------------|------------------------------------|------|------------------------|------|----|----------------------------------------------------------------------------------------------------|

|                                      |                                    | Min. | Тур.                   | Max. |    |                                                                                                    |

| Current Consumption in Active Mode   | I <sub>VDD_Active</sub>            |      |                        | 35   | mA |                                                                                                    |

| Current Consumption in<br>Sleep Mode | I <sub>VDD_Sleep</sub>             |      | 120                    |      | μΑ | Pins GPIO, RST# and I2C_PIRQ# = $V_{\rm DD}$ , CS# inactive (= $V_{\rm DD}$ ), no I2C bus activity |

| Current Consumption during reset     | I <sub>VDD_Reset</sub>             |      | 130                    |      | μΑ | Pin RST# active (= GND), GPIO and I2C_PIRQ# don't care                                             |

**Note**: Current consumption does not include any currents flowing through resistive loads on output pins!

**Note**: Device sleep mode will be entered after 50 milliseconds of inactivity after the last TPM command was

executed.

Table 5 DC characteristics of I2C interface pins (SCL, SDA, TEST#, RST#, I2C\_PIRQ#)

| Parameter               | Symbol            | Values              |      |                      | Unit | Note or test condition                  |

|-------------------------|-------------------|---------------------|------|----------------------|------|-----------------------------------------|

|                         |                   | Min.                | Тур. | Max.                 |      |                                         |

| Input voltage high      | V <sub>IH</sub>   | 0.7 V <sub>DD</sub> |      | V <sub>DD</sub> +0.5 | V    | _                                       |

| Input voltage low       | V <sub>IL</sub>   | -0.5                |      | 0.3 V <sub>DD</sub>  | V    | _                                       |

| Input leakage current   | I <sub>LEAK</sub> | -2                  |      | 2                    | μΑ   | 0 V < V <sub>IN</sub> < V <sub>DD</sub> |

| Output high voltage     | V <sub>OH</sub>   | 0.9 V <sub>DD</sub> |      |                      | V    | I <sub>OH</sub> = -100 μA               |

| Output low voltage      | V <sub>OL</sub>   |                     |      | 0.1 V <sub>DD</sub>  | V    | I <sub>OL</sub> = 1.5 mA                |

| Pad input capacitance   | C <sub>IN</sub>   |                     |      | 10                   | pF   |                                         |

| Output load capacitance | C <sub>LOAD</sub> |                     |      | 30                   | pF   |                                         |

Table 6 DC characteristics of GPIO pins

| Parameter             | Symbol            | Values               |      |                      | Unit | Note or test condition                  |

|-----------------------|-------------------|----------------------|------|----------------------|------|-----------------------------------------|

|                       |                   | Min.                 | Тур. | Max.                 |      |                                         |

| Input voltage high    | V <sub>IH</sub>   | 0.7 V <sub>DD</sub>  |      | V <sub>DD</sub> +0.3 | V    | Pins GPIO                               |

| Input voltage low     | V <sub>IL</sub>   | -0.5                 |      | 0.3 V <sub>DD</sub>  | V    | Pins GPIO                               |

| Input leakage current | I <sub>LEAK</sub> | -2                   |      | 2                    | μA   | 0 V < V <sub>IN</sub> < V <sub>DD</sub> |

| Output high voltage   | V <sub>OH</sub>   | V <sub>DD</sub> -0.3 |      |                      | V    | I <sub>OH</sub> = -1 mA, pins GPIO      |

| Output low voltage    | V <sub>OL</sub>   |                      |      | 0.3                  | V    | I <sub>OL</sub> = 1 mA, pins GPIO       |

| Pad input capacitance | C <sub>IN</sub>   |                      |      | 10                   | pF   | Pins GPIO                               |

## 3.1.1.4 AC characteristics

$T_A = 25$ °C,  $V_{DD} = 3.3$ V  $\pm 0.3$ V or  $V_{DD} = 1.8$ V  $\pm 0.15$ V unless otherwise noted.

#### **Datasheet**

#### 3 Solution details

Table 7 Power supply

| Parameter                | Symbol            | Values |      | Unit | Note or test condition |  |

|--------------------------|-------------------|--------|------|------|------------------------|--|

|                          |                   | Min.   | Тур. | Max. |                        |  |

| Supply voltage rise time | t <sub>VDDR</sub> |        |      | 1.0  | V/ns                   |  |

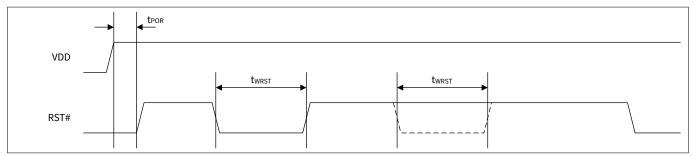

Table 8 Device reset

| Parameter             | Symbol            | Values |      | Unit | Note or test condition |  |

|-----------------------|-------------------|--------|------|------|------------------------|--|

|                       |                   | Min.   | Тур. | Max. |                        |  |

| Cold (Power-On) Reset | t <sub>POR</sub>  | 80     |      |      | μs                     |  |

| Warm Reset            | t <sub>WRST</sub> | 2      |      |      | μs                     |  |

Figure 5 Reset timing

## 3.1.1.4.1 I2C Interface Characteristics

The electrical characteristics are compliant to the NXP I<sup>2</sup>C bus specification [1] for "standard-mode" ( $f_{SCL} \le 100$  kHz), "fast-mode" ( $f_{SCL} \le 400$  kHz) and "fast-mode plus" ( $f_{SCL} \le 1000$  kHz), with certain deviations stated in Table 9, Table 10, and Table 11 below

For printed circuit board design the reduced output fall time tOF compared to the NXP I2C bus specification needs to be considered!

TA = 25°C,  $V_{DD}$  = 3.3 V  $\pm$  0.3 V or  $V_{DD}$  = 1.8 V  $\pm$  0.15 V unless otherwise noted.

Table 9 I2C Standard Mode Interface Characteristics

| Parameter                                                                  | Symbol                 | Values              |      |                                                   | Unit | Note or test condition                                    |

|----------------------------------------------------------------------------|------------------------|---------------------|------|---------------------------------------------------|------|-----------------------------------------------------------|

|                                                                            |                        | Min.                | Тур. | Max.                                              |      |                                                           |

| SCL clock frequency                                                        | $f_{SCL}$              | 0                   | _    | 100                                               | kHz  | _                                                         |

| Input voltage low                                                          | <b>V</b> <sup>IL</sup> | -0.5                | _    | 0.3 V <sub>DD</sub>                               | V    | _                                                         |

| Input voltage high                                                         | V <sup>IH</sup>        | 0.7 V <sub>DD</sub> | _    | V <sub>DD</sub> +0.5<br>or<br>V <sub>DD,max</sub> | V    | Maximum = min(V <sub>DD</sub> +0.5, V <sub>DD,max</sub> ) |

| Output low voltage                                                         | V <sub>OL</sub>        | _                   | _    | 0.4                                               | V    | $I_{OL} = 2 \text{ mA}, V_{DD} \le 2 \text{ V}$           |

| Output low voltage                                                         | V <sub>OL</sub>        | _                   | _    | 0.4                                               | ٧    | $I_{OL} = 3 \text{ mA}, V_{DD} > 2 \text{ V}$             |

| Low level output current                                                   | I <sub>OL</sub>        | 2                   | _    | _                                                 | mA   | $V_{OL} = 0.4 \text{ V}, V_{DD} < 2.7 \text{ V}$          |

| Low level output current                                                   | I <sub>OL</sub>        | 3                   | _    | _                                                 | mA   | $V_{OL} = 0.4 \text{ V}, V_{DD} \ge 2.7 \text{ V}$        |

| Output fall time from $V_{\text{IHmin}}$ to $V_{\text{ILmax}}$ (at device) | t <sub>OF</sub>        | _                   | _    | 250                                               | ns   | $C_b \le 200 \text{ pF}, V_{DD} \le 2.7 \text{ V}$        |

(table continues...)

#### **Datasheet**

# infineon

#### 3 Solution details

## Table 9 (continued) I2C Standard Mode Interface Characteristics

| Parameter                                                                  | Symbol Values   |      |      |      | Unit | Note or test condition                             |

|----------------------------------------------------------------------------|-----------------|------|------|------|------|----------------------------------------------------|

|                                                                            |                 | Min. | Тур. | Max. |      |                                                    |

| Output fall time from $V_{\text{IHmin}}$ to $V_{\text{ILmax}}$ (at device) | t <sub>OF</sub> | _    | _    | 250  | ns   | $C_b \le 400 \text{ pF, V}_{DD} \ge 2.7 \text{ V}$ |

| Capacitive load for each bus line                                          | C <sub>b</sub>  | _    | _    | 200  | pF   | V <sub>DD</sub> < 2.7 V                            |

|                                                                            | C <sub>b</sub>  | _    | _    |      |      | $V_{DD} \ge 2.7 \text{ V}$                         |

#### Table 10 I2C Fast Mode Interface Characteristics

| Parameter                                              | Symbol          |                               | Values |                                                   | Unit | Note or test condition                                          |

|--------------------------------------------------------|-----------------|-------------------------------|--------|---------------------------------------------------|------|-----------------------------------------------------------------|

|                                                        |                 | Min.                          | Тур.   | Max.                                              |      |                                                                 |

| SCL clock frequency                                    | $f_{SCL}$       | 0                             | _      | 400                                               | kHz  | _                                                               |

| Input voltage low                                      | V <sub>IL</sub> | -0.5                          | _      | 0.3 V <sub>DD</sub>                               | V    | _                                                               |

| Input voltage high                                     | V <sub>IH</sub> | 0.7 V <sub>DD</sub>           | _      | V <sub>DD</sub> +0.5<br>or<br>V <sub>DD,max</sub> | V    | Maximum = min(V <sub>DD</sub> +0.5, V <sub>DD,max</sub> )       |

| Output low voltage                                     | V <sub>OL</sub> | _                             | _      | 0.4                                               | V    | $I_{OL} = 2 \text{ mA}, V_{DD} \le 2 \text{ V}$                 |

| Output low voltage                                     | V <sub>OL</sub> | _                             | _      | 0.4                                               | V    | I <sub>OL</sub> = 3 mA, V <sub>DD</sub> > 2 V                   |

| Low level output current                               | I <sub>OL</sub> | 2                             | _      | _                                                 | mA   | $V_{OL} = 0.4 \text{ V}, V_{DD} < 2.7 \text{ V}$                |

| Low level output current                               | I <sub>OL</sub> | 3                             | _      | _                                                 | mA   | $V_{OL} = 0.4 \text{ V}, V_{DD} \ge 2.7 \text{ V}$              |

| Output fall time from VIHmin to VILmax (at device pin) | t <sub>OF</sub> | 20*V <sub>DD</sub> /<br>5.5 V | _      | 250                                               | ns   | $C_b$ ,min< $C_b \le 200 \text{ pF}$ , $V_{DD} < 2.7 \text{ V}$ |

| Output fall time from VIHmin to VILmax (at device pin) | t <sub>OF</sub> | 20*V <sub>DD</sub> /<br>5.5 V | _      | 250                                               | ns   | $C_{b,min} < C_b \le 400 \text{ pF}, V_{DD} \ge 2.7 \text{ V}$  |

| Capacitive load for each bus line                      | C <sub>b</sub>  | 15                            | _      | 200                                               | pF   | V <sub>DD</sub> < 2.7 V                                         |

| Capacitive load for each bus line                      | C <sub>b</sub>  | 15                            | _      | 400                                               | pF   | $V_{DD} \ge 2.7 \text{ V}$                                      |

## Table 11 I2C Fast Mode plus Interface Characteristics

| Parameter           | Symbol          |                     | Values |                                                    | Unit | Note or test condition                                        |

|---------------------|-----------------|---------------------|--------|----------------------------------------------------|------|---------------------------------------------------------------|

|                     |                 | Min.                | Тур.   | Max.                                               |      |                                                               |

| SCL clock frequency | $f_{SCL}$       | 0                   | _      | 1000                                               | kHz  | _                                                             |

| Input voltage low   | V <sub>IL</sub> | -0.5                | _      | 0.3 V <sub>DD</sub>                                | ٧    | _                                                             |

| Input voltage high  | V <sub>IH</sub> | 0.7 V <sub>DD</sub> | _      | V <sub>DD</sub> +0.5<br>or<br>V <sub>DD</sub> ,max | V    | Maximum = min(V <sub>DD</sub> + 0.5,<br>V <sub>DD,max</sub> ) |

| Output low voltage  | V <sub>OL</sub> | _                   | _      | 0.4                                                | ٧    | $I_{OL} = 2 \text{ mA}, V_{DD} \le 2 \text{ V}$               |

| Output low voltage  | V <sub>OL</sub> | _                   | _      | 0.4                                                | ٧    | I <sub>OL</sub> = 3 mA, V <sub>DD</sub> > 2 V                 |

(table continues...)

#### **Datasheet**

#### 3 Solution details

Table 11 (continued) I2C Fast Mode plus Interface Characteristics

| Parameter                                              | Symbol Values   |                               |      |      | Unit | Note or test condition                             |

|--------------------------------------------------------|-----------------|-------------------------------|------|------|------|----------------------------------------------------|

|                                                        |                 | Min.                          | Тур. | Max. |      |                                                    |

| Low level output current                               | I <sub>OL</sub> | 2                             | _    | _    | mA   | V <sub>OL</sub> = 0.4 V, V <sub>DD</sub> < 2.7 V   |

| Low level output current                               | I <sub>OL</sub> | 3                             | _    | _    | mA   | $V_{OL} = 0.4 \text{ V}, V_{DD} \ge 2.7 \text{ V}$ |

| Output fall time from VIHmin to VILmax (at device pin) | $t_{OF}$        | 20*V <sub>DD</sub> /<br>5.5 V | _    | 120  | ns   | $C_{b,min} < C_b \le 150 \text{ pF}$               |

| Capacitive load for each bus line                      | C <sub>b</sub>  | 15                            | _    | 150  | pF   |                                                    |

#### **Timing** 3.1.1.5

Some pads are disabled after deassertion of the reset signal for up to 500 µs. The SLB 9673 TPM 2.0 features security mechanisms which detect and count all resets.

#### Pin description 3.1.2

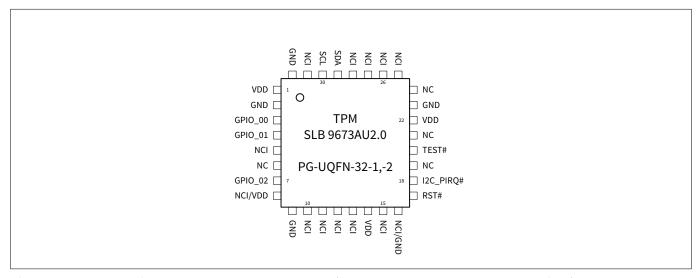

Figure 6 Pinout of the SLB 9673 TPM 2.0 (PG-UQFN-32-1,-2 package, top view)

Table 12 **Buffer types**

| Buffer type | Description    |

|-------------|----------------|

| TS          | Tri-state pin  |

| IN          | Input pin      |

| OD          | Open-drain pin |

## **Datasheet**

## 3 Solution details

Table 13 I/O Signals

| Pin number      | Name      | Pin  | Buffer | Function                                                                                                                                                                                                                                                                 |

|-----------------|-----------|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PG-UQFN-32-1,-2 |           | type | type   |                                                                                                                                                                                                                                                                          |

| 30              | SCL       | I/O  | OD     | I2C bus clock signal                                                                                                                                                                                                                                                     |

|                 |           |      |        | The clock signal of the I2C bus.                                                                                                                                                                                                                                         |

|                 |           |      |        | Note that this pin may also act as output when clock stretching is active.                                                                                                                                                                                               |

| 29              | SDA       | I/O  | OD     | I2C bus data signal                                                                                                                                                                                                                                                      |

|                 |           |      |        | The data signal of the I2C bus.                                                                                                                                                                                                                                          |

| 18              | I2C_PIRQ# | 0    | OD     | Interrupt signal                                                                                                                                                                                                                                                         |

|                 |           |      |        | This pin can be connected to the host interrupt controller to allow interrupt driven reads of the response data instead of polling. As soon as a response is available, the signal is asserted (low) and remains active until the complete response is read by the host. |

| 17              | RST#      | I    | IN     | Reset                                                                                                                                                                                                                                                                    |

|                 |           |      |        | External reset signal. Asserting this pin unconditionally resets the device. The signal is active low. This pin has a weak internal pull-up resistor.                                                                                                                    |

| 20              | TEST#     | I    | IN     | Test                                                                                                                                                                                                                                                                     |

|                 |           |      |        | Test signal, must be externally connected to a static high level.                                                                                                                                                                                                        |

| 3               | GPIO_00   | I/O  | TS     | General purpose IO                                                                                                                                                                                                                                                       |

|                 |           |      |        | This pin may be left unconnected; it has an internal pull-up resistor. It can be controlled via TPM NV GPIO functionality.                                                                                                                                               |

| 4               | GPIO_01   | I/O  | TS     | General purpose IO                                                                                                                                                                                                                                                       |

|                 |           |      |        | This pin may be left unconnected; it has an internal pull-up resistor. It can be controlled via TPM NV GPIO functionality.                                                                                                                                               |

| 7               | GPIO_02   | I/O  | TS     | General purpose IO                                                                                                                                                                                                                                                       |

|                 |           |      |        | This pin may be left unconnected; it has an internal pull-up resistor. It can be controlled via TPM NV GPIO functionality.                                                                                                                                               |

## Table 14 Power supply

| Pin number      | Name | Pin  | Buffer | Function                                                                                                    |

|-----------------|------|------|--------|-------------------------------------------------------------------------------------------------------------|

| PG-UQFN-32-1,-2 |      | type | type   |                                                                                                             |

| 1, 14, 22       | VDD  | PWR  | _      | Power supply All VDD pins must be connected externally and should be bypassed to GND via 100 nF capacitors. |

| 2, 9, 23, 32    | GND  | GND  | _      | Ground All GND pins must be connected externally.                                                           |

#### **Datasheet**

#### 3 Solution details

Table 15 Not connected

| Pin number                     | Name    | Pin  | Buffer | Function                                                                                                                                                                                                                                                                             |

|--------------------------------|---------|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PG-UQFN-32-1,-2                |         | type | type   |                                                                                                                                                                                                                                                                                      |

| 6, 19, 21, 24                  | NC      | NU   | _      | No connect All pins must not be connected externally (must be left floating).                                                                                                                                                                                                        |

| 5, 11 - 13, 15,<br>25 - 28, 31 | NCI     | _    | _      | Not connected internally All pins are not connected internally (can be connected externally).                                                                                                                                                                                        |

| 10                             | NCI/GND | _    | -      | Not connected internally This pin is not connected internally. For future use, it is recommended to connect this pin to GND (preferably via a pull-down resistor).                                                                                                                   |

| 8                              | NCI/VDD | _    | _      | Not connected internally/VDD  This pin is not connected internally (can be connected externally).  Note that pin 8 is defined as VDD in the TCG specification [2]. To be compliant, VDD can be connected to this pin.  For future use, it is recommended to connect this pin to VDD. |

| 16                             | NCI/GND | _    | _      | Not connected internally/GND This pin is not connected internally (can be connected externally). Note that pin 16 is defined as GND in the TCG specification [2]. To be compliant, GND can be connected to this pin. For future use, it is recommended to connect this pin to GND.   |

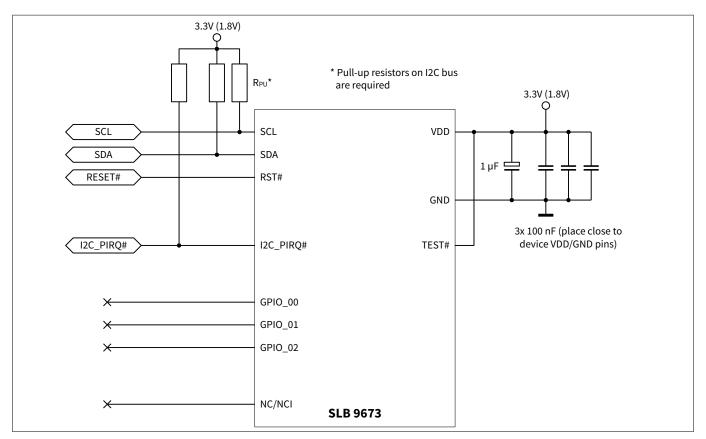

# 3.1.3 Typical schematic

The figure below shows the typical schematic for the SLB 9673 TPM 2.0. The power supply pins should be bypassed to GND with capacitors located close to the device.

# infineon

#### 3 Solution details

Figure 7 Typical schematic

#### **Datasheet**

#### 3 Solution details

#### 3.2 TPM embedded software

The embedded software of the Infineon SLB 9673 TPM 2.0 is fully compliant with the TPM Library specification [1] and the PC Client Platform TPM Profile (PTP) [2], including Errata (see [3] and [4]).

This section documents vendor-specific functionality and also the actual parameters of the implementation since the specified values in [1] and [2] are only minimum requirements.

## 3.2.1 Implemented algorithms

A list of algorithms implemented in the TPM can be read using the TPM2\_GetCapability command (capability = TPM\_CAP\_ALGS).

TPM\_ALG\_AES supports CFB mode and may be used for all specified use cases (see [1]) and also for bulk encryption via the command TPM2\_EncryptDecrypt2, which is supported by this TPM.

The elliptic curve TPM\_ECC\_BN\_P256 can only be used for ECDAA.

Table 16 Implemented algorithms

| Algorithm name | Key size/curve    | Mandatory (M),<br>optional (O) per [2] | Implemented in SLB 9673 TPM 2.0 |

|----------------|-------------------|----------------------------------------|---------------------------------|

| TPM_ALG_RSA    | 1024              | SHOULD NOT BE USED                     | X (D)                           |

|                | 2048              | M                                      | X                               |

|                | 3072              | M                                      | X                               |

|                | 4096              | 0                                      | X                               |

| TPM_ALG_AES    | 128               | M                                      | X                               |

|                | 192               | 0                                      | X                               |

|                | 256               | M                                      | X                               |

| TPM_ALG_SHA1   | n.a.              | M/D                                    | X (D)                           |

| TPM_ALG_SHA256 | n.a.              | M                                      | X                               |

| TPM_ALG_SHA384 | n.a.              | M                                      | X                               |

| TPM_ALG_ECC    | TPM_ECC_NIST_P256 | M                                      | X                               |

|                | TPM_ECC_NIST_P384 | M                                      | X                               |

|                | TPM_ECC_BN_P256   | 0                                      | X                               |

Note:

TPM\_ALG\_RSA with 1024-bit and TPM\_ALG\_SHA1 support is implemented but deprecated (D). Consequently, support for these algorithms may be removed in a future version and it is not recommended to use them anymore.

#### 3.2.2 Available resources

The table below provides an overview of the available resources.

Table 17 Available resources

| Number of PCRs (SHA-1, SHA-256 or SHA-384) (TPM_PT_PCR_COUNT)                         | 24          |

|---------------------------------------------------------------------------------------|-------------|

| See Allocation of PCR banks for further details.                                      |             |

| Amount of free NV memory including space of predefined NV indices (4 EK certificates) | 51072 Bytes |

| /table continues \                                                                    |             |

(table continues...)

#### **Datasheet**

#### 3 Solution details

## Table 17 (continued) Available resources

| 45720 Bytes  |

|--------------|

|              |

| 3            |

| 64           |

| 3            |

| 7            |

| 0 1)         |

| 2            |

| 1024 Bytes   |

| 768 Bytes    |

| 2000 Bytes   |

| ) 1100 Bytes |

|              |

<sup>1)</sup> The value 0 indicates that there is no fixed maximum. The number of counter indices is determined by the available NV memory pool.

#### **Datasheet**

#### 3 Solution details

## 3.2.3 Command ordinal list

The TPM implements the TCG standard commands defined in Table 18 and the vendor-specific commands defined in Table 19. All other ordinals will return TPM\_RC\_COMMAND\_CODE.

| Table 18 Command code list                          |                              |

|-----------------------------------------------------|------------------------------|

| Signals                                             |                              |

| _TPM_INIT                                           | _TPM_HashData                |

|                                                     | _TPM_HashEnd                 |

| Startup                                             |                              |

| TPM_CC_Startup                                      | TPM_CC_Shutdown              |

| Testing                                             |                              |

| TPM_CC_IncrementalSelfTest                          | TPM_CC_SelfTest              |

| TPM_CC_GetTestResult                                |                              |

| Session Commands                                    |                              |

| TPM_CC_StartAuthSession                             | TPM_CC_PolicyRestart         |

| Object Commands                                     |                              |

| TPM_CC_Create                                       | TPM_CC_Load                  |

| TPM_CC_LoadExternal                                 | TPM_CC_ReadPublic            |

| TPM_CC_ActivateCredential                           | TPM_CC_MakeCredential        |

| TPM_CC_Unseal                                       | TPM_CC_ObjectChangeAuth      |

| TPM_CC_CreateLoaded                                 |                              |

| Duplication Commands                                |                              |

| TPM_CC_Duplicate                                    | TPM_CC_Import                |

| Asymmetric Primitives                               |                              |

| TPM_CC_RSA_Encrypt                                  | TPM_CC_RSA_Decrypt           |

| TPM_CC_ECDH_KeyGen                                  | TPM_CC_ECDH_ZGen             |

| TPM_CC_ECC_Parameters                               |                              |

| Symmetric Primitives                                |                              |

| TPM_CC_Hash                                         | TPM_CC_HMAC                  |

| TPM_CC_EncryptDecrypt2 [Configurable] <sup>1)</sup> |                              |

| Random Number Generator                             |                              |

| TPM_CC_GetRandom                                    | TPM_CC_StirRandom            |

| Hash/HMAC/Event Sequences                           |                              |

| TPM_CC_HMAC_Start                                   | TPM_CC_HashSequenceStart     |

| TPM_CC_SequenceUpdate                               | TPM_CC_SequenceComplete      |

| TPM_CC_EventSequenceComplete                        |                              |

| Attestation Commands                                |                              |

| TPM_CC_Certify                                      | TPM_CC_CertifyCreation       |

| TPM_CC_Quote                                        | TPM_CC_GetSessionAuditDigest |

| (table continues)                                   | ,                            |

## **Datasheet**

## 3 Solution details

| Table 18 (continued) Command co      | de list                           |

|--------------------------------------|-----------------------------------|

| TPM_CC_GetTime                       |                                   |

| Anonymous Attestation                |                                   |

| TPM_CC_Commit                        |                                   |

| Signature Verification               |                                   |

| TPM_CC_VerifySignature               | TPM_CC_Sign                       |

| Integrity Collection (PCR)           |                                   |

| TPM_CC_PCR_Extend                    | TPM_CC_PCR_Event                  |

| TPM_CC_PCR_Read                      | TPM_CC_PCR_Allocate               |

| TPM_CC_PCR_Reset                     |                                   |

| Enhanced Authorization (EA) Commands |                                   |

| TPM_CC_PolicySigned                  | TPM_CC_PolicySecret               |

| TPM_CC_PolicyTicket                  | TPM_CC_PolicyOR                   |

| TPM_CC_PolicyPCR                     | TPM_CC_PolicyLocality             |

| TPM_CC_PolicyNV                      | TPM_CC_PolicyCounterTimer         |

| TPM_CC_PolicyCommandCode             | TPM_CC_PolicyCpHash               |

| TPM_CC_PolicyNameHash                | TPM_CC_PolicyDuplicationSelect    |

| TPM_CC_PolicyAuthorize               | TPM_CC_PolicyAuthValue            |

| TPM_CC_PolicyPassword                | TPM_CC_PolicyGetDigest            |

| TPM_CC_PolicyNvWritten               | TPM_CC_PolicyTemplate             |

| TPM_CC_PolicyAuthorizeNV             |                                   |

| Hierarchy Commands                   |                                   |

| TPM_CC_CreatePrimary                 | TPM_CC_HierarchyControl           |

| TPM_CC_SetPrimaryPolicy              | TPM_CC_ChangePPS                  |

| TPM_CC_ChangeEPS [Configurable] 1)   | TPM_CC_Clear                      |

| TPM_CC_ClearControl                  | TPM_CC_HierarchyChangeAuth        |

| Dictionary Attack Functions          |                                   |

| TPM_CC_DictionaryAttackLockReset     | TPM_CC_DictionaryAttackParameters |

| Context Management                   |                                   |

| TPM_CC_ContextSave                   | TPM_CC_ContextLoad                |

| TPM_CC_FlushContext                  | TPM_CC_EvictControl               |

| Clocks and Timers                    |                                   |

| TPM_CC_ReadClock                     | TPM_CC_ClockSet                   |

| TPM_CC_ClockRateAdjust               |                                   |

| Capability Commands                  |                                   |

| TPM_CC_GetCapability                 | TPM_CC_TestParms                  |

| Non-Volatile Storage                 |                                   |

| TPM_CC_NV_DefineSpace                | TPM_CC_NV_UndefineSpace           |

| (table continues)                    |                                   |

#### **Datasheet**

## 3 Solution details

Table 18 (continued) Command code list

| TPM_CC_NV_ReadPublic |

|----------------------|

| TPM_CC_NV_Increment  |

| TPM_CC_NV_SetBits    |

| TPM_CC_NV_Read       |

| TPM_CC_NV_ChangeAuth |

|                      |

|                      |

<sup>1)</sup> See TPM2\_SetCapabilityVendor for configuration

**Note**: Table 19 does not comprehensively list all vendor-defined TPM commands.

Table 19 Vendor-specific TPM\_CC constants

| Name                             | Command code | NV<br>write | Decrypt | Encrypt | Description                                                                                                                                               |

|----------------------------------|--------------|-------------|---------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| TPM_CC_SetCapabilityVendor       | 0x20000400   | Y           | N       | N       | Vendor-specific command to enable/disable and lock of configurable commands. Refer to TPM2_SetCapabilityVendo r for further details.                      |

| TPM_CC_FullFipsSelfTestVendor    | 0x20000401   | N           | N       | N       | Vendor specific command for executing all selftests which are performed at first power-up.  Refer to TPM2_FullFipsSelfTestVen dor for further details.    |

| TPM_CC_FieldUpgradeStartVendor   | 0x2000012F   | Y           | N       | N       | Vendor specific command for starting TPM firmware update mode while in TPM operational mode.  Refer to TPM2_FieldUpgradeStartV endor for further details. |

| TPM_CC_FieldUpgradeAbandonVendor | 0x20000130   | N           | N       | N       | Vendor specific command for aborting the field upgrade while in TPM firmware update mode.  Refer to TPM2_FieldUpgradeAband onVendor for further details.  |

(table continues...)

## **Datasheet**

## 3 Solution details

## Table 19 (continued) Vendor-specific TPM\_CC constants

| Name                              | Command code | NV<br>write | Decrypt | Encrypt | Description                                                                                                                                               |

|-----------------------------------|--------------|-------------|---------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| TPM_CC_FieldUpgradeManifestVendor | 0x20000131   | Y           | N       | N       | Vendor specific command for validating the manifest while in TPM firmware update mode.  Refer to TPM2_FieldUpgradeManife stVendor for further details.    |

| TPM_CC_FieldUpgradeDataVendor     | 0x20000132   | Y           | N       | N       | Vendor specific command for updating the firmware while in TPM firmware update mode.  Refer to  TPM2_FieldUpgradeDataVe ndor for further details.         |

| TPM_CC_FieldUpgradeFinalizeVendor | 0x20000133   | Y           | N       | N       | Vendor-specific command for finalizing the field upgrade process in TPM operational mode.  Refer to TPM2_FieldUpgradeFinaliz eVendor for further details. |

#### **Datasheet**

3 Solution details

#### 3.2.4 **Generation of RSA keys**

#### 3.2.4.1 **Pre-generation of RSA keys**

The TPM provides pre-generation of 2048-bit RSA keys in the background during idle times. A maximum of seven 2048-bit RSA keys can be generated and stored in non-volatile memory without any impact on the available amount of free non-volatile memory as stated in Table 17. When the user instructs the TPM to generate a new 2048-bit ordinary RSA key using TPM2\_Create or TPM2\_CreateLoaded, one of the pre-generated keys (if available) will be picked and returned. If the user demands more keys than the number of currently available pre- generated keys, the TPM will need to generate new keys in place, which will increase the total response time. All pre-generated keys will be discarded if command TPM2 StirRandom is sent to the TPM and reseeding of TPM Random Number Generator (RNG) is triggered.

Pre-generation is only supported for (RSA 2k) Ordinary keys. Pre-generation of Primary and Derived keys are not supported because their generation depends on caller-provided data. Pre-generation of any key types other than RSA is not supported because there is no performance advantage.

Note:

The key pre-generation is activated after TPM2 SelfTest has been executed after a reset (TPM INIT). Pre-generation of RSA 3072- and 4096-bit keys is not supported.

#### 3.2.4.2 Generation of RSA 3072- and 4096-bit keys

The creation of a 3072- or 4096-bit RSA primary key may take several minutes. For this reason, the duration of TPM2 CreatePrimary may violate the configured driver timeout value when waiting for the response of TPM2 CreatePrimary. For example, the Linux Kernel v4.17 or higher uses a timeout value of 300 seconds for TPM2\_CreatePrimary. This value may also be violated in some cases.

#### **Datasheet**

#### 3 Solution details

#### 3.2.5 Non-volatile storage

#### **Predefined NV indices** 3.2.5.1

The sizes documented in Table 20 are typical values and may vary by some bytes. The actual size can be read from the TPM using the command TPM2\_NV\_ReadPublic where parameter nvIndex defines the certificate whose size is to be determined.

Note:

The validity period of the EK certificate spans 15 years starting with production. This covers the validity for an expected lifetime of 10 years plus a buffer of 5 years between production and TPM assembly.

Table 20 **Predefined NV indices**

| Value      | Index Name                      | Default Size                                                                                                                                                                                                                            | Attributes   |

|------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 0x01C00002 | RSA 2048 EK<br>Certificate      | 1427 bytes (RSA Endorsement Key<br>Certificate)                                                                                                                                                                                         | see Table 21 |

| 0x01C0000A | ECC NIST P256 EK<br>Certificate | 844 bytes (ECC Endorsement Key<br>Certificate)                                                                                                                                                                                          | see Table 21 |

| 0x01C00016 | ECC NIST P384 EK<br>Certificate | 873 bytes (ECC Endorsement Key<br>Certificate)                                                                                                                                                                                          | see Table 21 |

| 0x01C0001C | RSA 3072 EK<br>Certificate      | The size of the RSA Endorsement<br>Key Certificate is typically 1560<br>bytes but may vary by some<br>bytes. The actual size can be read<br>from the TPM using the command<br>TPM2_NV_ReadPublic(nvIndex =<br>RSA 3072 EK Certificate). | see Table 21 |

#### **Attributes of predefined NV indices** Table 21

#### **Attributes**

TPMA\_NV\_PPWRITE

TPMA\_NV\_WRITEDEFINE

TPMA\_NV\_PPREAD

TPMA\_NV\_OWNERREAD

TPMA\_NV\_AUTHREAD

TPMA\_NV\_NO\_DA

TPMA\_NV\_WRITTEN

TPMA\_NV\_PLATFORMCREATE

#### **Datasheet**

#### 3 Solution details

## 3.2.6 Vendor-specific functionality

This section describes vendor-specific functionality, such as vendor-specific properties, commands and default values/settings, which extends the functionality described in the TPM Library specification [1].

## 3.2.6.1 Power saving mode

The TPM supports a reduced power consumption mode which is entered after inactivity for at least 50 ms has been detected. The resulting power consumption in this mode is shown in Table 4 (current consumption in sleep mode).

## 3.2.6.2 TPM and vendor properties

Properties defined within the TPM can be read with the command TPM2\_GetCapability. The values are vendor dependent or determined by a platform-specific specification. The following properties are returned by the Infineon SLB 9673 TPM 2.0 using the command TPM2\_GetCapability (capability = TPM\_CAP\_TPM\_PROPERTIES):

Table 22 Infineon TPM property values

| TPM_PT_MANUFACTURER       | "IFX"                                                                                                       |

|---------------------------|-------------------------------------------------------------------------------------------------------------|

| TPM_PT_VENDOR_STRING_1    | "SLB9"                                                                                                      |

| TPM_PT_VENDOR_STRING_2    | "673"                                                                                                       |

| TPM_PT_VENDOR_STRING_3    | NULL                                                                                                        |

| TPM_PT_VENDOR_STRING_4    | NULL                                                                                                        |

| TPM_PT_FIRMWARE_VERSION_1 | Major and minor version (for instance, 0x001A0018 indicates V26.24) <sup>1)</sup>                           |

| TPM_PT_FIRMWARE_VERSION_2 | Build number and Common Criteria certification state (for instance, 0x004A6100 or 0x004A6102) <sup>1)</sup> |

|                           | Byte 1: reserved for future use (0x00)                                                                      |

|                           | Byte 2 and 3: Build number (for instance, 0x4A61) <sup>1)</sup>                                             |

|                           | Byte 4: Common Criteria certification state/mode:                                                           |

|                           | 0x00 = TPM operational mode/TPM is CC certified                                                             |

|                           | 0x02 = TPM operational mode/TPM is not certified                                                            |

|                           | 0x62 = TPM firmware update mode                                                                             |

| TPM_PT_MODES              | Bit 0 (FIPS_140_2) = 1                                                                                      |

|                           | Bits 131 = 0                                                                                                |

<sup>1)</sup> The build- and version numbers given here are examples and do not necessarily match the numbers of the device this datasheet has been provided for.

The vendor-specific properties shown in the table below can be read by using the vendor-specific capability selector TPM CAP VENDOR PROPERTY:

Table 23 Infine on vendor-specific property constants

| TPM property  | Value      | Property value                                    |

|---------------|------------|---------------------------------------------------|

| PT_VENDOR_FIX | 0x80000000 | The group of fixed vendor specific properties.    |

| PT_VENDOR_VAR | 0xC0000000 | The group of variable vendor specific properties. |

#### **Datasheet**

# infineon

## 3 Solution details

Table 24 Infineon vendor-specific property values

| TPM property                            | Value             | Property value                                                          |

|-----------------------------------------|-------------------|-------------------------------------------------------------------------|

| TPM_PT_VENDOR_FIX_FU_COUNTER            | PT_VENDOR_FIX + 3 | UINT16 field upgrade counter for upgrades to different firmware version |

| TPM_PT_VENDOR_FIX_FU_COUNTER_SAME       | PT_VENDOR_FIX + 4 | UINT16 field upgrade counter for upgrades to same firmware version      |

| TPM_PT_VENDOR_FIX_FU_START_HASH_DI GEST | PT_VENDOR_FIX + 5 | TPMT_HA structure containing manifest hash digest for field upgrade:    |

|                                         |                   | Bytes 1-2: Hash digest algorithm (TPM_ALG_SHA384, TPM_ALG_SHA512)       |

|                                         |                   | Bytes 3-66: SHA512 manifest digest                                      |

|                                         |                   | Or                                                                      |

|                                         |                   | Bytes 3-50: SHA384 manifest digest or                                   |

| TPM_PT_VENDOR_FIX_FU_OPERATION_MO DE    | PT_VENDOR_FIX + 7 | UINT8 operation mode of firmware as described in Table 25               |

| TPM_PT_VENDOR_FIX_FU_KEYGROUP_ID        | PT_VENDOR_FIX + 8 | UINT32 ID of field upgrade keys                                         |

| TPM_PT_VENDOR_VAR_ENCRYPTDECRYPT2       | PT_VENDOR_VAR + 5 | Bytes 1-2: 0x0001 means feature is enabled                              |

|                                         |                   | Bytes 3-4: 0x0001 means feature is permanently locked                   |

| TPM_PT_VENDOR_VAR_CHANGEEPS             | PT_VENDOR_VAR + 6 | Bytes 1-2: 0x0001 means feature is enabled                              |

|                                         |                   | Bytes 3-4: 0x0001 means feature is permanently locked                   |

| TPM_PT_VENDOR_VAR_TPMID_NV              | PT_VENDOR_VAR + 7 | Bytes 1-2: 0x0001 means feature is enabled                              |

|                                         |                   | Bytes 3-4: 0x0001 means feature is permanently locked                   |

An overview of all possible values returned for the operation mode is given in the following table:

Table 25 TPM operation modes

| Operation<br>Mode | Description                                                                                   |

|-------------------|-----------------------------------------------------------------------------------------------|

| 0x00              | Normal TPM operational mode                                                                   |

| 0x01              | TPM firmware update mode when abandoning the field upgrade process is possible                |

| 0x02              | TPM firmware update mode when abandoning the field upgrade process is not possible anymore    |

| 0x03              | After successful field upgrade, but before TPM2_FieldUpgradeFinalizeVendor                    |

| 0x04              | After TPM2_FieldUpgradeFinalizeVendor or TPM2_FieldUpgradeAbandonVendor until the next reboot |

The next table lists FIFO Configuration registers initialized by the vendor.

#### **Datasheet**

#### 3 Solution details

#### Table 26 FIFO configuration registers

| Register | Value  | Comments                                          |

|----------|--------|---------------------------------------------------|

| TPM_VID  | 0x15D1 | Vendor identification of Infineon Technologies AG |

| TPM_DID  | 0x001C | Device identification                             |

| TPM_RID  | 0x16   | Revision identification register                  |

#### Table 27 TPM\_RID register value description

| Bit | Description                                     |  |

|-----|-------------------------------------------------|--|

| 0   | TPM 1.2 if set                                  |  |

| 1   | TPM 2.0 if set                                  |  |

| 2   | FIPS if set                                     |  |

| 3   | Reserved for future use, value 0                |  |

| 4-7 | Interface revision, currently 0001 <sub>B</sub> |  |

#### 3.2.6.3 Selftest operations

#### 3.2.6.3.1 TPM2 SelfTest

This command executes all selftests except for the tests which are only performed at first power-up (see Table 30 for further details). The selftest can be done in two ways. TPM2\_Selftest(fullTest = YES) always performs all tests while TPM2 Selftest(fullTest = NO) only executes tests which have not been run yet.

## 3.2.6.3.2 TPM2\_FullFipsSelfTestVendor

This command executes on demand all selftests which are performed at first power-up as required by FIPS 140-2. The selftest result can be read using the command TPM2\_GetTestResult.

Table 28 Incoming operands and sizes

| Туре                | Name        | Description                   |

|---------------------|-------------|-------------------------------|