#### LITIX™ Basic+

#### **Features**

- Three-channel device with integrated and protected output stages (current sinks), optimized to drive LEDs

- · High output current up to 150 mA per channel

- Possibility to offload power consumption via low cost external resistors to allow maximum current driving capability (Power Shift)

- Output current control via enable pin

- Fault management supports both 1-fail-all-OFF and 1-fail-all-ON

- · Analog output current control input to adjust the output current

- Open load (OL), short to battery (SC) and thermal shutdown protections

- Intelligent fault management: up to 10 devices can share a common error network with only one external resistor

- Thermal derating function via external NTC resistor

### **Potential applications**

- Cost effective "stop"/"tail" function with shared and separated LEDs per function

- Automotive light functions like turn indicators, position, fog, stop/tail, DRL and side markers

- Animated light functions like sequential indicator and "welcome/goodbye" functions

- Interior lighting functions like ambient lighting, illumination and dash board lighting

- LED indicators for industrial applications and instrumentation

#### **Product validation**

Product validation according to AEC-Q100, Grade 1.

Qualified for automotive applications.

#### **Description**

The TLD2372-3ET is a three channel low-side driver IC with integrated and protected output stages. It is designed to control LEDs with a current up to 150 mA as linear current sink (LCS). The Power Shift feature allows the device to reach maximum current driving capability by offloading power consumption to external low cost components. The diagnostic features and thermal derating via external NTC resistor provide a reliable solution for high current applications. The configurable fault management allows up to 10 and more devices to share the same error network and to be combined in applications with other LITIX™ LED drivers, such as other LITIX™ Basic+ products and LITIX™ TLD7002-16ES.

| Product type | Package  | Marking |

|--------------|----------|---------|

| TLD2372-3ET  | TFDSO-16 | 237     |

## **Datasheet**

# **Table of contents**

|      | Table of contents               | 7          |

|------|---------------------------------|------------|

|      |                                 |            |

| 1    | Product description             |            |

| 2    | Block diagram                   | 5          |

| 3    | Pin configuration               | 6          |

| 3.1  | Pin assignment                  | 6          |

| 3.2  | Pin definitions and functions   | .6         |

| 4    | General product characteristics | 8          |

| 4.1  | Absolute maximum ratings        | 8          |

| 4.2  | Functional range                | .9         |

| 4.3  | Thermal resistance              | .9         |

| 5    | Internal supply 1               | L1         |

| 5.1  | Description                     | L1         |

| 5.2  | Electrical characteristics      | L1         |

| 6    | Power stage                     | 13         |

| 6.1  | Output current regulation       | L3         |

| 6.2  | Thermal protection              | L3         |

| 6.3  | Electrical characteristics      | L4         |

| 7    | Power shift                     | L5         |

| 7.1  | Electrical characteristics      | 16         |

| 8    | <b>PWM control</b>              | L7         |

| 8.1  | Electrical characteristics      | L9         |

| 9    | Analog output current control   | 20         |

| 9.1  | Electrical characteristics      | 21         |

| 10   | Current reference generation    | 22         |

| 10.1 | Electrical characteristics      | 22         |

| 11   | Load diagnostics                | 23         |

| 11.1 | Diagnostics enable              | 23         |

| 11.2 | ERRN/DEN pin                    | 24         |

| 11.3 | D pin                           | <u>2</u> 4 |

| 11.4 | Fault management                | 25         |

| 11.5 | Electrical characteristics      | 28         |

| 12   | Application information         | 31         |

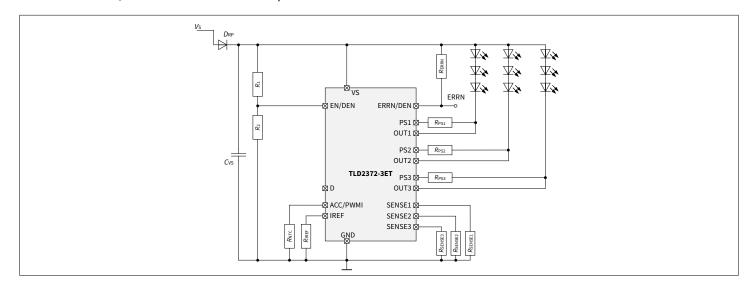

| 12.1 | Application diagram 3           | 31         |

| 13   | Package information             | 33         |

|      | Revision history                | 34         |

### **Datasheet**

Table of contents

| licelaimor  |      |      | っこ |

|-------------|------|------|----|

| uscialiller | <br> | <br> |    |

### **Datasheet**

1 Product description

# 1 Product description

## Table 1 Product summary

| Parameter                                | Symbol                       | Values                                             |

|------------------------------------------|------------------------------|----------------------------------------------------|

| Operating voltage                        | V <sub>S(func)</sub>         | 5.5 V - 18 V                                       |

| Extended operating voltage               | V <sub>S(ext)</sub>          | 4.5 V - 36 V                                       |

| Maximum load current                     | I <sub>SENSE(max)</sub>      | 150 mA                                             |

| Output current accuracy                  | V <sub>SENSE(reg)</sub>      | $\pm 4\%$ with $V_{\text{SENSE}} = 400 \text{ mV}$ |

| Current consumption in sleep mode        | I <sub>VS(sleep, max)</sub>  | 3 μΑ                                               |

| Maximum current consumption during fault | I <sub>VS(fault, ERRN)</sub> | 850 μΑ                                             |

| Maximum dropout voltage                  | V <sub>DR,CS(max)</sub>      | 0.6 V                                              |

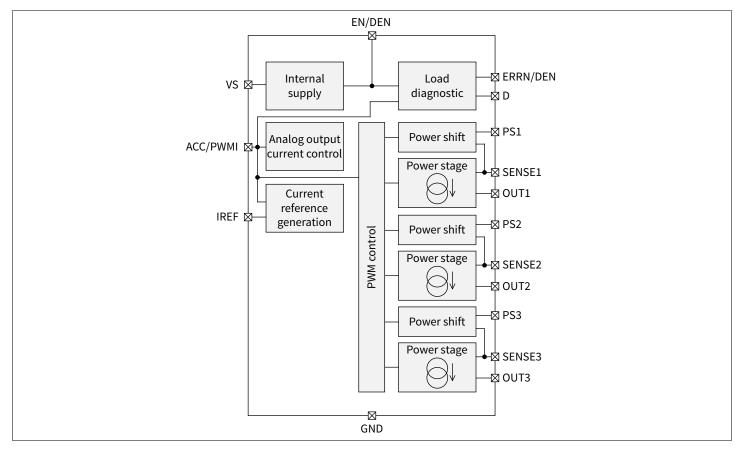

2 Block diagram

# 2 Block diagram

Figure 1 TLD2372-3ET Block diagram

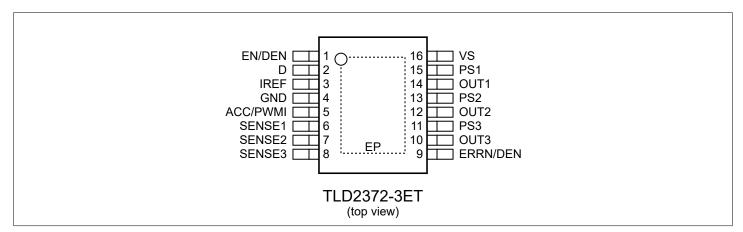

3 Pin configuration

# 3 Pin configuration

## 3.1 Pin assignment

Figure 2 Pin configuration PG-TFDSO-16

### 3.2 Pin definitions and functions

Table 2 Pin definitions and functions

| Pin    | Symbol   | Function                                                                                                                                                                                  |

|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16     | VS       | Power supply voltage                                                                                                                                                                      |

|        |          | Battery supply input                                                                                                                                                                      |

| 4      | GND      | Ground                                                                                                                                                                                    |

|        |          | Ground potential. Connect externally close to the chip                                                                                                                                    |

| 1      | EN/DEN   | Output enable and diagnosis control input                                                                                                                                                 |

|        |          | Connect to $V_S$ via a resistor divider to enable all outputs control and diagnosis capability                                                                                            |

| 2      | D        | Disable/delay error input                                                                                                                                                                 |

|        |          | Connect to a capacitor, leave open or connect to GND depending on the required diagnostic management                                                                                      |

| 3      | IREF     | Current reference generation                                                                                                                                                              |

|        |          | Connect to an external accurate low power resistor to generate a current reference                                                                                                        |

| 9      | ERRN/DEN | ERROR flag I/O and diagnosis control input                                                                                                                                                |

|        |          | Open drain, active low. Connect to $V_{\rm S}$ via pull-up resistor for ERROR flag capability only otherwise connect to $V_{\rm S}$ via a resistor divider to enable diagnosis capability |

| 6      | SENSE1   | Sense input 1                                                                                                                                                                             |

|        |          | Connect to low ohmic accurate sense resistor                                                                                                                                              |

| 7      | SENSE2   | Sense input 2                                                                                                                                                                             |

|        |          | Connect to low ohmic accurate sense resistor                                                                                                                                              |

| /+-bl- | \        | <del></del>                                                                                                                                                                               |

### **Datasheet**

3 Pin configuration

## Table 2 (continued) Pin definitions and functions

| Pin     | Symbol   | Function                                                                                                                                                                                                                             |

|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8       | SENSE3   | Sense input 3                                                                                                                                                                                                                        |

|         |          | Connect to low ohmic accurate sense resistor                                                                                                                                                                                         |

| 14      | OUT1     | Channel 1, output pin                                                                                                                                                                                                                |

|         |          | Open drain linear current sink. Connect to the target load                                                                                                                                                                           |

| 15      | PS1      | Power shift 1                                                                                                                                                                                                                        |

|         |          | Connect to external power resistor                                                                                                                                                                                                   |

| 12      | OUT2     | Channel 2, output pin                                                                                                                                                                                                                |

|         |          | Open drain linear current sink. Connect to the target load                                                                                                                                                                           |

| 13      | PS2      | Power shift 2                                                                                                                                                                                                                        |

|         |          | Connect to external power resistor                                                                                                                                                                                                   |

| 10      | OUT3     | Channel 3, output pin                                                                                                                                                                                                                |

|         |          | Open drain linear current sink. Connect to the target load                                                                                                                                                                           |

| 11      | PS3      | Power shift 3                                                                                                                                                                                                                        |

|         |          | Connect to external power resistor                                                                                                                                                                                                   |

| 5       | ACC/PWMI | Analog current control and PWMI input pin                                                                                                                                                                                            |

|         |          | Connect to external low power resistor or apply a desired reference voltage to adjust the output current. Connect to external NTC to apply thermal derating. It is possible also to connect to an external open drain PWM controller |

| Exposed | EP       | Exposed pad                                                                                                                                                                                                                          |

| pad     |          | Used only for thermal dissipation purpose. Connect externally to GND close to the chip                                                                                                                                               |

#### **Datasheet**

4 General product characteristics

### 4 General product characteristics

## 4.1 Absolute maximum ratings

### Table 3 Absolute maximum ratings

<sup>1)</sup>  $T_J = T_{J(func)}$ , all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                        | Symbol                   |      | Values |      | Unit | Note or condition                                                                   | P-Number |

|----------------------------------|--------------------------|------|--------|------|------|-------------------------------------------------------------------------------------|----------|

|                                  |                          | Min. | Тур.   | Max. |      |                                                                                     |          |

| Voltages                         |                          |      | -      |      |      |                                                                                     |          |

| Supply voltage                   | $V_{S}$                  | -0.3 | _      | 40   | V    | -                                                                                   | PRQ-32   |

| EN/DEN voltage                   | V <sub>EN/DEN</sub>      | -0.3 | _      | 40   | V    | -                                                                                   | PRQ-55   |

| Output voltages                  | V <sub>OUTx</sub>        | -0.3 | _      | 40   | V    | -                                                                                   | PRQ-58   |

| Power shift voltages             | $V_{PSx}$                | -0.3 | _      | 40   | V    | -                                                                                   | PRQ-60   |

| Sense voltage                    | V <sub>SENSEx</sub>      | -0.3 | _      | 0.9  | V    | _                                                                                   | PRQ-62   |

| ERRN/DEN voltage                 | V <sub>ERRN/DEN</sub>    | -0.3 | _      | 40   | V    | -                                                                                   | PRQ-61   |

| D voltage                        | $V_{D}$                  | -0.3 | _      | 5.5  | V    | -                                                                                   | PRQ-175  |

| ACC/PWMI voltage                 | V <sub>ACC/PWMI</sub>    | -0.3 | _      | 5.5  | V    | -                                                                                   | PRQ-64   |

| IREF voltage                     | V <sub>IREF</sub>        | -0.3 | _      | 5.5  | V    | -                                                                                   | PRQ-176  |

| Temperatures                     |                          |      |        | ·    |      |                                                                                     |          |

| Junction temperature             | $T_{J\_ABS}$             | -40  | _      | 150  | °C   | _                                                                                   | PRQ-39   |

| Storage temperature              | $T_{STG}$                | -55  | _      | 150  | -    | -                                                                                   | PRQ-40   |

| ESD robustness                   |                          |      |        | ·    | •    |                                                                                     |          |

| ESD robustness all pins<br>(HBM) | V <sub>ESD(HBM)</sub>    | -2   | _      | 2    | kV   | ESD robustness, Human<br>Body Model "HBM"<br>according to AEC<br>Q100-002           | PRQ-53   |

| ESD robustness all pins<br>(CDM) | V <sub>ESD(CDM)</sub>    | -500 | _      | 500  | V    | ESD robustness,<br>Charged Device Model<br>"CDM" according to AEC<br>Q100-011 Rev.D | PRQ-41   |

| ESD robustness corner pins (CDM) | V <sub>ESD(CDM)</sub> CR | -750 | _      | 750  | V    | ESD robustness,<br>Charged Device Model<br>"CDM" according to AEC<br>Q100-011 Rev.D | PRQ-54   |

<sup>1)</sup> Not subject to production test, specified by design

Note:

Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.

Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as outside the normal operating range. Protection functions are not designed for continuous repetitive operation.

#### **Datasheet**

4 General product characteristics

### 4.2 Functional range

#### Table 4 Functional range

$T_J = T_{J(func)}$ , all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                   | Symbol                    |      | Values |      | Unit | Note or condition                              | P-Number |

|---------------------------------------------|---------------------------|------|--------|------|------|------------------------------------------------|----------|

|                                             |                           | Min. | Тур.   | Max. |      |                                                |          |

| Voltages                                    |                           |      |        |      | ,    |                                                |          |

| Supply voltage for operating range          | $V_{S(func)}$             | 5.5  | _      | 18   | V    | -                                              | PRQ-33   |

| Extended supply voltage for operating range | V <sub>S(ext)</sub>       | 4.5  | _      | 36   | V    | -                                              | PRQ-71   |

| Currents                                    | 1                         | 1    | -      |      |      |                                                |          |

| Channel output current                      | I <sub>SENSEx(func)</sub> | 5    | _      | 150  | mA   | -                                              | PRQ-223  |

| Power dissipation                           |                           | •    |        |      |      |                                                |          |

| Max. static and dynamic power dissipation   | P <sub>max</sub>          | _    | _      | 1.5  | W    | $T_{\rm A}$ = 85°C and $R_{\rm thJA}$ = 40 K/W | PRQ-178  |

| Temperatures                                |                           | •    |        |      | •    |                                                |          |

| Junction temperature                        | $T_{J(func)}$             | -40  | _      | 150  | °C   | -                                              | PRQ-72   |

Note:

Within the functional or operating range, the IC operates as described in the circuit description. Within the Extended Operation range, parameters deviations are possible. The electrical characteristics are specified within the conditions given in the electrical characteristics table.

### 4.3 Thermal resistance

Note:

This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to www.jedec.org

#### Table 5 Thermal resistance

| Parameter                         | Symbol             |      | Values |      |     | Note or condition           | P-Number |

|-----------------------------------|--------------------|------|--------|------|-----|-----------------------------|----------|

|                                   |                    | Min. | Тур.   | Max. |     |                             |          |

| Junction to top                   | $\Psi_{JTOP}$      | _    | 7      | _    | K/W | 1)                          | PRQ-262  |

| Junction to case                  | R <sub>thJC</sub>  | _    | 6      | _    | K/W | 2)                          | PRQ-263  |

| Junction to ambient<br>1s0p board | R <sub>thJA1</sub> | -    | 61     | _    | K/W | 3)<br>T <sub>A</sub> = 85°C | PRQ-264  |

| Junction to ambient<br>2s2p board | R <sub>thJA2</sub> | -    | 40     | -    | K/W | 4)<br>T <sub>A</sub> = 85°C | PRQ-265  |

<sup>1)</sup> Specified  $\Psi_{\text{JTOP}}$  is derived under natural convention conditions and provide a correlation between the junction temperature and the temperature on the package top surface.  $T_{\text{A}} = 85^{\circ}\text{C}$ . Total power dissipation = 1.5 W

#### **Datasheet**

#### 4 General product characteristics

- 2) Specified  $R_{\text{thJC}}$  is simulated at natural convention on a cold plate setup (all pins and exposed pad are fixed at ambient temperature).  $T_A = 85^{\circ}\text{C}$ . Total power dissipation = 1.5 W

- 3) Specified  $R_{thJA1}$  is generated in accordance with JEDEC JESD51-3 standards at natural convection on FR4 1s0p board. The simulation has been performed on a 76.2 x 114.3 x 1.5 mm board with 70  $\mu$ m, 300 mm<sup>2</sup> cooling area. Total power dissipation 1.5W distributed statically and homogenously over all power stages

- Specified  $R_{\text{thJA2}}$  is generated in accordance with JEDEC JESD51-5,-7 standards at natural convection on FR4 2s2p board. The simulation has been performed on a 76.2 x 114.3 x 1.5 mm board with 2 inner copper layers ( 2 x 70  $\mu$ m Cu, 2 x 35  $\mu$ m Cu). A total of six thermal via (Ø = 0.3 mm, plating 25  $\mu$ m) is placed under the exposed pad contacting the first inner copper layer. Total power dissipation 1.5W distributed statically and homogenously over all power stages

5 Internal supply

### 5 Internal supply

This chapter describes the internal supply, its main parameters and functionality.

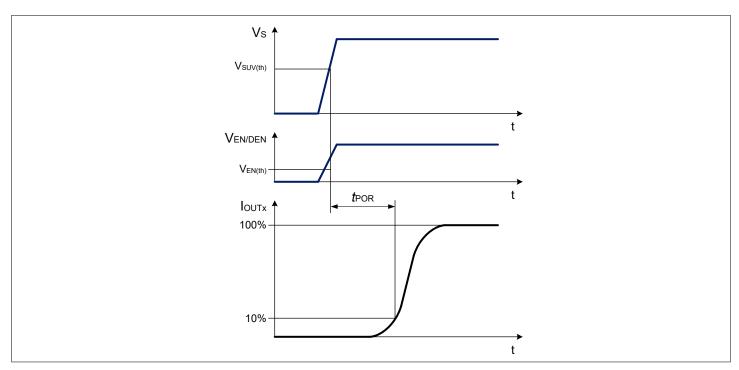

### 5.1 Description

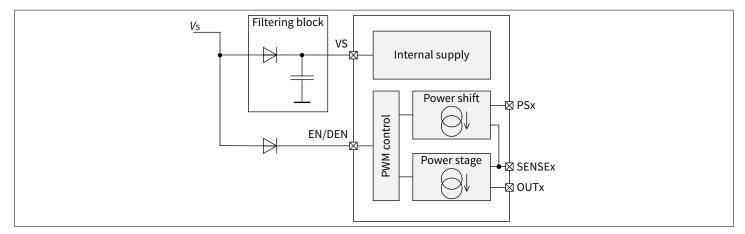

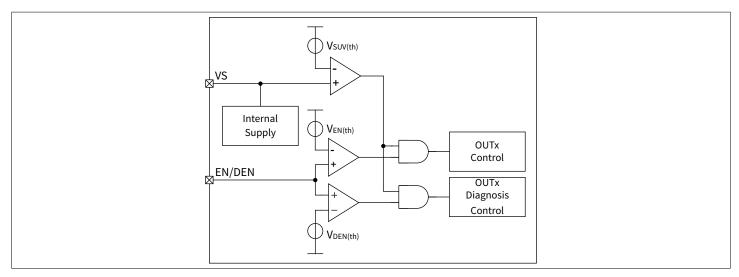

As soon as the voltage applied at the supply pin VS is above  $V_{\text{SUV(th)}}$  and the voltage applied at the EN/DEN pin is above  $V_{\text{EN(th)}}$ , the device is ready to deliver output current from the output stage after the power on reset time  $t_{\text{POR}}$ . When the supply voltage  $V_{\text{S}}$  is below the threshold  $V_{\text{SUV(th)}}$ , the internal Power-ON-Reset (POR) function holds the device in reset state.

The power on reset time  $t_{POR}$  has to be taken into account under relevant application conditions, i.e. with PWM control from VS.

Figure 3 Power on reset timing diagram

If the voltage applied at the EN/DEN pin is below  $V_{\text{EN(th)}}$  for more than  $t_{\text{SLEEP}}$  the device enters sleep mode. In this state all internal functions are switched off and the current consumption is reduced to  $I_{\text{VS(sleep)}}$ .

#### 5.2 Electrical characteristics

#### Table 6 Electrical characteristics

| Parameter                                   | Symbol                  | Values |      |      | Unit | Note or condition                                                            | P-Number |

|---------------------------------------------|-------------------------|--------|------|------|------|------------------------------------------------------------------------------|----------|

|                                             |                         | Min.   | Тур. | Max. |      |                                                                              |          |

| Current consumption, sleep mode             | I <sub>VS(sleep)</sub>  | -      | _    | 3    | μΑ   | $V_{\text{EN/DEN}} = 0 \text{ V}$ $T_{\text{J}} = 150^{\circ}\text{C}$       | PRQ-85   |

| Current consumption, active mode (no fault) | I <sub>VS(active)</sub> | -      | 2.5  | 3.5  | mA   | $V_{\rm EN/DEN}$ = 5.5 V<br>$V_{\rm ACC/PWMI}$ = 2.4 V<br>IREF pin left open | PRQ-154  |

### **Datasheet**

5 Internal supply

## Table 6 (continued) Electrical characteristics

| Parameter                                                   | Symbol                          | Values |      |      | Unit | Note or condition                                                                                                                     | P-Number |

|-------------------------------------------------------------|---------------------------------|--------|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                             |                                 | Min.   | Тур. | Max. |      |                                                                                                                                       |          |

| Current consumption during fault condition (1-fail-all-OFF) | I <sub>VS(fault,</sub><br>ERRN) | -      | -    | 850  | μΑ   | $V_{\text{EN/DEN}} = 5.5 \text{ V}$ $V_{\text{ERRN}} = 0 \text{ V}$ D pin open                                                        | PRQ-87   |

| VS undervoltage threshold                                   | V <sub>SUV(th)</sub>            | 3.5    | _    | 4.5  | V    | -                                                                                                                                     | PRQ-89   |

| EN/DEN outputs enable threshold                             | V <sub>EN(th)</sub>             | 0.6    | _    | 1.8  | V    | -                                                                                                                                     | PRQ-159  |

| EN/DEN outputs enable hysteresis                            | V <sub>EN(hys)</sub>            | 80     | 120  | _    | mV   | 1)                                                                                                                                    | PRQ-160  |

| EN/DEN pull-down current                                    | I <sub>EN/DEN(PD)</sub>         | -      | _    | 5    | μΑ   | V <sub>EN/DEN</sub> = 3 V                                                                                                             | PRQ-161  |

| EN/DEN pull-down current                                    | I <sub>EN/DEN(PD)</sub>         | -      | -    | 150  | μΑ   | V <sub>EN/DEN</sub> = 18 V                                                                                                            | PRQ-371  |

| Power on reset delay time                                   | t <sub>POR</sub>                | -      | -    | 75   | μs   | $V_{\rm S}$ rising edge from 0 V to<br>8 V to 10% of output<br>current<br>$V_{\rm EN/DEN}$ = 5.5 V<br>$V_{\rm ACC/PWMI}$ $\geq$ 2.4 V | PRQ-164  |

| Sleep mode filter time                                      | $t_{\sf SLEEP}$                 | 15     | _    | 45   | ms   | -                                                                                                                                     | PRQ-109  |

<sup>1)</sup> Not subject to production test, specified by design

6 Power stage

### 6 Power stage

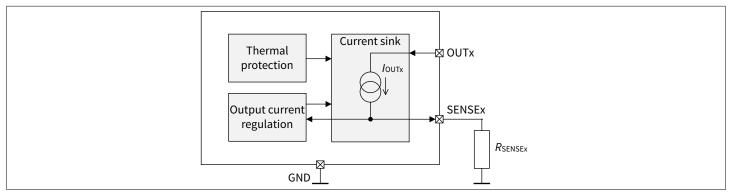

The power stages sinks from the OUTx pins an output current  $I_{\text{OUTx}}$  which is a function of the external sense resistors placed at SENSEx pins.

The overall maximum output current is limited by the power dissipation and used cooling areas.

Figure 4 Power stages block diagram

### 6.1 Output current regulation

The output current regulation block controls the LEDs current by regulating the voltage drop  $V_{SENSEx(reg)}$  on the external low-side current-sense resistors  $R_{SENSEx}$  placed between SENSEx pin and GND.

When the LEDs current is in regulation, the LEDs current value for each channel can be calculated by using the following equation:

$$I_{SENSEx} = \frac{V_{SENSEx(reg)}}{R_{SENSEx}} \tag{1}$$

For an operating output current control loop, the power stages dropout voltage ( $V_{DR,CSx}$ ), the  $V_{SENSEx(reg)}$  voltage, the forward voltage  $V_{D_RP}$  of the reverse polarity protection diode (when used) and the minimum supply voltage have to be considered in the LED string design.

To grant a proper control of the output current the following equation has to be satisfied:

$$V_S \ge V_{SENSEx(reg)} + V_{DR,CSx} + V_{LED,STRINGx} + V_{D,RP} \tag{2}$$

In case the supply voltage drops below the minimum requested by a particular channel, the LEDs current of that channel is no longer properly regulated. Consequently, a lower current is delivered and the voltage across the  $R_{\text{SENSEx}}$  resistor is lower than the expected  $V_{\text{SENSEx}(\text{reg})}$ .

**Note**: The  $R_{SENSE}$  has to be placed as close as possible to the pin VSENSE to avoid current regulation instability.

### 6.2 Thermal protection

A thermal protection function is integrated into the device to prevent IC damage under fault conditions described in the datasheet. Fault conditions are considered as "outside" the normal operating range. Protective functions are not designed for continuous operations.

The thermal protection function is achieved by temperature monitoring of the power stages. As soon as the junction temperature exceeds the overtemperature threshold  $T_{ISD}$ :

- The output currents are disabled by turning off the power stages

- The ERRN/DEN pin is pulled low

- The current consumption is below I<sub>VS(fault, ERRN)</sub>

#### **Datasheet**

6 Power stage

Once the junction temperature falls below  $T_{\rm JSD}$  -  $T_{\rm J(hys)}$ :

- The power stages recover to normal operation

- The ERRN/DEN pin is released

### 6.3 Electrical characteristics

#### Table 7 Electrical characteristics

| Parameter                             | Symbol                   | Values |      |      | Unit | Note or condition                     | P-Number |

|---------------------------------------|--------------------------|--------|------|------|------|---------------------------------------|----------|

|                                       |                          | Min.   | Тур. | Max. |      |                                       |          |

| Leakage currents                      |                          | 1      |      |      | ,    |                                       |          |

| Output leakage current                | I <sub>OUTx(leak)</sub>  | -      | _    | 1    | μΑ   | 1) T <sub>J</sub> = 85°C              | PRQ-308  |

|                                       |                          |        |      |      |      | <i>V</i> <sub>OUTx</sub> ≤ 16 V       |          |

|                                       |                          |        |      |      |      | $V_{ACC/PWMI} = 0 V$                  |          |

|                                       |                          |        |      |      |      | $V_{\rm EN/DEN} = 5.5 \rm V$          |          |

| Output leakage currents               | I <sub>OUTx(leak)</sub>  |        |      | 3    | μΑ   | T <sub>J</sub> = 150°C                | PRQ-309  |

|                                       |                          | _      | _    |      |      | <i>V</i> <sub>OUTx</sub> ≤ 16 V       |          |

|                                       |                          |        |      |      |      | $V_{ACC/PWMI} = 0 V$                  |          |

|                                       |                          |        |      |      |      | $V_{\rm EN/DEN}$ = 5.5 V              |          |

| Sense regulation voltag               | e accuracy               |        | ·    | ·    | •    |                                       |          |

| SENSEx voltage                        | V <sub>SENSEx(reg)</sub> | 384    | 400  | 416  | mV   | V <sub>ACC/PWMI</sub> ≥ 2.4 V         | PRQ-135  |

| regulation accuracy                   |                          |        |      |      |      |                                       |          |

| SENSEx voltage                        | $V_{SENSEx(reg)}$        | 95     | 100  | 105  | mV   | $V_{\text{ACC/PWMI}} = 0.9 \text{ V}$ | PRQ-137  |

| regulation accuracy                   |                          |        |      |      |      |                                       |          |

| SENSEx voltage                        | $V_{SENSEx(reg)}$        | 14     | 20   | 26   | mV   | $V_{\text{ACC/PWMI}} = 0.5 \text{ V}$ | PRQ-139  |

| regulation accuracy                   |                          |        |      |      |      |                                       |          |

| Power stage drop out                  |                          |        |      |      |      |                                       |          |

| Power stages drop out<br>voltage      | $V_{\mathrm{DR,CSx}}$    | _      | _    | 0.6  | V    | I <sub>OUTx</sub> = 150 mA            | PRQ-126  |

| Thermal protection thre               | esholds                  |        |      |      |      |                                       |          |

| Overtemperature<br>shutdown threshold | $T_{JSD}$                | 165    | 175  | 185  | °C   | 2)                                    | PRQ-131  |

| Overtemperature<br>hysteresis         | $T_{J(hys)}$             | 5      | 10   | 15   | °C   | 2)                                    | PRQ-132  |

- 1) Not subject to production test, specified by design

- 2) Not subject to production test, specified by design

7 Power shift

#### 7 Power shift

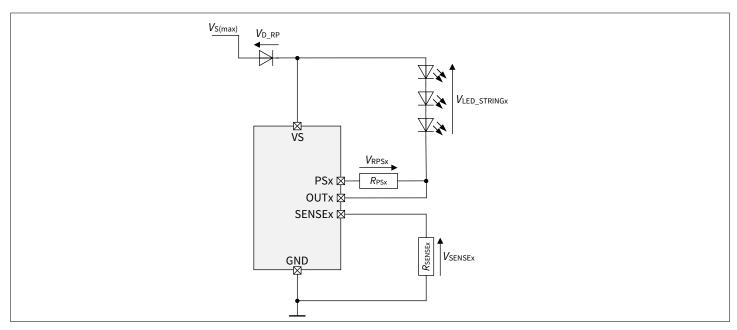

The device manages high power dissipation (higher than allowed by the thermal impedance  $R_{thJA}$  of the application) by separating the LED current into two current branches:

- One current sink path through an external drop element (power resistor) and the internal power shift

- One current sink path through the internal power stage

The current flowing into the power shift path and the one flowing into the power stage path are dynamically adjusted in order to obtain that the sum of  $I_{OUTx}$  and  $I_{PSx}$  currents is equal to the regulated  $I_{SENSEx}$  current.

The distribution of the current between the power shift path and the power stage path is defined by the power shift resistor value, the load and the applied battery voltage  $V_S$ .

In order to proper dimension the resistor value the following parameters have to be considered:

- Maximum current  $I_{PSx}$  intended to flow into the power shift path at maximum battery operative voltage  $V_{S(PEAK)}$

- Forward voltage V<sub>LED\_STRINGx</sub> of the output LED load and forward voltage V<sub>D\_RP</sub> of the reverse polarity protection diode

- Voltage drop on the internal power shift element  $(V_{PS-INTx} = I_{PSx} \times R_{PS-INT(ON)})$

- Regulated V<sub>SENSEx</sub> voltage

The resistor can then be calculated using the following formula:

$$R_{PSx} = \frac{V_{S(PEAK)} - V_{D\_RP} - V_{LED\_STRINGx} - V_{PS\_INTx} - V_{SENSEx}}{I_{PSx}}$$

(3)

Figure 5 Power shift resistor diagram

**Note**: Please consider that if the  $R_{PS}$  is set to 0  $\Omega$  all the LED current flows inside the internal power shift path leading to a possible overheating of the device up to the thermal shut-down.

### **Datasheet**

7 Power shift

## 7.1 Electrical characteristics

### Table 8Electrical characteristics

| Parameter                             | Symbol                                | Values |      |      | Unit | Note or condition                                                                                                           | P-Number |

|---------------------------------------|---------------------------------------|--------|------|------|------|-----------------------------------------------------------------------------------------------------------------------------|----------|

|                                       |                                       | Min.   | Тур. | Max. |      |                                                                                                                             |          |

| Power shift ON resistance             | R <sub>PS_INT(ON)</sub>               | -      | _    | 7.5  | Ω    | I <sub>PSx</sub> = 150 mA                                                                                                   | PRQ-276  |

| Power shift leakage current           | / <sub>PSx(leak)</sub>                | -      | -    | 1    | μА   | 1) $T_J = 85^{\circ}\text{C}$<br>$V_{PSx} \le 16 \text{ V}$<br>$V_{ACC/PWMI} = 0 \text{ V}$<br>$V_{EN/DEN} = 5.5 \text{ V}$ | PRQ-280  |

| Power shift leakage<br>current        | / <sub>PSx(leak)</sub>                | -      | -    | 3    | μА   | $T_{\rm J}$ = 150°C<br>$V_{\rm PSx} \le 16 \text{ V}$<br>$V_{\rm ACC/PWMI}$ = 0 V<br>$V_{\rm EN/DEN}$ = 5.5 V               | PRQ-289  |

| Power shift ratio                     | I <sub>PSx</sub> /I <sub>SENSEx</sub> | 0.95   | -    | -    | _    | $V_{PSx} - V_{SENSEx} > 1.5 \text{ V}$<br>$V_{ACC/PWMI} \ge 0.9 \text{ V}$                                                  | PRQ-281  |

| SENSEx voltage regulation accuracy    | V <sub>SENSEx(reg)</sub>              | 384    | 400  | 416  | mV   | V <sub>ACC/PWMI</sub> ≥ 2.4 V                                                                                               | PRQ-409  |

| SENSEx voltage regulation accuracy    | V <sub>SENSEx(reg)</sub>              | 95     | 100  | 105  | mV   | $V_{\text{ACC/PWMI}} = 0.9 \text{ V}$<br>$I_{\text{SENSE}} > 20 \text{ mA}$                                                 | PRQ-411  |

| SENSEx voltage<br>regulation accuracy | V <sub>SENSEx(reg)</sub>              | 14     | 20   | 28   | mV   | $V_{\text{ACC/PWMI}} = 0.5 \text{ V}$<br>$I_{\text{SENSE}} > 20 \text{ mA}$                                                 | PRQ-415  |

<sup>1)</sup> Not subject to production test, specified by design

8 PWM control

#### 8 PWM control

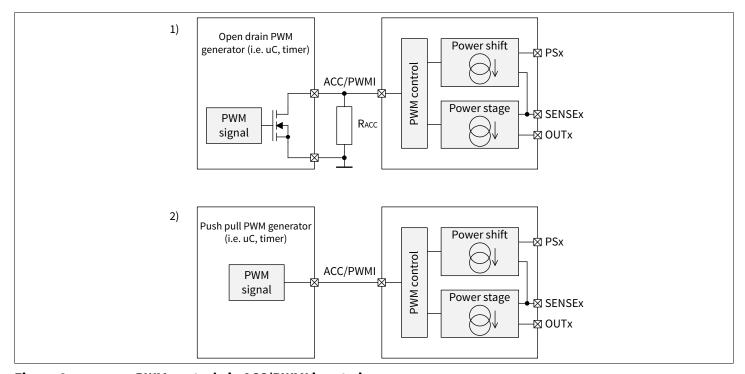

PWM dimming is adopted to vary LEDs brightness with greatly reduced chromaticity shift. PWM dimming achieves brightness reduction by varying the duty cycle of a constant current in the LED string.

The PWM modulation is performed via the ACC/PWMI pin. The power stages and the power shift blocks are disabled if the voltage applied on the ACC/PWMI pin is lower than  $V_{\text{PWM}(\text{OFF})}$  while they are enabled if the voltage applied on the ACC/PWMI pin is higher than  $V_{\text{PWM}(\text{ON})}$ .

In Figure 6 two examples of PWM dimming are shown via the ACC/PWMI input pin:

- 1. In case a resistor is needed on the ACC/PWMI input pin to apply analog current control (i.e. binning or thermal derating) the PWM signal can be applied using an open drain output from the PWM generator

- 2. In case the analog current control function is not needed a push-pull output from the PWM generator can be used to apply the PWM modulation

Figure 6 PWM control via ACC/PWMI input pin

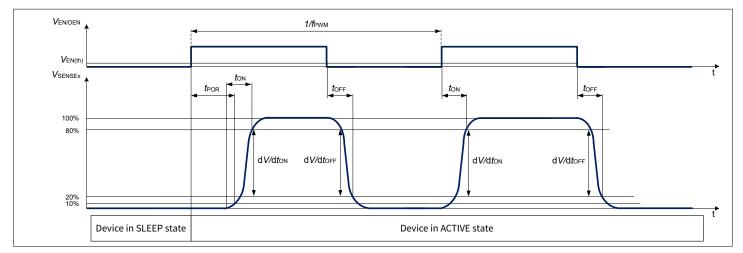

The PWM signal can be applied via the EN/DEN pin as well to allow PWM modulation from the battery line. Indeed by applying a proper filtering on the VS pin to avoid to trigger the VS undervoltage threshold, the  $t_{\rm POR}$  delay time would be applied only on the first PWM pulse generation after the exit from sleep state, like shown if Figure 9.

When applied on the EN/DEN pin the PWM signal has a frequency range  $f_{PWM}$  to avoid to turn-off the channels by triggering the  $t_{SLEEP}$  filter time.

The power stage and the power shift of all the channels are enabled if the voltage applied on the EN/DEN pin is higher than  $V_{\text{EN(th)}}$  while they are disabled if the voltage applied on the EN/DENx pin is lower than  $V_{\text{EN(th)}}$ .

8 PWM control

Figure 7 PWM control via EN/DEN input pin

When the voltage applied on the ACC/PWMI pin is below  $V_{PWM(OFF)}$ , the load diagnostic is disabled unless a fault was previously detected.

As well, when the voltage applied on the EN/DEN pin is below  $V_{\text{DEN(th)}}$ , the load diagnostic is disabled unless a fault was previously detected.

In particular, if a fault is already present when the voltage applied on the ACC/PWMI pin is below  $V_{\text{PWM}(\text{OFF})}$  or the voltage applied on EN/DEN pin is below  $V_{\text{DEN}(\text{th})}$  the diagnostic is kept active until the fault condition disappears, after that it is then disabled.

The PWM control block implements a slope rate control of the  $V_{\text{SENSEx}}$  voltages in order to improve EMC performances. The slew rate timings are defined by  $dV/dt_{\text{ON}}$  and  $dV/dt_{\text{OFF}}$  parameters.

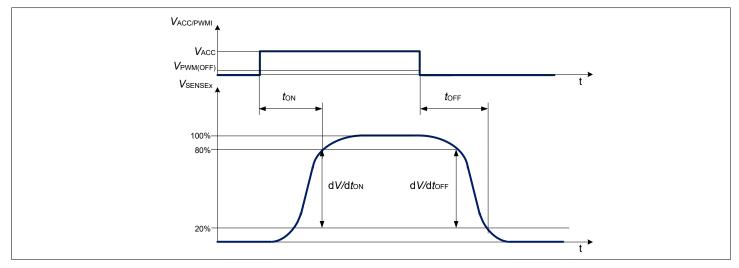

Figure 8 PWMI control timing diagram for  $V_{ACC/PWMI} \ge 2.4 \text{ V}$

#### 8 PWM control

Figure 9 PWM control on EN/DEN timing diagrams for  $V_{ACC/PWMI} \ge 2.4 \text{ V}$

## 8.1 Electrical characteristics

#### Table 9 Electrical characteristics

| Parameter                | Symbol                | Values |      |      | Unit  | Note or condition                                                             | P-Number |

|--------------------------|-----------------------|--------|------|------|-------|-------------------------------------------------------------------------------|----------|

|                          |                       | Min.   | Тур. | Max. |       |                                                                               |          |

| PWM turn off threshold   | V <sub>PWM(OFF)</sub> | 0.35   | 0.4  | _    | V     | -                                                                             | PRQ-145  |

| PWM turn on threshold    | V <sub>PWM(ON)</sub>  | _      | _    | 0.45 | V     | -                                                                             | PRQ-261  |

| PWM frequency range      | $f_{PWM}$             | 100    | _    | _    | Hz    | 1)                                                                            | PRQ-146  |

| PWM turn on time         | t <sub>ON</sub>       | _      | _    | 20   | μs    | 1) V <sub>SENSEx</sub> rising to 80% of regulation                            | PRQ-356  |

|                          |                       |        |      |      |       | $V_{\text{ACC/PWMI}} \ge 2.4 \text{ V}$                                       |          |

| PWM turn off time        | t <sub>OFF</sub>      | _      | _    | 20   | μs    | <sup>1)</sup> V <sub>SENSEx</sub> falling to 20% of regulation                | PRQ-357  |

|                          |                       |        |      |      |       | V <sub>ACC/PWMI</sub> falling from ≥ 2.4 V to less than V <sub>PWM(OFF)</sub> |          |

| VSENSE rising slew rate  | dV/dt <sub>ON</sub>   | 15     | 35   | 50   | mV/μs | 1) V <sub>SENSEx</sub> rising from 20% to 80% of regulation                   | PRQ-358  |

|                          |                       |        |      |      |       | V <sub>ACC/PWMI</sub> ≥ 2.4 V                                                 |          |

| VSENSE falling slew rate | dV/dt <sub>OFF</sub>  | -50    | -35  | -15  | mV/μs | 1) V <sub>SENSEx</sub> falling from<br>80% to 20% of<br>regulation            | PRQ-359  |

|                          |                       |        |      |      |       | V <sub>ACC/PWMI</sub> falling from ≥ 2.4 V to less than V <sub>PWM(OFF)</sub> |          |

<sup>1)</sup> Not subject to production test, specified by design

9 Analog output current control

### 9 Analog output current control

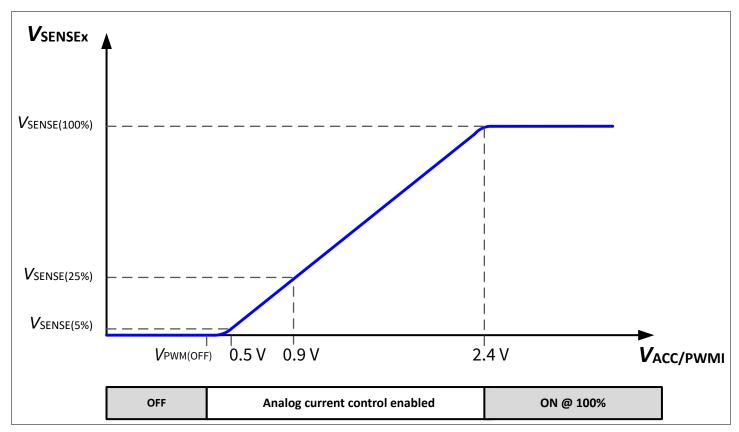

The analog output current control function adjusts the  $V_{\text{SENSEx}}$  voltages by sensing the applied voltage on the ACC/PWMI pin  $V_{\text{ACC/PWMI}}$ .

As described in Chapter 6 the output current provided by each channel is a direct function of the regulated voltage  $V_{\text{SENSEx.}}$  In this way by adjusting the voltage applied on the ACC/PWMI pin it is possible to control the output current of all the channels.

$$I_{SENSEx} = \frac{0.2 \times V_{ACC/PWMI} - 0.08 \quad V}{R_{SENSEx}} \tag{4}$$

The relation between the ACC/PWMI voltage  $V_{\text{ACC/PWMI}}$  and the respective regulated voltages  $V_{\text{SENSEx}}$  is shown in the Figure 10.

Figure 10 Analog output current control

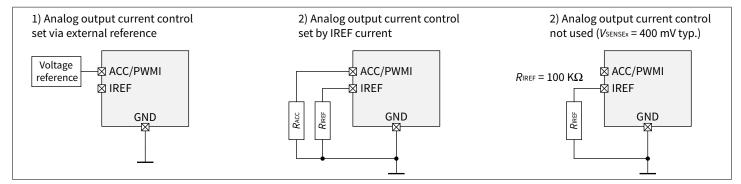

The voltage on ACC/PWMI can be set by applying an accurate external resistor on the ACC/PWMI pin. In case the resistor is placed in another PCB (i.e. binning resistor) it is recommended to add capacitor of 220 nF close to the ACC/PWMI pin.

The ACC/PWMI pin outputs a constant current based on the IREF output current and the ACC current ratio  $I_{ACC}/I_{IREF}$ .

**Note**: In case the analog output current control function is not needed it is recommended to put 100 k $\Omega$  pull-down resistor on the IREF pin to proper bias the ACC/PWMI voltage to avoid wrong  $V_{\text{SENSE}}$  setting.

## 9 Analog output current control

Figure 11 Analog output current control configurations

## 9.1 Electrical characteristics

#### Table 10 Electrical characteristics

| Parameter         | Symbol                              | Values |      |      | Unit | Note or condition                  | P-Number |

|-------------------|-------------------------------------|--------|------|------|------|------------------------------------|----------|

|                   |                                     | Min.   | Тур. | Max. |      |                                    |          |

| ACC current ratio | I <sub>ACC</sub> /I <sub>IREF</sub> | 4.85   | 5    | 5.15 | _    | 20 μA ≤ I <sub>IREF</sub> ≤ 250 μA | PRQ-253  |

#### **Datasheet**

10 Current reference generation

### 10 Current reference generation

The current reference generation block, outputs an accurate output reference current with low temperature shift. The voltage on the IREF pin is regulated in the  $V_{IREF}$  range.

It turns out that the reference current can be set by placing an external resistor from IREF pin to GND and can be calculated using the following formula:

$$I_{IREF} = \frac{V_{IREF}}{R_{IREF}} \tag{5}$$

**Note**: The R<sub>IREF</sub> has to be placed as close as possible to the pin IREF to avoid current regulation instability.

### 10.1 Electrical characteristics

#### Table 11 Electrical characteristics

| Parameter              | Symbol            | Values |      |       | Unit | Note or condition | P-Number |

|------------------------|-------------------|--------|------|-------|------|-------------------|----------|

|                        |                   | Min.   | Тур. | Max.  |      |                   |          |

| IREF regulated voltage | V <sub>IREF</sub> | 1.164  | 1.2  | 1.236 | V    | -                 | PRQ-268  |

| IREF current range     | I <sub>IREF</sub> | _      | _    | 250   | μΑ   | -                 | PRQ-269  |

| IREF capacitance       | C <sub>IREF</sub> | _      | _    | 0.22  | nF   | 1)                | PRQ-273  |

<sup>1)</sup> Not subject to production test, specified by design

### 11 Load diagnostics

Several diagnosis features are integrated:

- Open load detection (OL)

- Short to supply detection (SC)

- Power shift short to supply detection (SC)

- Overtemperature thermal detection (OT)

The behavior of the device during overload conditions that lead to an excess of internal heating, up to overtemperature condition, is already described in chapter Thermal protection.

An open load condition is detected if the voltage across the power stage  $V_{DRX} = V_{OUTx} - V_{SENSEx}$  is below the threshold  $V_{DR(OL)}$  for at least a filter time  $t_{fault}$ .

A short to supply condition is detected if the output voltage drop over one of the loads  $V_S$  -  $V_{OUTx}$  is below the threshold  $V_{OUT(SC)}$  for at least a filter time  $t_{fault}$ .

A power shift short to supply condition is detected if the power shift voltage drop  $V_S$  -  $V_{PSX}$  is below the threshold  $V_{PS(SC)}$  for at least a filter time  $t_{fault}$ .

If an OL condition is detected on the OUT pin or a SC condition is detected on one of the OUT or PS pins, a pull-down current  $I_{\text{OUT}(\text{fault})}$  flows inside the OUT pin replacing the configured output current. Only in case of 1-fail-all-OFF configuration (D pin open or connect to a capacitor) any further fault on additional channels leads to turn-off the channel without replacing the configured output current with the  $I_{\text{OUT}(\text{fault})}$ .

It turns out that in case of multiple faults on different channels of the same device configured with the 1-fail-all-OFF fault management, only one channel at time will provide the  $I_{OUT(fault)}$  current.

Note:

The  $I_{OUT(fault)}$  current is limited by the actual load impedance, e.g. it is reduced to zero with an ideal open load.

### 11.1 Diagnostics enable

As soon as the voltage applied at the supply pin VS is above  $V_{SUV(th)}$  and the voltage applied to the EN/DEN pin is above  $V_{DEN(th)}$ , the device is ready to detect and report fault conditions via ERRN/DEN pin.

There are several possibilities to program the output enable and diagnosis enable via EN/DEN pin, like a resistor divider from VS to GND, a Zener diode from EN/DEN to VS and also a logic control pin (e.g. from a microcontroller output).

Figure 12 EN/DEN block diagram

### 11.2 ERRN/DEN pin

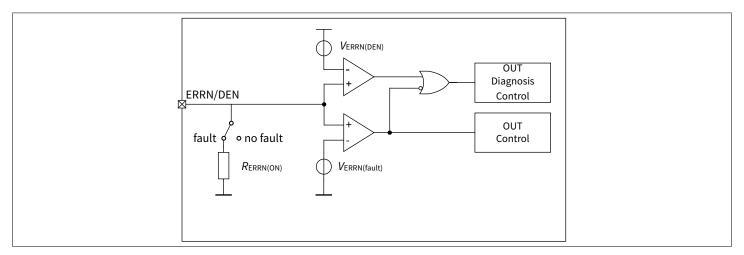

The device is able to report a detected failure in one of its driven loads and react to a fault detected by another LED driver in the system if a shared error network is implemented (i.e. driving LED chains of the same light function). This is possible with the usage of an external pull-up resistor, allowing multiple devices to share the open-drain diagnostic output pin ERRN/DEN. All devices sharing a common error network are capable to detect the fault from any of the channels driven by the Basic+ family.

The open-drain ERRN/DEN pin applies a pull-down resistance  $R_{\text{ERRN}(ON)}$  towards GND when a fault condition is detected for at least a filter time  $t_{\text{fault}}$ . Therefore, an active low state can be detected at ERRN/DEN pin when  $V_{\text{ERRN}} < V_{\text{ERRN}(fault)}$  and the relative faulty output channel is switched off.

Similarly, when the fault is removed, ERRN/DEN pin is back in high impedance state and the channel reactivation is completed as illustrated in Figure 13.

Figure 13 ERRN/DEN pin block diagram

To enable the possibility to decouple the  $V_{\text{DEN(th)}}$  threshold from the  $V_{\text{EN(th)}}$  threshold to have the device turning on as soon as needed independently from the diagnostic enable threshold,  $V_{\text{DEN(th)}}$ , the DEN functionality is duplicated on the ERRN/DEN pin.

The diagnostic reporting on ERRN/DEN pin and "open load", "short to supply" and the "power shift short to supply" protections are disabled, unless a fault was previously detected, as soon as one of the following condition is verified:

- The voltage on the ERRN/DEN pin is  $V_{\text{ERRN(fault)}} < V_{\text{ERRN/DEN}} \le V_{\text{ERRN(DEN)}}$

- The voltage on EN/DEN pin is below V<sub>DEN(th)</sub>

In addition the "open load" protection is disabled as well in case the voltage on the ERRN/DEN pin is  $V_{\text{ERRN/P}} \leq V_{\text{ERRN(fault)}}$  on all the channels that are not already in a fault condition.

When the ERRN/DEN pin applies a pull-down resistor  $R_{\text{ERRN}(ON)}$  towards GND the  $V_{\text{ERRN}(DEN)}$  threshold is masked to avoid unwanted toggling of the voltages on the ERRN/DEN pin.

#### 11.3 D pin

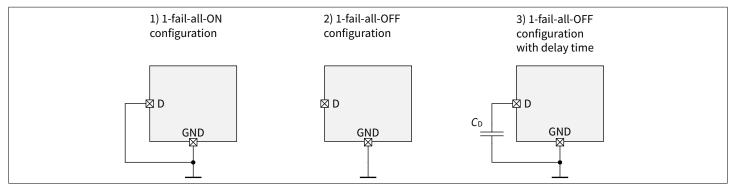

The D pin is designed for two main purposes:

- To react to error conditions in LED arrays according to the implementation fault management policy, in systems where multiple LED chains are used for a given function as illustrated in Figure 14

- To extend the channel's deactivation delay time of a value t<sub>D</sub>, adding a small signal capacitor from the D-pin to GND. In this way, an unstable or noisy fault condition may be prevented from switching off all the channels of a given light function (i.e. driven by several ICs sharing the same error network)

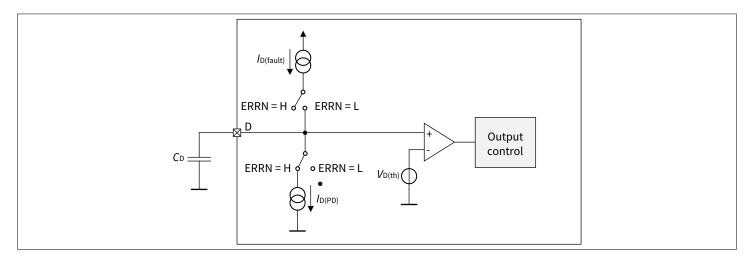

The functionality of the D-pin is shown in the simplified block diagram illustrated in Figure 15.

Figure 14 D pin configurations

Figure 15 D pin block diagram

In normal operative status (no fault) a pull-down current  $I_{D(PD)}$  is sunk from the D-pin to GND.

If there is a fault condition (for at least a filter time  $t_{\text{fault}}$ ) in one of the LED channels driven by the IC or in any of the devices sharing the same ERRN error network line, a pull-up current  $I_{\text{D(fault)}}$  is instead sourced from the D-pin.

If a capacitive or open load is applied at this pin (1-fail-all-OFF), its voltage starts rising. When  $V_{D(th)}$  is reached at D-pin, all the channels driven by the device are switched off and if other devices share the same ERRN/DEN and D-pins nodes, all the devices turn their outputs off.

Alternatively, if the D-pin is tied to GND (1-fail-all-ON), only the channel that has been detected with a fault is safely deactivated.

The capacitor value used at the D-pin,  $C_D$ , sets the delay times  $t_{D(\text{set/reset})}$  according to the following equations:

$$t_{D(set)} = \frac{C_D \times V_{D(th)}}{I_{D(fault)}} \tag{6}$$

$$t_{D(reset)} = \frac{C_D \times \left(V_{D(CL)} - \left(V_{D(th)} - V_{D(hys)}\right)\right)}{I_{D(PD)}} \tag{7}$$

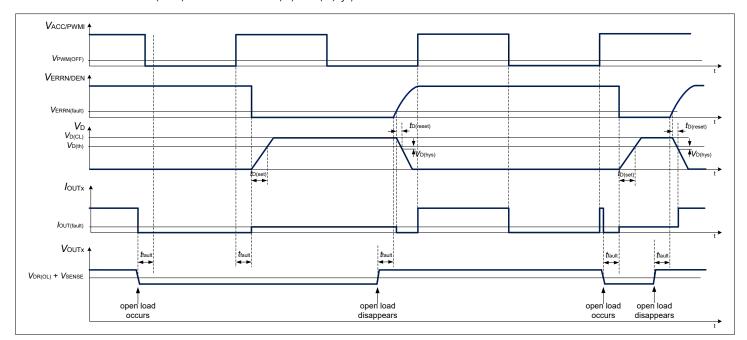

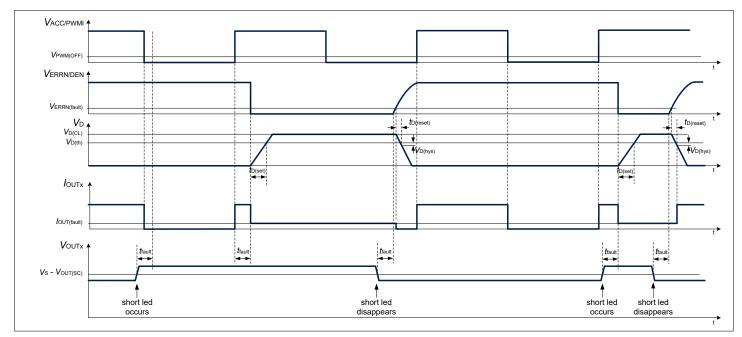

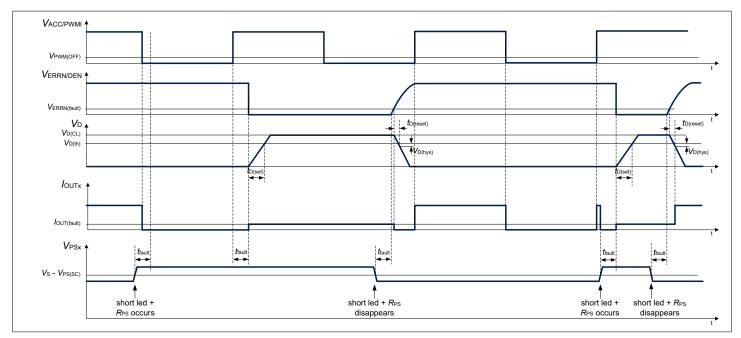

## 11.4 Fault management

With D pin open or connected with a capacitor to GND configuration, it is possible to switch off all the channels which share a common error network, without the need of an auxiliary microcontroller. For more details refer also to the timing diagram.

If there is a fault condition at the output or the power shift, the ERRN/DEN pin applies a pull-down resistance  $R_{\text{ERRN}(ON)}$  towards GND and (with proper dimensioning of the external pull-up resistor) reaches a voltage level below  $V_{\text{ERRN}(fault)}$ . After  $t_{\text{D}(\text{set})}$ , the voltage  $V_{\text{D}(\text{th})}$  is reached at D pin. The ERRN/DEN low voltage can also be used as input signal for a microcontroller to perform the desired diagnosis policy.

The OL and SC error conditions are not latched: as soon as the fault condition is no longer present, for at least a filter time  $t_{\text{fault}}$ , ERRN/DEN goes back to high impedance. When its voltage is above  $V_{\text{ERRN}(\text{fault})}$ , the D pin voltage starts decreasing and after  $t_{\text{D(reset)}}$  goes below  $(V_{\text{D(th)}} - V_{\text{D(th,hys)}})$ .

Figure 16 Open load condition timing diagram example in 1-fail-all-OFF configuration (D pin open or connected to external capacitor)

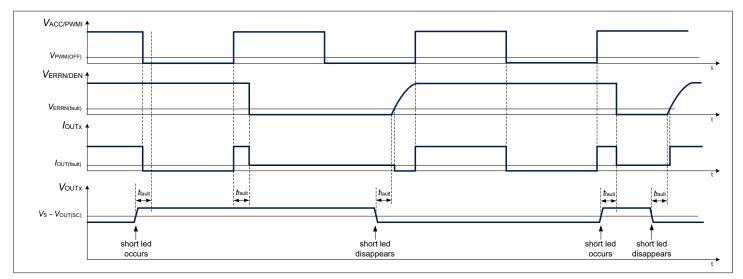

Figure 17 Output short to supply condition timing diagram example in 1-fail-all-OFF configuration (D pin open or connected to external capacitor)

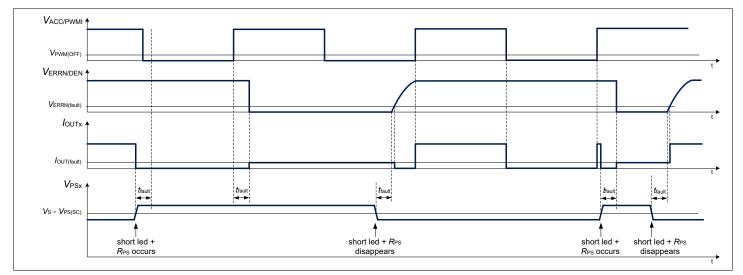

Figure 18 Power shift short to supply condition timing diagram example in 1-fail-all-OFF configuration (D pin open or connected to external capacitor)

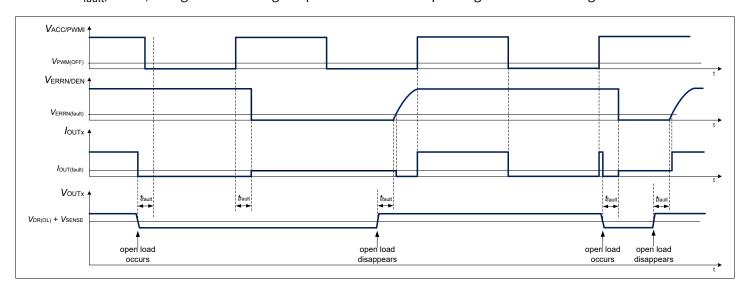

With D pin connected to GND, it is possible to deactivate only the channel under fault condition, still sharing ERRN pin in a common error network with other devices of Basic+ family.

If there is a fault condition at the output or the power shift, the ERRN pin applies a pull-down resistance  $R_{\text{ERRN}(ON)}$  to ground and the voltage level on this pin will drop below  $V_{\text{ERRN}(\text{fault})}$  if the external pull-up resistor is properly dimensioned. The ERRN low voltage can also be used as input signal for a  $\mu$ C to perform the desired diagnosis policy.

The OL and SC error conditions are not latched: as soon as the fault condition is no longer present (for at least for a filter time  $t_{\text{fault}}$ ) ERRN/DEN goes back to high impedance and the output stages are activated again.

Figure 19 Open load condition timing diagram example in 1-fail-all-ON configuration (D pin shorted to GND)

Figure 20 Output short to supply condition timing diagram example in 1-fail-all-ON configuration (D pin shorted to GND)

Figure 21 Power shift short to supply condition timing diagram example in 1-fail-all-ON configuration (D pin shorted to GND)

### 11.5 Electrical characteristics

#### Table 12 Electrical characteristics

$V_S = V_{S(func)}$ ,  $T_J = T_{J(func)}$ , all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter            | Symbol                   | Values |      |      | Unit | Note or condition | P-Number |

|----------------------|--------------------------|--------|------|------|------|-------------------|----------|

|                      |                          | Min.   | Тур. | Max. |      |                   |          |

| ERRN/DEN pin         | ·                        |        |      |      | ,    |                   |          |

| ERRN fault threshold | V <sub>ERRN(fault)</sub> | 0.7    | _    | 0.9  | V    | -                 | PRQ-193  |

(table continues...)

### **Datasheet**

11 Load diagnostics

### Table 12 (continued) Electrical characteristics

$V_S = V_{S(func)}$ ,  $T_J = T_{J(func)}$ , all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                    | Symbol                         |      | Values |      | Unit | Note or condition                                                                                                                             | P-Number |

|----------------------------------------------|--------------------------------|------|--------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                              |                                | Min. | Тур.   | Max. |      |                                                                                                                                               |          |

| ERRN ON resistance                           | R <sub>ERRN(ON)</sub>          | -    | -      | 350  | Ω    | $I_{\text{ERRN/DEN}} = 2 \text{ mA}$ Fault condition $V_{\text{EN/DEN}} > V_{\text{DEN(th)}}$                                                 | PRQ-379  |

| ERRN diagnosis enable threshold              | V <sub>ERRN(DEN)</sub>         | 2.1  | _      | 2.3  | V    | -                                                                                                                                             | PRQ-255  |

| ERRN pull-down current                       | / <sub>ERRN_PD</sub>           | -    | -      | 2    | μΑ   | No fault condition $V_{\text{EN/DEN}} > V_{\text{DEN(th)}}$                                                                                   | PRQ-380  |

| Diagnosis enable                             |                                | 1    |        | -    | -    |                                                                                                                                               |          |

| DEN diagnosis enable threshold               | $V_{DEN(th)}$                  | 2.3  | -      | 2.7  | V    | -                                                                                                                                             | PRQ-244  |

| Protections                                  | •                              |      |        |      |      |                                                                                                                                               |          |

| OL detection threshold                       | $V_{\mathrm{DR}(\mathrm{OL})}$ | 0.2  | _      | 0.4  | V    | $V_{\rm EN/DEN} > V_{\rm DEN(th)}$<br>$V_{\rm ERRN/DEN} > V_{\rm ERRN(DEN)}$                                                                  | PRQ-285  |

| OUT SC detection<br>threshold                | V <sub>OUT(SC)</sub>           | 0.8  | _      | 1.35 | V    | $V_{\rm EN/DEN} > V_{\rm DEN(th)}$<br>$V_{\rm ERRN/DEN} > V_{\rm ERRN(DEN)}$                                                                  | PRQ-286  |

| PS SC detection<br>threshold                 | V <sub>PS(SC)</sub>            | 0.8  | _      | 1.35 | V    | $V_{\rm EN/DEN} > V_{\rm DEN(th)}$<br>$V_{\rm ERRN/DEN} > V_{\rm ERRN(DEN)}$                                                                  | PRQ-292  |

| Fault detection current                      | I <sub>OUT(fault)</sub>        | -    | -      | 650  | μΑ   | OL or SC fault condition $V_{\rm EN/DEN} > V_{\rm DEN(th)}$ $V_{\rm ERRN/DEN} < V_{\rm ERRN(fault)}$                                          | PRQ-294  |

| D pin                                        |                                |      |        |      | •    |                                                                                                                                               |          |

| Threshold voltage for function de-activation | $V_{\rm D(th)}$                | 1.4  | 1.7    | 2    | V    | $V_{\rm EN/DEN} > V_{\rm DEN(th)}$<br>$V_{\rm ERRN/DEN} > V_{\rm ERRN(DEN)}$                                                                  | PRQ-299  |

| Threshold hysteresis                         | V <sub>D(hys)</sub>            | 70   | -      | -    | mV   | $V_{\rm EN/DEN} > V_{\rm DEN(th)}$<br>$V_{\rm ERRN/DEN} > V_{\rm ERRN(DEN)}$<br>Not subject to<br>production test,<br>specified by design     | PRQ-300  |

| Fault pull-up current                        | I <sub>D(fault)</sub>          | 20   | 35     | 50   | μА   | OL or SC fault condition $V_{\text{EN/DEN}} > V_{\text{DEN(th)}}$ $V_{\text{ERRN/DEN}} < V_{\text{ERRN(fault)}}$ $V_{\text{D}} = 2 \text{ V}$ | PRQ-301  |

(table continues...)

### **Datasheet**

11 Load diagnostics

## Table 12 (continued) Electrical characteristics

| Parameter              | Symbol             | Values |      |      | Unit | Note or condition                                                                                                         | P-Number |

|------------------------|--------------------|--------|------|------|------|---------------------------------------------------------------------------------------------------------------------------|----------|

|                        |                    | Min.   | Тур. | Max. |      |                                                                                                                           |          |

| Pull-down current      | I <sub>D(PD)</sub> | 40     | 60   | 95   | μА   | No fault conditions $V_{\rm EN/DEN} > V_{\rm DEN(th)}$ $V_{\rm ERRN/DEN} > V_{\rm ERRN(DEN)}$ $V_{\rm D} = 1.4 \text{ V}$ | PRQ-302  |

| Internal clamp voltage | V <sub>D(CL)</sub> | 2      | -    | 3    | V    | OL or SC fault condition $V_{\rm EN/DEN} > V_{\rm DEN(th)}$ $V_{\rm ERRN/DEN} < V_{\rm ERRN(fault)}$ D-pin open           | PRQ-303  |

| Timings                |                    |        | ·    | ·    |      |                                                                                                                           |          |

| Fault to ERRN delay    | $t_{fault}$        | 40     | -    | 120  | μs   | $V_{\rm EN/DEN} > V_{\rm DEN(th)}$<br>$V_{\rm ERRN/DEN} > V_{\rm ERRN(DEN)}$                                              | PRQ-304  |

12 Application information

### 12 Application information

**Note**: The following information is given as an example for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

# 12.1 Application diagram

**Note**: This figure is a simplified example of an application circuit. The function must be verified in the application.

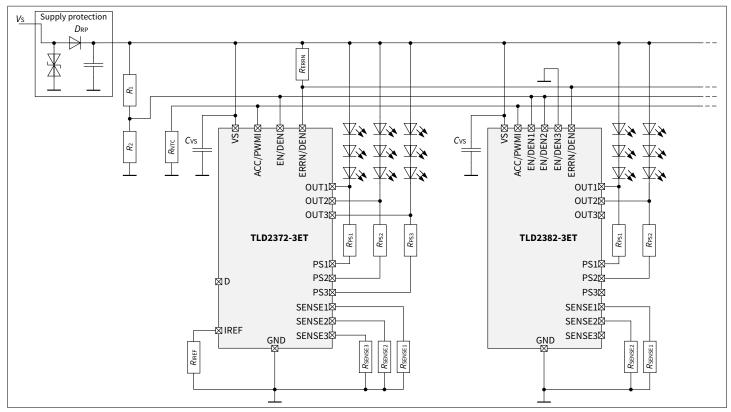

Figure 22 Application diagram example in a shared network with "one fail all off" fault management and central thermal derating

#### 12 Application information

Figure 23 Application diagram example for a 5 channels light function in a shared network with "one fail all off" fault management and central thermal derating

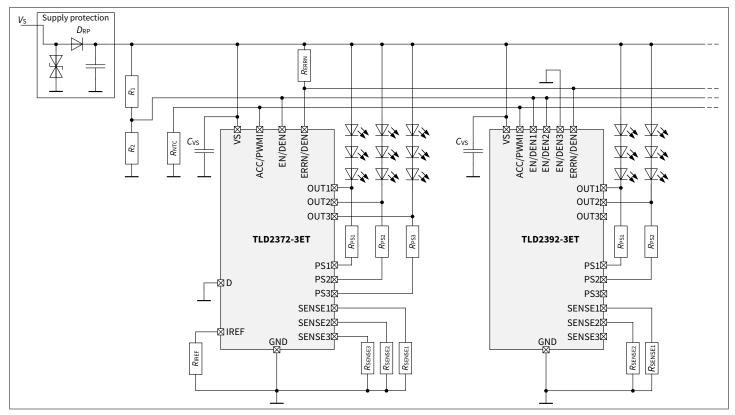

Figure 24 Application diagram example for a 5 channels light function in a shared network with "one fail all on" fault management and central thermal derating

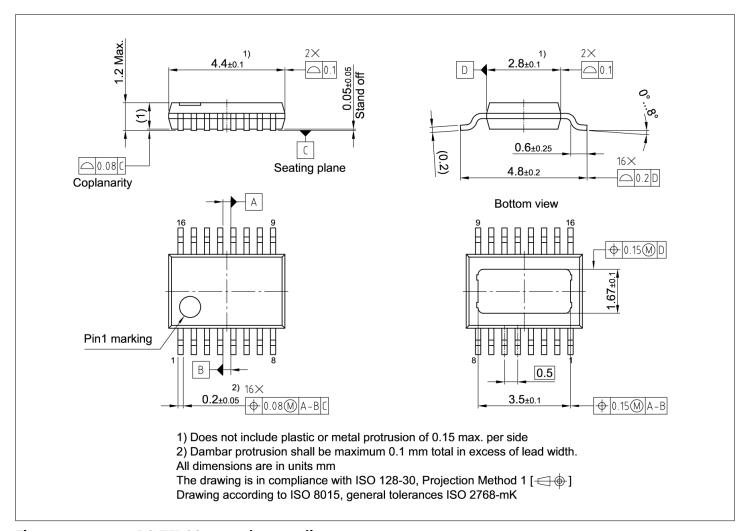

13 Package information

## 13 Package information

33

Figure 25 PG-TFDSO-16 package outline png

## **Datasheet**

Revision history

# **Revision history**

| Document version | Date of release | Description of changes   |

|------------------|-----------------|--------------------------|

| Rev. 1.00        | 2024-10-14      | Initial document release |

#### Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2024-10-14 Published by Infineon Technologies AG 81726 Munich, Germany

© 2024 Infineon Technologies AG All Rights Reserved.

Do you have a question about any aspect of this document?

${\bf Email: erratum@infineon.com}$

Document reference IFX-xdk1676899181382

#### Important notice

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

#### Warnings

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.