# **XDP<sup>™</sup> XDPP114x product family**

# Digital power supply controller for PWM and PFM applications

### Features

- Digital controller assisted high performance analog front ends and fully programmable ARM<sup>®</sup> Cortex<sup>™</sup>-M0 processor

- 100 MHz clock, 32-bit, 64 kB OTP, 32 kB RAM, 80 kB ROM

- High performance, low latency digital hardware control loop for single rail up to two phases

- High-speed voltage sense

- 100 MHz 11-bit ADC with 1.25 mV/ LSB

- Up to 2.1 V differential voltage range

- 200 MHz edge detection comparator

- High-speed current sense

- 100 MHz 9-bit ADC with 1 mV/LSB

- Configurable symmetrical positive and negative input voltage range or asymmetrical input

- 6 high-resolution Digital Pulse Width Modulated (DPWM) remappable outputs

- 78.125 ps pulse width resolution

- Adjustable dead-time between pairs for both rising and falling edges with 1.25 ns or 2.5 ns resolution

- Frequency range: 50 kHz to 2 MHz with 5 ns resolution

- 2 High-speed inputs for external fault shutdown or PWM edge control

- PWM edge alignment

- Trailing, leading, and dual-edge modulation

- Configurable feedback control

- Voltage mode, peak current mode

- Configurable modulation methods

- Pulse width modulation, phase shift modulation, frequency modulation

- Up to 11 GPIO pins

- Synchronization with external clock

- 4-channel, 10-bit, 0.926 Msps general purpose ADC

- 2.34 mV/LSB, input voltage range 2.4 V

- Communication peripherals

- 1 MHz I<sup>2</sup>C/PMBUS, full duplex SPI, full duplex UART

- 24-pin VQFN packages

- Operating temperature: -40°C to 125°C

# **Typical applications**

- Isolated/ non-isolated DC-DC PWM converters

- LLC converters

- Intermediate bus converters for Datacenter / computing system

- Power supplies for Telecom infrastructure/ Brick modules

# Product validation

#### **Product validation**

Fully qualified according to JEDEC for industrial applications.

## **Application features**

- Soft start with pre-bias (non-resonant topologies)

- Feed forward compensation for PWM topologies

- Active current sharing

- LLC features

- Hybrid soft start: PWM or phase-shift at the maximum frequency and frequency sweep

- Adaptive SR turn-off based on V<sub>DS</sub> sensing

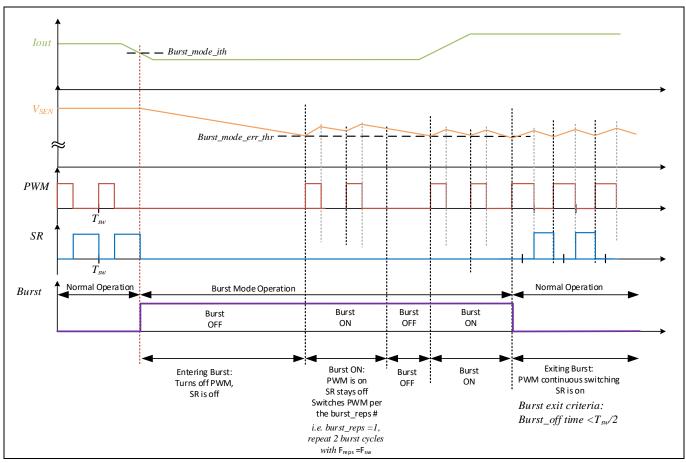

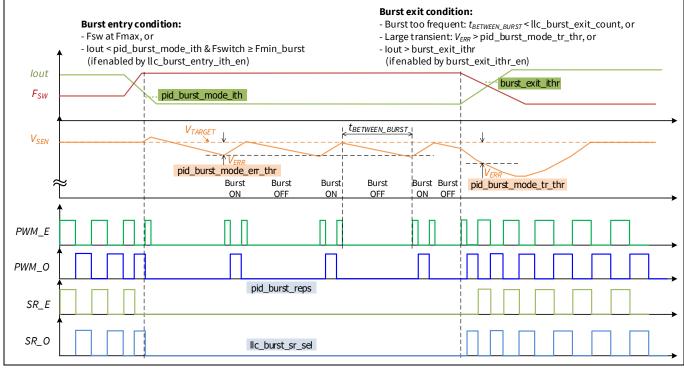

- Light load operation including:

- Burst mode at the maximum frequency

- Diode emulation (DE) mode

- Phase Shift duty cycle reduction at the maximum frequency for full-bridge LLC

- High efficiency and light load management

- Burst mode (except ACF topology)

- Phase dropping (interleave topologies)

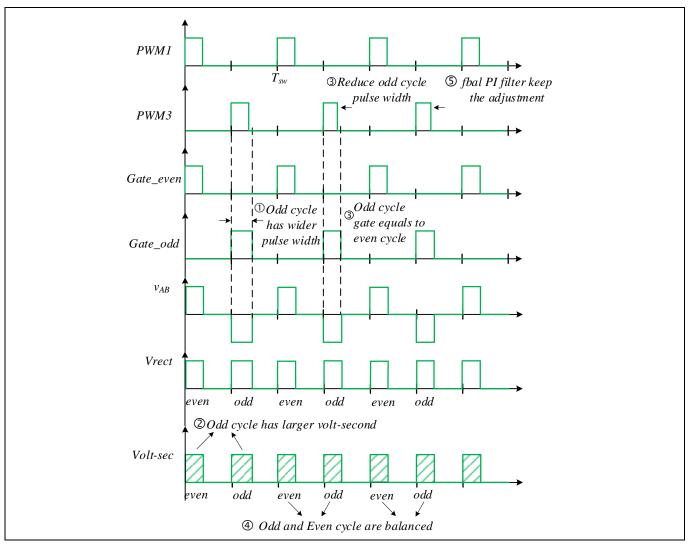

- Flux balancing

- Phase current balancing

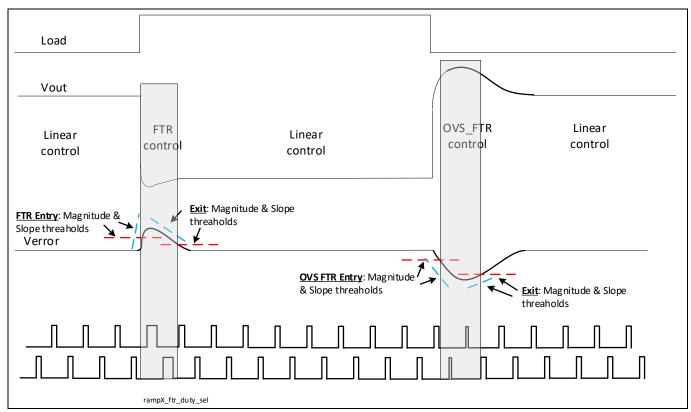

- Configurable non-linear PID and Fast Transient Response (FTR)

- Feature rich fault protections

- Programmable over and under voltage protection (OVP, UVP) thresholds and response

- Programmable over and under current protection (OCP, UCP) thresholds and response

- Programmable fast over-current protection and short circuit protection

- Programmable over and under temperature protection (OTP, UTP) thresholds and hysteresis

- Programmable positive/ negative peak current limit threshold

- Internal and external temperature sensor

- Feedback open loop protection

- Programmable blanking time

### **Ordering information**

#### Table 1Ordering information

| Base part<br>number | Package type             | Standard pack<br>form and Qty | Application                                                                             | Orderable part<br>number |

|---------------------|--------------------------|-------------------------------|-----------------------------------------------------------------------------------------|--------------------------|

| XDPP1140-100B       | VQFN (24)<br>4 mm x 4 mm |                               | Single phase topologies, supports flux balancing                                        | XDPP1140100BXUMA1        |

| XDPP1148-100B       |                          | Tape & reel, 5000             | Single phase or interleaved<br>topologies, supports current<br>balancing between phases | XDPP1148100BXUMA1        |

# Description

#### Description

The XDPP1140 and XDPP1148 are digital power supply controllers for AC/DC and DC/DC power converters. The controller has high performance analog front end, a unique architecture with optimized power-processing digital blocks, and built-in ready to use firmware which minimize firmware development effort. The state machine based configurable control loop architecture supports various modes of operation including PWM and PFM modulation, voltage mode and peak current mode control.

The XDPP114x includes a 32-bit, 100 MHz ARM<sup>®</sup> Cortex<sup>™</sup>-M0 RISC microcontroller sub-system that can be used for enhanced control, real-time monitoring, configuration of peripheral, and managing communications. It also allows firmware-based customization and implementation of housekeeping functions such as sequencing, blackbox data recording and interfacing.

The core power control functions are implemented by dedicated hardware or firmware pre-programmed in the device ROM, allows fast time to market. Additional programs can be stored and executed out of the nonvolatile memory OTP and RAM. Developers have full control of their application and firmware. System designers can develop and compile their customized firmware in any commonly used ARM<sup>™</sup> based develop environment.

The XDPP114x supports PMBus<sup>™</sup>1.4 subsets and includes UART, SPI and I2C communication interfaces. The PMBus<sup>™</sup> command set is runtime programmable, which allows config the commands on the fly.

The XDPP114x supports many commonly used AC-DC and DC-DC topologies such as, LLC, hard-switched full bridge and half bridge, phase shifted full bridge, active clamp forward, non-isolated buck, buck-boost, boost, interleaved buck, interleaved buck-boost, and interleaved boost topologies.

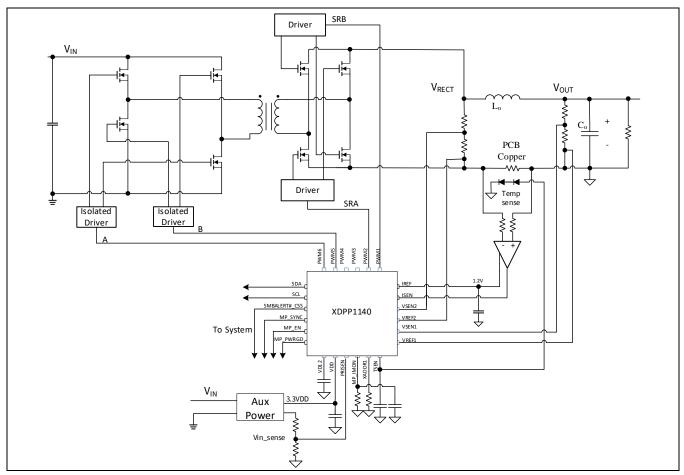

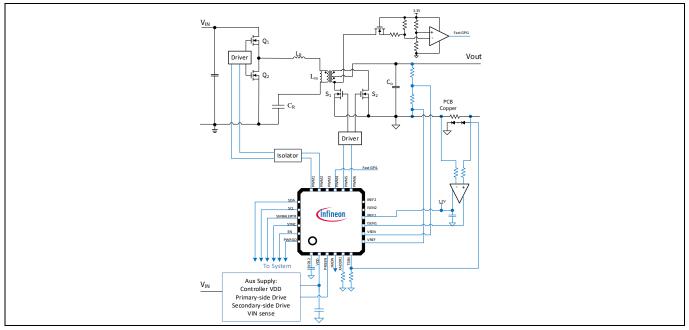

Figure 1 shows a typical application of the XDPP1140 device in a full-bridge to full-bridge converter.

Figure 1 Typical application diagram

Note:

In this datasheet, the reference XDPP114x applies to both the XDPP1140 and XDPP1148 versions of the product. While references to XDPP1140 or XDPP1148 specifically refer to the referenced version of the product.

### **Table of contents**

| Typical applications       1         Product validation       2         Application features       2         Ordering information       2         Description       3         Table of contents       4         1       Block diagram         2       Product selection matrix         3       Pin configuration and functions         3.1       XDPP1140-100B package         3.2       XDPP1148-100B package |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Application features.       2         Ordering information       2         Description matrix       7         3       Pin configuration and functions       8         3.1       XDPP1140-100B package       8                                                                                                                                                                                                  |

| Ordering information       2         Description       3         Table of contents       4         1       Block diagram         2       Product selection matrix         3       Pin configuration and functions         3.1       XDPP1140-100B package                                                                                                                                                      |

| Description       3         Table of contents       4         1       Block diagram       6         2       Product selection matrix       7         3       Pin configuration and functions       8         3.1       XDPP1140-100B package       8                                                                                                                                                           |

| Table of contents.       4         1       Block diagram.         2       Product selection matrix.         3       Pin configuration and functions.         3.1       XDPP1140-100B package                                                                                                                                                                                                                   |

| 1       Block diagram                                                                                                                                                                                                                                                                                                                                                                                          |

| <ul> <li>2 Product selection matrix</li></ul>                                                                                                                                                                                                                                                                                                                                                                  |

| <ul> <li><b>Pin configuration and functions</b></li> <li>XDPP1140-100B package</li> </ul>                                                                                                                                                                                                                                                                                                                      |

| 3.1 XDPP1140-100B package                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.1 XDPP1140-100B package                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                |

| יייייייייייייייייייייייייייייייייייי                                                                                                                                                                                                                                                                                                                                                                           |

| 4 Functionial description                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                               |

| 4.1.1 ARM <sup>®</sup> Cortex <sup>™</sup> – M0 core                                                                                                                                                                                                                                                                                                                                                           |

| 4.1.2 Memories                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4.1.3 Communication ports                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.1.3.1 I <sup>2</sup> C/PMBus                                                                                                                                                                                                                                                                                                                                                                                 |

| 4.1.3.2 SPI                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.1.3.3 UART                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.1.3.4 Address offset                                                                                                                                                                                                                                                                                                                                                                                         |

| 4.1.4 GPIO                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.1.5 Register map14                                                                                                                                                                                                                                                                                                                                                                                           |

| 4.2 Analog blocks and subsystems14                                                                                                                                                                                                                                                                                                                                                                             |

| 4.2.1 Power supply14                                                                                                                                                                                                                                                                                                                                                                                           |

| 4.2.2 Oscillator and PLL                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.2.2.1 The 3 <sup>rd</sup> ramp                                                                                                                                                                                                                                                                                                                                                                               |

| 4.2.3 Voltage sense AFE1                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.2.4 Current sense AFE2                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.2.5General purpose AFE3224.2.5.1IMON and active current sharing23                                                                                                                                                                                                                                                                                                                                            |

| 4.2.5.1     IMON and active current sharing                                                                                                                                                                                                                                                                                                                                                                    |

| 4.2.5.2 reinperature sense                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.2.6 Fast trigger input                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.2.7 Fast fault output                                                                                                                                                                                                                                                                                                                                                                                        |

| 4.3 Control loop subsystems                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.3.1 State diagram                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.3.2 Soft start                                                                                                                                                                                                                                                                                                                                                                                               |

| 4.3.2.1 Soft start for non-resonant topologies                                                                                                                                                                                                                                                                                                                                                                 |

| 4.3.2.2 Soft start for LLC converters                                                                                                                                                                                                                                                                                                                                                                          |

| 4.3.3 Shutdown                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4.3.4 Voltage mode control (VMC)                                                                                                                                                                                                                                                                                                                                                                               |

### Table of contents

| 4.3.5   | Peak current mode control (PCMC) non-resonant topologies | 29 |

|---------|----------------------------------------------------------|----|

| 4.3.6   | PID and control loop                                     |    |

| 4.3.7   | Frequency modulation (LLC)                               | 31 |

| 4.3.8   | Full-bridge LLC phase shift mode                         |    |

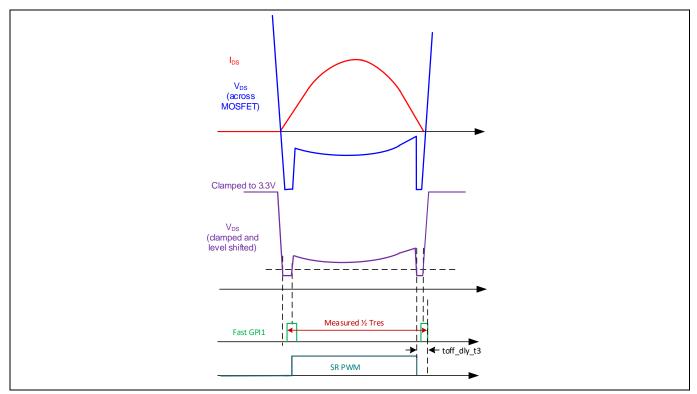

| 4.3.9   | LLC SR timing control                                    |    |

| 4.3.9.2 | 1 Fixed maximum on-time of SR                            | 32 |

| 4.3.9.2 | 2 Adaptive SR maximum on-time                            | 33 |

| 4.3.10  | Current sense estimator for non-resonant topologies      | 34 |

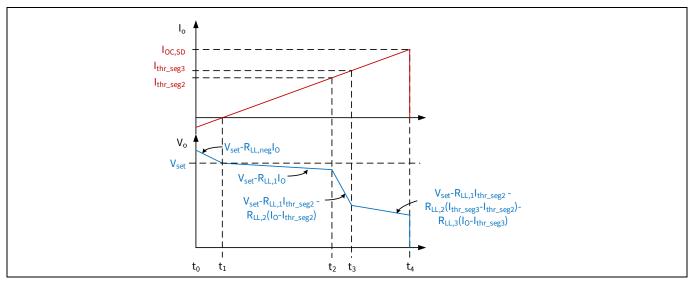

| 4.3.11  | Load-line (Droop)                                        | 35 |

| 4.3.12  |                                                          |    |

| 4.3.13  | Fast transient response (FTR) for bridge topologies      |    |

| 4.3.14  | Fast transient response (FTR) for buck                   | 37 |

| 4.3.15  | I                                                        |    |

| 4.3.16  | 6 Current balancing of XDPP1148                          |    |

| 4.3.17  | 3                                                        |    |

| 4.3.18  | Flux balancing of XDPP1140                               |    |

| 4.3.19  |                                                          |    |

| 4.3.19  |                                                          |    |

| 4.3.19  | · · · · · · · · · · · · · · · · · · ·                    |    |

| 4.3.20  | 0                                                        |    |

| 4.3.21  |                                                          |    |

| 4.4     | Protection and fault                                     | 42 |

| 5       | Electrical characteristics                               | 45 |

| 5.1     | Absolute maximum ratings                                 | 45 |

| 5.2     | ESD and MSL rating                                       | 45 |

| 5.3     | Thermal characteristics                                  | 45 |

| 5.4     | Recommended operating conditions                         | 46 |

| 5.5     | Electrical characteristics                               | 46 |

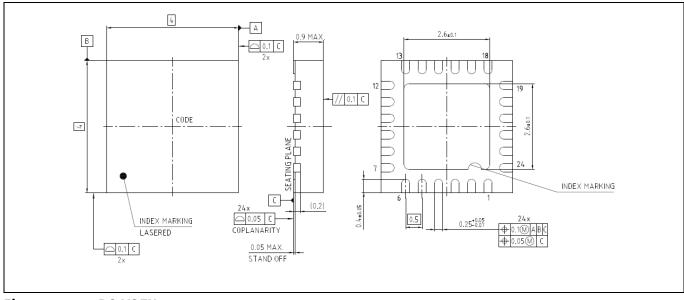

| 6       | Package information                                      | 51 |

| 6.1     | QFN 4x4 – 24pin                                          | 51 |

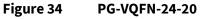

| 6.2     | Part marking                                             | 51 |

| 7       | Nomenclature                                             | 52 |

| Revis   | ion history                                              | 54 |

**Block diagram**

# 1 Block diagram

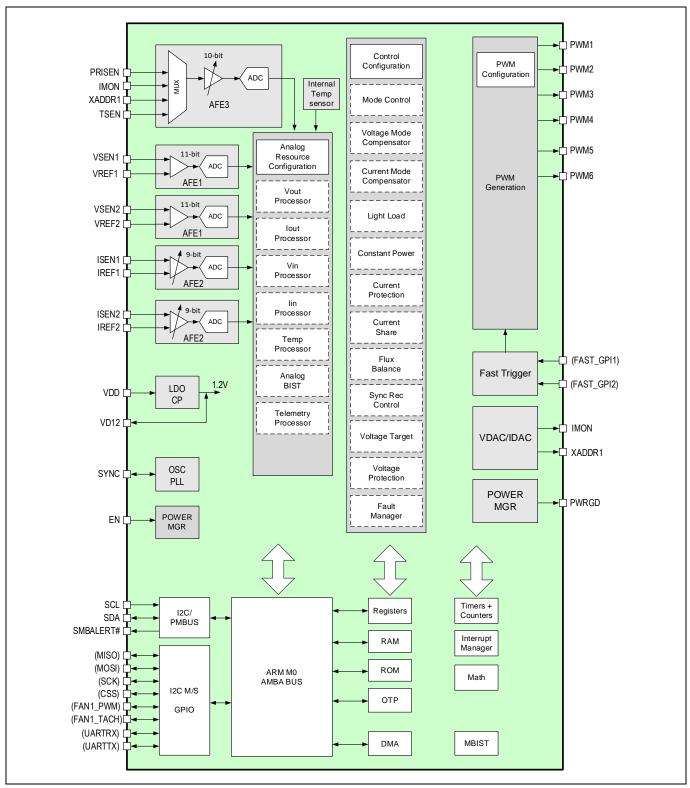

**Figure 2** shows a functional block diagram of the XDPP114x device architecture. Pin name in brackets indicates it is a secondary function of a multi-purpose pin. Details see **Table 7**.

Figure 2 Block diagram

Product selection matrix

# 2 Product selection matrix

#### Table 2Product selection table

| FEATURE                                            | XDPP1140-100B                  | XDPP1148-100B                  |

|----------------------------------------------------|--------------------------------|--------------------------------|

| ARM M0 core processor                              | 100 MHz                        | 100 MHz                        |

| High resolution DPWM outputs (78.125ps resolution) | 6                              | 6                              |

| Number of voltage sense ADC                        | 2                              | 1                              |

| Number of current sense ADC                        | 1                              | 2                              |

| General purpose ADC channels                       | 4                              | 4                              |

| ОТР                                                | 64 kB                          | 64 kB                          |

| RAM                                                | 32 kB                          | 32 kB                          |

| ROM                                                | 80 kB                          | 80 kB                          |

| DPWM switching frequency                           | Up to 2 MHz                    | Up to 2 MHz                    |

| SPI serial bus                                     | Yes                            | Yes                            |

| UART                                               | Yes                            | Yes                            |

| PMBus                                              | Yes                            | Yes                            |

| Watchdog                                           | Yes                            | Yes                            |

| On chip oscillator                                 | Yes                            | Yes                            |

| Sync in and sync out functions                     | Yes                            | Yes                            |

| Temperature sense inputs                           | 1                              | 1                              |

| Total GPIO (General purpose I/O pins)              | 11                             | 11                             |

| Package offering                                   | VQFN-24 (4x4 mm <sup>2</sup> ) | VQFN-24 (4x4 mm <sup>2</sup> ) |

3 Pin configuration and functions

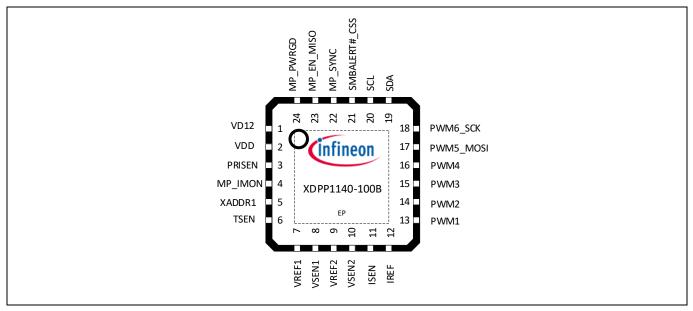

# 3.1 XDPP1140-100B package

#### Figure 3

XDPP1140-100B pin assignment

#### Table 3XDPP1140-100B pin definition

| Pin<br>No. | Name                                                                                      | Primary assignment                             | Alternate assignment | Configurable<br>GPIO |

|------------|-------------------------------------------------------------------------------------------|------------------------------------------------|----------------------|----------------------|

| 1          | VD12                                                                                      | 1.2 V supply bypass.                           |                      | -                    |

| 2          | VDD                                                                                       | 3.3 V main supply input                        |                      | -                    |

| 3          | PRISEN                                                                                    | Primary voltage sensing input                  | GPA1                 | -                    |

| 4          | MP_IMON     Output current monitor     GPA2/ SYNC / FAN1_TACH /<br>Fault / Fast GPI2 / EN |                                                | Yes                  |                      |

| 5          | XADDR1                                                                                    | Address 1                                      | GPA3                 | -                    |

| 6          | TSEN                                                                                      | Temperature sensing input                      | GPA4                 | -                    |

| 7          | VREF1                                                                                     | Differential voltage sensing 1, negative input |                      | -                    |

| 8          | VSEN1                                                                                     | Differential voltage sensing 1, positive input |                      | -                    |

| 9          | VREF2                                                                                     | Differential voltage sensing 2, negative input |                      | -                    |

| 10         | VSEN2                                                                                     | Differential voltage sensing 2                 |                      | -                    |

| 11         | ISEN                                                                                      | Differential current sensing                   |                      | -                    |

| 12         | IREF                                                                                      | Differential current sensing, negative input   |                      | -                    |

| 13         | PWM1                                                                                      | PWM1 output                                    | SYNC/ Fast_GPI1      | Yes                  |

Pin configuration and functions

| Pin<br>No. | Name             | Primary assignment                 | Alternate assignment                 | Configurable<br>GPIO |

|------------|------------------|------------------------------------|--------------------------------------|----------------------|

| 14         | PWM2             | PWM2 output                        | SYNC/ Fast_GPI2                      | Yes                  |

| 15         | PWM3             | PWM3 output                        | SYNC/ Fast_GPI1 / FAN1_TACH          | Yes                  |

| 16         | PWM4             | PWM4 output                        | SYNC/ Fast_GPI2 / FAN1_PWM           | Yes                  |

| 17         | PWM5_MOSI        | PWM5 output                        | SYNC/ UARTRX/ Fast_GPI1/<br>SPI_MOSI | Yes                  |

| 18         | PWM6_SCK         | PWM6 output                        | SYNC/ UARTTX/ Fast_GPI2/<br>SPI_SCK  | Yes                  |

| 19         | SDA              | I <sup>2</sup> C serial data line  |                                      | -                    |

| 20         | SCL              | I <sup>2</sup> C serial clock line |                                      | -                    |

| 21         | SMBALERT#_CSS    | PMBus alert                        | SYNC / Fault / CSS                   | Yes                  |

| 22         | MP_SYNC          | Synchronize pin                    | FAN1_PWM/ Fast GPI1/ Fault           | Yes                  |

| 23         | MP_EN_MISO       | Enable_Sleep control               | SYNC/ SPI MISO                       | Yes                  |

| 24         | MP_PWRGD         | Power good output                  | SYNC                                 | Yes                  |

|            | EP (exposed pad) | Ground pin                         |                                      | -                    |

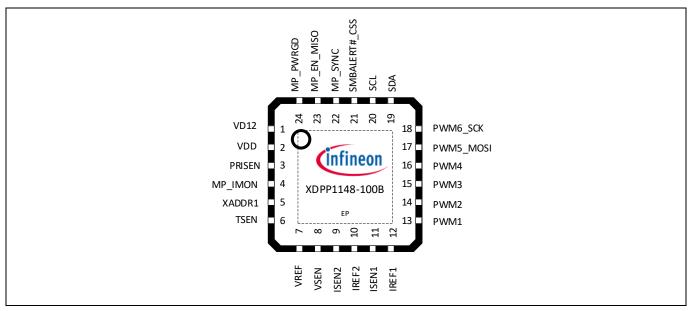

### 3.2 XDPP1148-100B package

#### Figure 4 XDPP1148-100B pin assignment

#### Table 4XDPP1148-100B pin definition

| Pin No. | Name   | Primary assignment            | Alternate assignment | Configurable<br>GPIO |

|---------|--------|-------------------------------|----------------------|----------------------|

| 1       | VD12   | 1.2 V supply bypass           |                      | -                    |

| 2       | VDD    | 3.3 V main supply input       |                      | -                    |

| 3       | PRISEN | Primary voltage sensing input | GPA1                 | -                    |

Pin configuration and functions

| Pin No. | Name             | Primary assignment                                      | Alternate assignment                               | Configurable<br>GPIO |

|---------|------------------|---------------------------------------------------------|----------------------------------------------------|----------------------|

| 4       | MP_IMON_EN       | Output current monitor                                  | GPA2/ SYNC / FAN1_TACH /<br>Fault / Fast GPI2 / EN | Yes                  |

| 5       | XADDR1           | Address 1                                               | GPA3                                               | -                    |

| 6       | TSEN             | Temperature sensing input                               | GPA4                                               | -                    |

| 7       | VREF             | Differential voltage sensing, negative input.           |                                                    | -                    |

| 8       | VSEN             | Differential voltage sensing, positive input            |                                                    | -                    |

| 9       | ISEN2            | Differential current sensing of phase 2, positive input |                                                    | -                    |

| 10      | IREF2            | Differential current sensing of phase 2, negative input |                                                    | -                    |

| 11      | ISEN1            | Differential current sensing of phase 1, positive input |                                                    | -                    |

| 12      | IREF1            | Differential current sensing of phase 1, negative input |                                                    | -                    |

| 13      | PWM1             | PWM1 output                                             | SYNC/ Fast_GPI1                                    | Yes                  |

| 14      | PWM2             | PWM2 output                                             | SYNC/ Fast_GPI2                                    | Yes                  |

| 15      | PWM3             | PWM3 output                                             | SYNC/ Fast_GPI1 / FAN1_TACH                        | Yes                  |

| 16      | PWM4             | PWM4 output                                             | SYNC/ Fast_GPI2 / FAN1_PWM                         | Yes                  |

| 17      | PWM5_MOSI        | PWM5 output                                             | SYNC/ UARTRX/ Fast_GPI1/<br>SPI_MOSI               | Yes                  |

| 18      | PWM6_SCK         | PWM6 output                                             | SYNC/ UARTTX/ Fast_GPI2/<br>SPI_SCK                | Yes                  |

| 19      | SDA              | I <sup>2</sup> C serial data line                       |                                                    |                      |

| 20      | SCL              | I <sup>2</sup> C serial clock line                      |                                                    |                      |

| 21      | SMBALERT#_CSS    | PMBus alert                                             | SYNC / Fault / CSS                                 | Yes                  |

| 22      | MP_SYNC          | Synchronize pin                                         | FAN1_PWM/ Fast GPI1/ Fault                         | Yes                  |

| 23      | MP_EN_MISO       | Enable_Sleep control                                    | SYNC/ SPI MISO                                     | Yes                  |

| 24      | MP_PWRGD         | Power good output                                       | SYNC                                               | Yes                  |

|         | EP (exposed pad) | Ground pin                                              |                                                    |                      |

Note:

- 1. EP is the metal pad under the chip

- 2. SDA, SCL, SMBALERT are Open Drain I/O pins

- 3. All digital GPIO pins are 3.3V level CMOS, the outputs are programmable to be CMOS or Open Drain

- 4. GPA: general purpose analog input pin

# 4 Functional description

#### 4.1 Introduction

The XDPP114x is a flexible, feature-rich digital controller, optimized for isolated and non-isolated dc-to-dc converters. The XDPP114x is designed to enable flexibility and provide excellent digital control for all the major fixed frequency topologies: pulse width modulation (PWM) half-bridge (HB), PWM full-bridge (FB), PWM phase-shift full-bridge (PSFB), active clamp forward (ACF), non-isolated Buck, Boost and Buck-boost. It also works for resonant LLC topologies including half-bridge (HB) LLC, full-bridge (FB) LLC, phase-shift full-bridge (PSFB) LLC. The XDPP1148 supports interleaved operation of Buck, Boost and Buck-boost.

The features that require fast response are implemented by state machine in hardware and can be configured over the I<sup>2</sup>C port. These features include:

- Digital PID loop filter and compensation

- Pre-bias startup

- Feed-forward compensation

- Non-linear PID fast transient

- Active current sharing

- Current balancing between two phases

- Flux balancing of full-bridge converter

- Burst operation in light load

- Phase shedding

The fault protections are implemented in hardware for the shortest delay time. The fault thresholds, thresholds hysteresis and fault count are configurable. The fault response is managed by firmware for flexibility. The industry standard PMBus interface also provides access to the monitoring and system control functions.

The integrated ARM<sup>®</sup> Cortex<sup>®</sup> -M0 microcontroller and built-in non-volatile memory provide extensive programming and customization of functions such as, the frequency dithering, GPIO signal timing, soft start timing and sequencing, dynamic dead-time based on operation, blackbox data recording.

### 4.1.1 ARM<sup>®</sup> Cortex<sup>™</sup> – M0 core

The XDPP114x chip embeds the smallest ARM processor – the ARM<sup>®</sup> Cortex<sup>®</sup>-M0 processor. It is a high performance 32-bit processor with low gate count, minimal power requirements, and reduced code footprint. It is an optimized interrupt controller, allows to be used in hard real-time applications. The ARM<sup>®</sup> Cortex<sup>®</sup> -M0 processor clock frequency f<sub>CLK</sub> is 100 MHz.

#### 4.1.2 Memories

The device has 80 kB Boot ROM that contains the initial firmware startup routines for PMBUS communication. This boot ROM is executed after power-up-reset checks. The XDPP114x also supports customization of the boot program by allowing an alternative boot routine to be executed from the one-time programmable (OTP) nonvolatile memory (NVM). Control registers can be reprogrammed in the field via the serial communication (I<sup>2</sup>C) bus and stored into the OTP NVM. For run time data storage and scratchpad memory, a 32 kB RAM is available.

## 4.1.3 Communication ports

The device provides I<sup>2</sup>C, SPI, and UART communication ports.

### 4.1.3.1 I<sup>2</sup>C/PMBus

All operating parameters in the device are configurable via the I<sup>2</sup>C serial interface (SDA, SCL). The SDA, SCL support two logic levels, 3.3 V and 1.8 V. By default, the controller uses 3.3 V logic. The device supports all three speeds I<sup>2</sup>C: standard (100 kHz), fast (400 kHz) and fast mode plus (1 MHz) operating frequency.

The device is compliant to PMBus<sup>™</sup> Power System Management Protocol Specification, revision 1.4.1. The I<sup>2</sup>C/PMBus interface allows to configure the device as well as monitoring fault status, voltage, current, power, and temperature telemetry.

### 4.1.3.2 SPI

The SPI is high speed communication port that allows a serial bit stream of programmed length (1 to 16 bits) to be shifted into and out of the device at a programmed bit-transfer rate up to 5 MHz. The SPI port supports two logic levels, 3.3 V and 1.8 V. For 3.3 V output, the SPI pin can be configured as CMOS (push-pull) output or opendrain. For 1.8 V logic, it must be configured to open-drain output and use external pull-up.

The device supports programmable slave or master mode. The SPI is normally used for communication between the XDPP114x and external peripherals. Typical applications include an interface to external I/O or peripheral such as shift registers, SPI EPROMs and analog-to-digital converters. The SPI typically is configured as a master for communicating to external EEPROM. It should be configured to slave mode when receiving control from another microcontroller in the system.

### 4.1.3.3 UART

A full duplex Universal Asynchronous Receiver/Transmitter (UART) interface is included in the device. The baud rate, word size, and buffer depth are configurable through registers. A loop back feature can also be setup for firmware verification.

The UARTTX and UARTRX pin sets can be configured using assigned GPIO pins. See **Table 7** for the list of GPIO pins and the pre-defined functions of each of them.

# 4.1.3.4 Address offset

The base address of I<sup>2</sup>C and PMBus is configured by firmware registers **addr\_pin\_i2c\_address\_offset** and **addr\_pin\_pmbus\_address\_offset**. By default, the base address of I<sup>2</sup>C is 0x10, the base address of PMBus is 0x40. Address offset can be added to the base address to differentiate multiple devices that have the same configuration (base address) in system. The XDPP114x uses XADDR1 pin for I<sup>2</sup>C/PMBus address offset by connecting a resistor from the XADDR1 to ground. The offset decoding is enabled by default with bit [7] of the **addr\_pin\_i2c\_address\_offset** set to 0 and bit [7] of the **addr\_pin\_pmbus\_address\_offset** set to 0.

The device supports 16-valent or 8-valent address table as shown in **Table 5** and **Table 6**. The bit [1] of firmware register **addr\_pin\_xv** configs the xValent selection between 16-valent and 8-valent. Set to 0 selects 16-valent, set to 1 selects 8-valent. The default pinset table size is 16-valent. To properly set the device addresses, resistors with 1% tolerance must be connected. The programming resistors are designed to allow using E12 resistors for system cost saving.

The device measures XADDR1 resistor offset during initialization state and does not support on the fly modification. The configuration must be stored in OTP memory and recycling VDD is required to have the modifications taking effect.

| Resis | tor-to-GND (1%) | Address offset |  |

|-------|-----------------|----------------|--|

|       | 680 Ω           | 0x00           |  |

|       | 1 kΩ            | 0x01           |  |

|       | 1.5 kΩ          | 0x02           |  |

|       | 2.2 kΩ          | 0x03           |  |

|       | 3.3 kΩ          | 0x04           |  |

|       | 4.7 kΩ          | 0x05           |  |

|       | 6.8 kΩ          | 0x06           |  |

| XADDR | 10 kΩ           | 0x07           |  |

| XAD   | 15 kΩ           | 0x08           |  |

|       | 22 kΩ           | 0x09           |  |

|       | 33 kΩ           | 0x0A           |  |

|       | 47 kΩ           | 0x0B           |  |

|       | 68 kΩ           | 0x0C           |  |

|       | 100 kΩ          | 0x0D           |  |

|       | 150 kΩ          | 0x0E           |  |

|       | 220 kΩ          | 0x0F           |  |

| Table 5 | I <sup>2</sup> C/PMBus address offset of 16-segment decode |

|---------|------------------------------------------------------------|

|---------|------------------------------------------------------------|

| Table 6 | I <sup>2</sup> C/PMBus address offset of 8-segment decode |

|---------|-----------------------------------------------------------|

|---------|-----------------------------------------------------------|

| Resistor-to-GND (1%) |        | Address offset |  |

|----------------------|--------|----------------|--|

| Nesis                | 10 kΩ  | 0x00           |  |

| XADDR                | 22 kΩ  | 0x01           |  |

|                      | 33 kΩ  | 0x02           |  |

|                      | 47 kΩ  | 0x03           |  |

|                      | 68 kΩ  | 0x04           |  |

|                      | 100 kΩ | 0x05           |  |

|                      | 150 kΩ | 0x06           |  |

|                      | 220 kΩ | 0x07           |  |

### 4.1.4 GPIO

The device provides up to 11 general purpose inputs/outputs (GPIOs). All the GPIO pins are shared with alternative functions. The GPIO configuration is programmed by the function register of each GPIO pin named xxxx\_func. The GPIO polarity is configured by firmware config register **gpio\_config\_polarity**. When configured as an output pin, the MP\_IMON, MP\_EN, PWM5\_MOSI and PWM6\_SCK pins can choose output buffer as CMOS output (push-pull) or open-drain output by setting xxxx\_ppen register. All other GPIO pins can be configured as emulated open-drain using firmware register **gpio\_config\_emu\_open\_drain**.

The GPIO config only set on initialization. Modifications to gpio\_config registers would have to be stored in OTP and will take effect after power cycling the  $V_{DD}$  or resetting FW.

| Name       | Function 0         | <b>Function 1</b> | Function 2   | Function 3 | Function 4   | Function 5  | Function 6   | Function 7  |

|------------|--------------------|-------------------|--------------|------------|--------------|-------------|--------------|-------------|

| MP_IMON    | A: IMON            | IO: GPIO[3]       | IO: GPIO[11] | IO: SYNC   | I: FAN1_TACH | O: GENERIC_ | I: FAST_GPI2 | IO: GPIO[0] |

|            |                    |                   |              |            |              | FAULT       |              | (EN)        |

| PWM1       | O: PWM1            | IO: GPIO[5]       | IO: GPIO[13] | IO: SYNC   | na           | na          | I: FAST_GPI1 | na          |

| PWM2       | O: PWM2            | IO: GPIO[7]       | IO: GPIO[15] | IO: SYNC   | na           | na          | I: FAST_GPI2 | na          |

| PWM3       | O: PWM3            | IO: GPIO[6]       | IO: GPIO[14] | IO: SYNC   | I: FAN1_TACH | na          | I: FAST_GPI1 | na          |

| PWM4       | O: PWM4            | IO: GPIO[2]       | IO: GPIO[10] | IO: SYNC   | O: FAN1_PWM  | na          | I: FAST_GPI2 | na          |

| PWM5_MOSI  | O: PWM5            | IO: GPIO[3]       | IO: GPIO[11] | IO: SYNC   | I: UARTRX    | I: S_MOSI   | I: FAST_GPI1 | O: M_MOSI   |

| PWM6_SCK   | O: PWM6            | IO: GPIO[4]       | IO: GPIO[12] | IO: SYNC   | O: UARTTX    | I: S_SCK    | I: FAST_GPI2 | O: M_SCK    |

| SMBALERT#_ | IO: SMBALERT_N     | IO: GPIO[6]       | IO: GPIO[14] | IO: SYNC   | O: GENERIC_  | I: S_CSS    | na           | O: M_CSS    |

| CSS        |                    |                   |              |            | FAULT        |             |              |             |

| MP_SYNC    | na                 | IO: GPIO[7]       | IO: GPIO[15] | IO: SYNC   | O: FAN1_PWM  | O: GENERIC_ | I: FAST_GPI1 | na          |

|            |                    |                   |              |            |              | FAULT       |              |             |

| MP_EN_MISO | IO: GPIO[0](EN)    | IO: GPIO[10]      | IO: GPIO[8]  | IO: SYNC   | na           | O: S_MISO   | na           | I: M_MISO   |

| MP_PWRGD   | IO: GPIO[1](PWRGD) | IO: GPIO[12]      | IO: GPIO[9]  | IO: SYNC   | na           | na          | na           | na          |

#### Table 7GPIO and I<sup>2</sup>C/SPI multi-purpose pin

Note:

- 1. Analog functions prefixed with "A:"

- 2. Digital inputs prefixed with "I:", outputs prefixed with "O:", inouts prefixed with "IO:"

- 3. Input priority by lowest pin # (e.g., if MP\_IMON and PWM6\_SCK both programmed to SYNC, the input is taken from MP\_IMON due to lower pin #)

#### 4.1.5 Register map

The device is configured by application specific parameter settings loaded into control registers. The direct I<sup>2</sup>C register access is disabled by default with the bit [4] of **vid\_resolution** set to 1. The access to control register map can be achieved via PMBus. The MFR\_REG\_WRITE, MFR\_REG\_READ and the MFR\_AHB\_ADDRESS PMBus commands are used write\read register parameters. The access to register map is supported by the XDP designer GUI without extra steps.

The control registers are not pre-programmed at the factory. Control registers should be programmed in each specific application and stored into the on-chip nonvolatile memory (NVM), which is then downloaded to the control registers during initialization of the controller as it powers up. The controllers support multiple reprogramming cycles which is easily accomplished with the GUI or System Programmer software.

The controllers also support storing multiple configurations in NVM. It can store up to 16 configurations, and these configurations may be reprogrammed if needed.

### 4.2 Analog blocks and subsystems

### 4.2.1 Power supply

Operating from a single +3.3 V (VDD) supply to the controller, an on-chip low drop-out (LDO) regulator generates an internal +1.2 V voltage at VD12 pin. Both VDD and VD12 pin should have 1  $\mu$ F + 0.1  $\mu$ F ceramic bypass capacitors for noise filtering. Place the bypass capacitors as close as possible to VDD and VD12 pins. Do not apply voltage to or ground VD12 pin. VD12 pin can be used as 1.2 V reference of the current sense input, but not intend to drive a load.

The device can be put into sleep mode to reduce quiescent current and system standby power. The sleep mode current consumption is  $I_{DDsleep}$ . It is capable wakeup from sleep mode after  $t_{wakeup}$ . If deep sleep mode is not desired, it can be disabled and allows faster response to the EN input. The EN logic can be configured to be active-high or active-low.

## 4.2.2 Oscillator and PLL

An internal PWM oscillator running at f<sub>osc</sub> is incorporated in the device, and the frequency programming resolution is 5 ns. With a 6-bit interpolator, the XDP device offers high PWM resolution as small as 78.125 ps. Using a 12-bit time-based period and frequency control, the maximum pulse width that the device supports is 20.48 µs (4096 x 5ns); this sets the minimum switching frequency to approximately 50 kHz. The maximum switching frequency is 2 MHz. For LLC topologies, the frequency adjusting resolution is 2.5 ns.

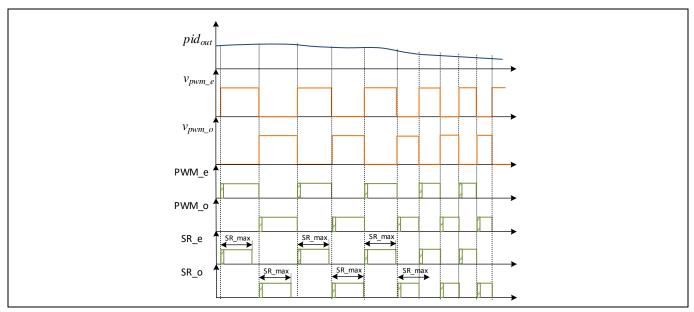

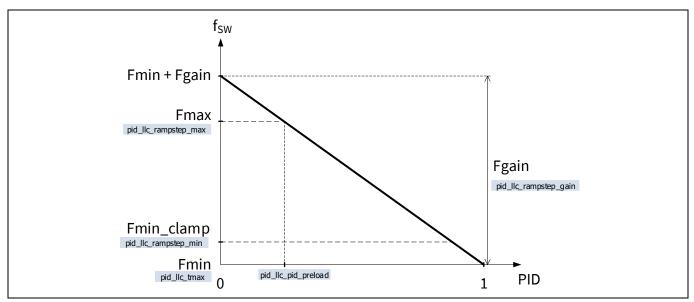

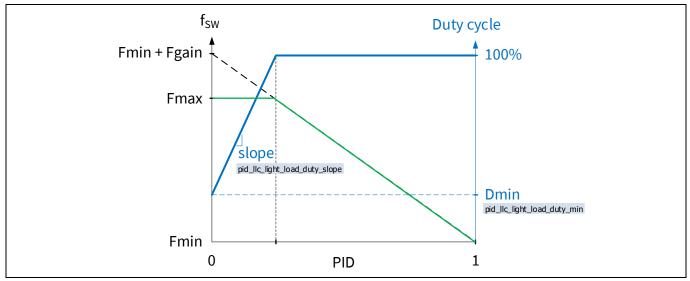

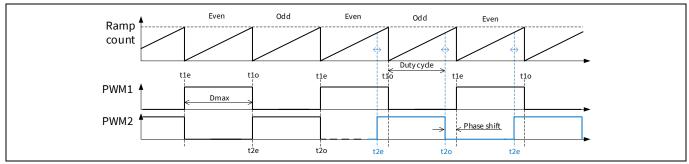

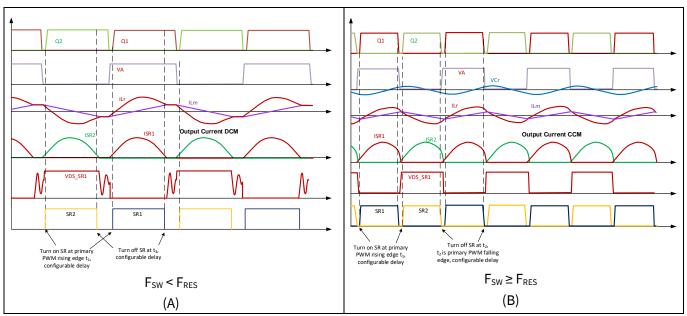

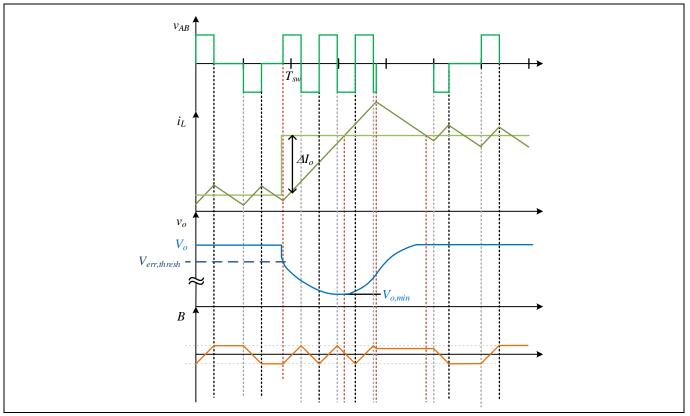

A typical LLC frequency modulation waveform is shown in **Figure 5**. The top axis shows compensated error signal (that is, PID output). The second axis shows the resulting pwm waveform of even cycle, followed by the pwm signal of odd cycle. The lower the PID output, the higher the switching frequency. The signals on the next two axes are PWM outputs which have hatched lines indicating where dead-time is applied to the signals. The bottom two axes are the secondary SR PWM waveforms which follows primary PWM with maximum ON time limitation.

Figure 5 PWM generation of LLC topology

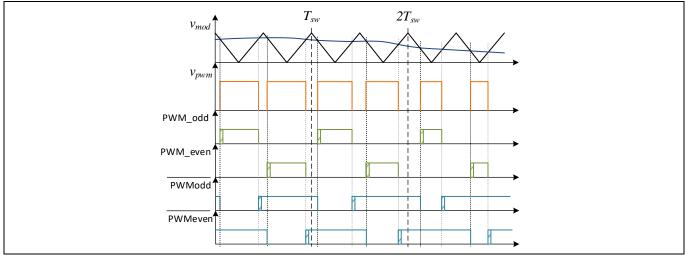

A typical PWM generation waveform is shown in **Figure 6**. The top axis shows analog behavioral waveforms of a dual-edge modulator (Vmod) and compensated error signal (that is, PID output). The second axis shows the resulting PWM waveform. The signals on the bottom four axes have hatched lines indicating where dead-time is applied to the signals.

#### Functional description

Figure 6 PWM Generation of PWM topology

Dead-time refers to the amount of time between the turning-off of one switch to the turning-on of another switch where both are off to prevent unintentional short circuit conditions. The standard way of implementing dead-time is to use leading edge-blanking. Each signal of the PWM generator is capable of blanking the rising edge by a programmable amount. The device supports two sets of dead-time resolutions and ranges, configured by register **deadtime\_lsb\_sel**, for 0-318.75 ns in 1.25 ns increments or 0-637.5 ns in 2.5 ns increments. The device also supports to adjust the falling edge of each PWM if additional blanking time is required. The value of dead-time is changeable during normal operation to allow power supply efficiency optimization.

PWM outputs are 3.3 V compatible signals which are set to high impedance during reset, configuration, and initialization. The PWM outputs that are mapped to a Loop to drive MOSFETs is pulled to the state defined in the configuration after firmware completed the initialization. The PWM OFF state level can be set low or high by **pwm\_state\_shutdown** register, and enabled by **en\_pwm\_state\_shutdown**. By default, the PWM OFF state is disabled and all the PWMs that are mapped to a Loop stays low during shutdown.

The multi-purpose MP\_SYNC pin can be configured as an input to allow synchronization to an external clock signal, or as an output to provide a clock that other converters synchronize to. For the best flexibility, all GPIO pins can be configured as SYNC pin.

When SYNC pin is configured as an input, the PLL receives a periodic signal. The input signal is limited to  $\pm 12.5\%$  of the programmed switching period to lock the sync clock. Once the frequency is locked, the system can remain in sync for a maximum of  $\pm 25\%$  of the programmed switching period.

The SYNC output signal is a square waveform with the rising edge aligned with PWM signal per topology and type of modulation. The sync function would provide a signal indicating successfully synchronization, as well as a fault if it cannot synchronize.

# 4.2.2.1 The 3<sup>rd</sup> ramp

Besides the two regular oscillator ramps which used to generate PWM outputs for up to two phases, the device also provides a third ramp. The frequency of the third ramp can be configured independently to the first two regular ramps (ramp0 and ramp1). It can also be synchronized with the ramp0 or to an external frequency if desired. The third ramp is not associate with any close loop control thus only supports open loop operation. The rising edge and the falling edge of the third ramp can be programmed independently by FW patch.

With the third ramp, the device could drive interleaved Buck or interleaved 3-level buck converter with a cascade open loop stage.

| Features                                                        | XDPP1148-100B | XDPP1140-100B | XDPP1100-Q024 | XDPP1100-Q040 |  |

|-----------------------------------------------------------------|---------------|---------------|---------------|---------------|--|

| Number of loops                                                 | 1             | 1             | 1             | 2             |  |

| Number of ramps                                                 | 2+1           | 2+1           | 2             | 2             |  |

| Number of VS ADC                                                | 1             | 2             | 2             | 2             |  |

| Number of IS ADC                                                | 2             | 1             | 1             | 2             |  |

| Topology                                                        |               |               |               |               |  |

| HB/CT; HB/FB                                                    | $\checkmark$  | $\checkmark$  | ✓             | ✓             |  |

| FB/CT; FB/FB                                                    |               | ✓             | $\checkmark$  | ✓             |  |

| (VMC with Flus balance)                                         |               | •             | •             | •             |  |

| FB/CT; FB/FB (PCMC)                                             | $\checkmark$  |               |               | $\checkmark$  |  |

| ACF                                                             | ✓             | $\checkmark$  | $\checkmark$  | $\checkmark$  |  |

| PSM-FB/CT; PSM-FB/FB                                            | ✓             | ✓             | ✓             | ✓             |  |

| LLC-HB; LLC-FB; LLC-PSFB;<br>secondary CT or FB                 | ✓             | ~             |               |               |  |

| Buck                                                            | ✓             | $\checkmark$  | $\checkmark$  | $\checkmark$  |  |

| Buck-boost                                                      | ✓             | $\checkmark$  | $\checkmark$  | $\checkmark$  |  |

| Boost                                                           | ✓             | $\checkmark$  | $\checkmark$  | $\checkmark$  |  |

| Interleaved Buck                                                | ✓             |               |               | $\checkmark$  |  |

| Interleaved Buck-boost                                          | ✓             |               |               | $\checkmark$  |  |

| Interleaved Boost                                               | ✓             |               |               | ✓             |  |

| Interleaved HB/CT; HB/FB; FB/CT;<br>FB/FB; PSM-FB/CT; PSM-FB/FB |               |               |               | ~             |  |

| Interleaved ACF                                                 |               |               |               | $\checkmark$  |  |

| Dual loop<br>(single phase of each loop)                        |               |               |               | ✓             |  |

| Interleaved Buck + open loop<br>converter                       | ✓             |               |               |               |  |

| Interleaved 3-level Buck+ open<br>loop converter                | ✓             |               |               |               |  |

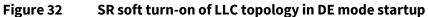

# 4.2.3 Voltage sense AFE1

The XDPP1140 offers two dedicated high speed voltage analog/digital converters (ADC) as Analog Front End (AFE1), while the XDPP1148 offers one dedicated high speed VADC. The voltage sense AFE1 can be used as voltage sense processor (VSP) or rectified voltage sense processor (VRSP).

The major functions of the VSP and its associated blocks are:

- Voltage ADC full rate interface to the digital domain

- Voltage ADC gain and offset trim (digital trim)

- Voltage scaling (external resistor divider)

- Input or output voltage computation (configurable input or output sense)

- Over/Under Voltage Protection comparators and fault

- Fast transient (FTR) mode and FTR exit comparators

- Burst mode and burst mode exit comparators

The VRSP and its associated blocks have the following functions in addition to the above:

- 200 MHz edge comparator with digital de-glitcher

- Measure V<sub>RECT</sub> voltage of the even and odd half cycles of bridge topologies

- Measure V<sub>RECT</sub> voltage on the even cycle for non-bridge topologies

- Average the measured even and odd V<sub>RECT</sub> voltage

- Flux balancing circuit

- Input voltage processing

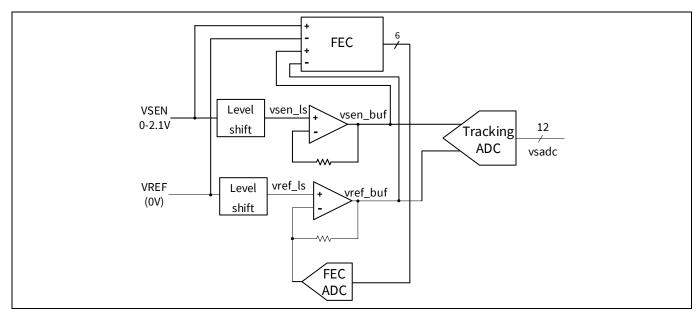

The simplified VSADC block diagram is shown Figure 7.

#### Figure 7 Voltage sense ADC block diagram

The level shifters allow wide input voltage range, 0.0 to 2.1 V, as well as provide a high input impedance. The unity gain buffers provide additional drive strength to the tracking ADC input stage. The front end offset compensator (FEC) is to reduce the effects of temperature, stress and lifetime offset-drift in the AFE.

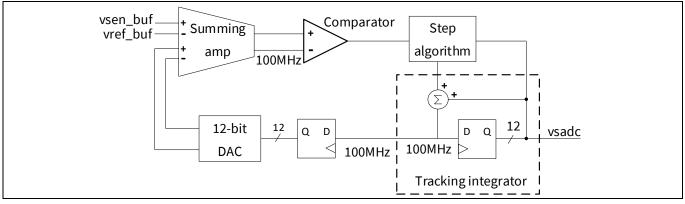

Simplified block diagram of the tracking ADC is shown in **Figure 8**. The summing amplifier amplifies the difference between the buffered differential sensed voltage and the DAC output voltage.

The output of the summing amplifier drives the comparator whose output determines the size and direction of the next step for the tracking integrator. The tracking integrator output represents the analog to digital converted sensed voltage. It is also used to drive the DAC whose output is summed in the summing amplifier.

Functional description

Tracking ADC resolution is 12 bits with an input referred LSB weight of 1.25 mV. Note that the AFE input range is restricted to maximum of 2.1 V, meaning only the lower 11 bits of the ADC output are actually used. For output voltage sensing, 3-bit modulation is added to the reference voltage to achieve 156.25  $\mu$ V resolution.

The voltage sense input has a nominal input impedance of  $1 \text{ M}\Omega$ . The ADC is clocked at 100 MHz and a voltage sense front-end amplifier process the voltage at 50 MHz. There is no need for an anti-alias filtering, but it may be advantageous to add a higher bandwidth external RC filter network to increase the attenuation of high frequency noise that may couple onto the voltage sense lines. This additional filter provides minimal phase margin impact on the feedback loop. If such an additional filter is used, it is recommended that values of  $R_{EXT} = 10 \Omega$  and  $C_{EXT} = 220 \text{ pF}$  be used.

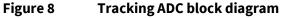

The VRSP is responsible for controlling the VSEN1 or VSEN2 ADC when they are used to measure the rectified voltage waveform ( $V_{RECT}$ ).  $V_{RECT}$  sensing is often used to sense the input voltage indirectly from the secondary side of transformer. Figure 9 presents waveforms to illustrate how sampling of the  $V_{RECT}$  waveform. Noise has been added to the ideal  $V_{RECT}$  waveform to highlight the importance of sampling window timing. The AFE1 has an edge detector working at 200 MHz clock. It senses the rising and falling edges of  $V_{RECT}$  waveform. T<sub>detect</sub> waveform is the output of edge detector logic. The rising-edge of the rectified voltage waveform is detected and some programmable blanking window is added to it. The blanking time should be configured longer than the voltage spike and ringing duration. The blanking time should also be set longer than 250 ns for the tracking ADC to settle. After the blanking window, sampling of the rectified voltage can occur (shown as the T<sub>sample</sub> waveform). The comparator for the VSEN ADC is prepositioned to the value of the last cycle to minimize the time required for the ADC to properly track the voltage. The sampling window ends when the associated PWM signal goes low.

The input voltage is calculated based on  $V_{RECT}$  sensed voltage,  $V_{RECT}$  resistor divider scale and the transformer turns ratio. Faults and warnings including input overvoltage and undervoltage would be detected by the VRSP when it is being used for input voltage sensing. These are set by PMBus commands, and the response is handled by the CPU.

#### Functional description

Figure 9 VRSP sampling window

The timing of the rising and falling edges of the rectified voltage waveform, along with the magnitude, is used for transformer protection, that is, in full-bridge voltage mode converter, the  $V_{RECT}$  timing and amplitude is used for volt-second flux balancing. To avoid waveform distortion or timing delay, it is not recommended to add any filter to the input of VSEN when it is used  $V_{RECT}$  sensing mode.

# 4.2.4 Current sense AFE2

The dedicated differential current sense ADC (AFE2) is designed to sense current via low ohmic sense resistor or PCB copper trace, as well as sense primary current through current sense transformer. The ISADC (ISEN1, ISEN2) is 9-bit ADC. It operates at 100 MHz and could provide high speed short circuit protection (SCP). The resolution of current sense ADC is 1 mV/LSB. The reference level (common mode voltage at IREF pin) is 1.2 V.

The device supports both primary and secondary current sense. When sensing primary current through current transformer, symmetric positive and negative input voltage range (+/- 256 mV) is enabled. This feature does not require rectifying the signal, thus simplify external circuit. When sensing secondary current, a configurable digital offset could be used to adjust the voltage level at 0 A, thus allowing to increase the effective positive input voltage range. The maximum digital offset voltage is 252 mV.

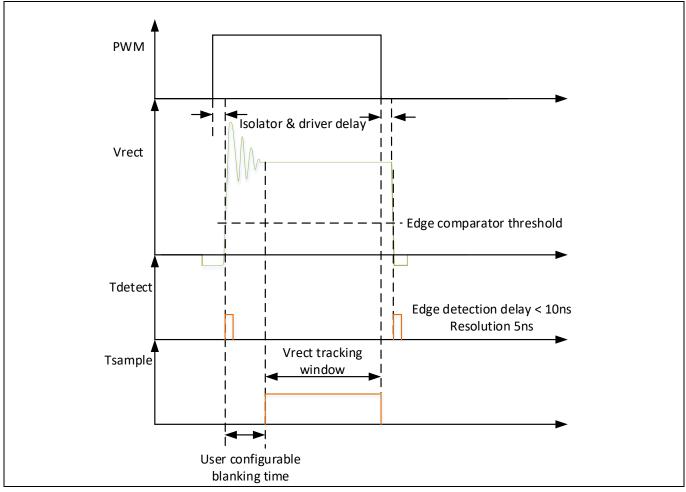

Simplified block diagram of the current sense ADC is shown in **Figure 10**.

#### **Functional description**

Figure 10 Simplified block diagram of the current sense ADC

For PWM topologies, the current estimator provides a digital reconstruction of the secondary side inductor current or the primary side current, depending on the current sense input pin configuration. The shape of this current is obtained through slope estimation function. Based on the state of the PWM pulse, the controller continuously predicts each individual phase DC and ripple current. The result of the prediction is combined with the actual measured phase current to be processed by the controller. Hence, the instantaneous noise in the measurement can be filtered out without losing the valuable ripple current information.

For LLC topology, the current estimator circuit is bypassed. The output of the current sense block purely relies on ADC sensing. The ADC is capable tracking sinusoid current waveform with slew rate up to 1.6 mV/ns. The current sense processor (ISP) mode is configured by **isp0\_mode** and **isp1\_mode** registers.

If PCB copper traced is used for current sensing, temperature compensation should be considered to compensate the temperature shift of the copper trace. The controller continuously monitors temperature and uses this information to digitally compensate for resistance changes over temperature. The built-in temperature coefficient is 0.39% Ampere/ °C for copper material. Customized temperature coefficient can be achieved using FW patch.

The controller provides several mechanisms for improving the current sense accuracy. To reduce the effect of board noise on the current sense, leading edge blanking and trailing edge blanking time are implemented at PWM transition. The blanking time can be configured from 0 to 280 ns. In addition, the controller makes

multiple current measurements and the readings are averaged over every switching cycle. To improve the current sense accuracy, the controller also allows to compensate the parasitic inductance of current sense resistor.

The polarity of the current sense can be configured through the ISP digital processor. Write 1 to **isp0\_invert\_input** or **isp1\_invert\_input** inverts the polarity. When the polarity is inverted, the current estimator is disabled and current sense relies on the ADC only. The default config is non-inverted.

The major functions of the current sense processor (ISP) and its associated blocks are:

- Current ADC full rate interface to the digital domain

- Current ADC gain and offset trim (digital trim)

- Current scaling

- Output current computation

- Output current shunt temperature compensation

- Output Over/Under Current Protection comparators and fault

- Input current computation

- Input Over Current Protection comparators and fault

- Cycle-by-cycle peak current limit

### 4.2.5 General purpose AFE3

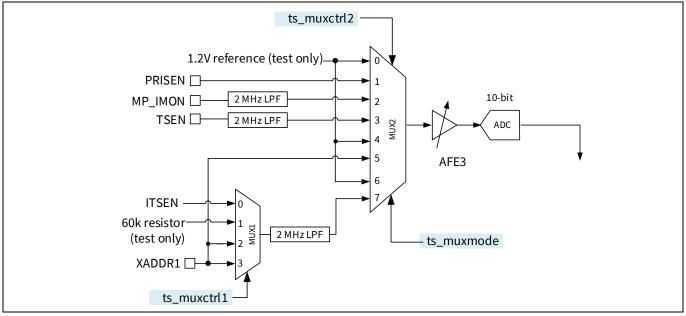

The general-purpose ADC AFE3, also referred to as telemetry ADC (TS ADC), is a 10-bit, high speed analog to digital converter. Voltage resolution of the general-purpose ADC is 2.344 mV, with a sample frequency 0.926 MHz. The general-purpose ADC block consists of 8 channels with 4 channels externally accessible through pins PRISEN, MP\_IMON, TSEN and XADDR1 as shown in **Figure 11**. It can be configured to digitize voltage, impedance, and temperature.

Figure 11 Telemetry ADC block

The conversion sequence of channels can be customized or can be set to auto sequencing per mux control registers **ts\_muxctrl1**, **ts\_muxctrl2**, **ts\_muxmode**.

#### 4.2.5.1 IMON and active current sharing

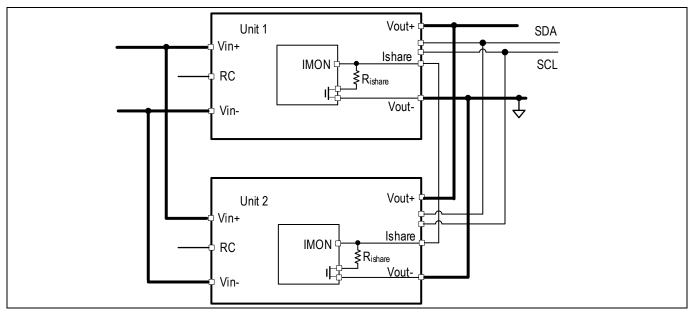

IMON pin has an analog DAC current source representing the output current. IMON could be used for output current monitor, and for active current sharing in multi parallel modules application. An internal current proportional to the output current is sourced from IMON pin. IMON current DAC (IDAC) is 6-bit DAC with output current range in 0 to 640  $\mu$ A. There are 4-bit accumulated dithering driving an extra LSB input to the DAC for extra resolution (total 6+4 bit). The gain of the current source is configurable which allows to scale the current source per application. At no load, this source current is 160  $\mu$ A. IMON source current lower than 160  $\mu$ A indicates negative current in this module.

Connecting a 2.2 k $\Omega$  precision resistor (R<sub>ishare</sub>) between IMON and a GPIO pin. The GPIO pin is used as a switch to disconnect the R<sub>ishare</sub> when the converter is not in regulation such as in off state or in fault shutdown. Use register **gpio\_config\_ishare\_imon\_disconnect\_select\_loop0** to assign a GPIO for this function. When the converter is in regulation and the current sharing is active, the GPIO pin connects the R<sub>ishare</sub> to ground, thus IMON pin presents a voltage proportional to output current. Connecting the IMON of multi converters to the I<sub>share</sub> bus, the voltage of I<sub>share</sub> bus represents the average current of the parallel modules.

Each power supply converter would compare its own output current with the average current and adjust output voltage accordingly to reduce the error. To prevent oscillation on small error current, a dead zone applies to the current sharing block. When the error current is less than the dead zone, current sharing is inactive. At full load, the IMON voltage is 1.408 V (640  $\mu$ A x 2.2 k $\Omega$ ); and at 0 A load, IMON voltage is 0.352 V (160  $\mu$ A x 2.2 k $\Omega$ ).

To smooth the IDAC dithering ripple, it is suggested to put at least 1 nF capacitor between IMON pin and ground. The device has an internal low pass filter to config the bandwidth for the current sharing.

The device provides both positive and negative clamps to voltage adjustment during active current sharing. This guard bands the output voltage in a safe range. If the output voltage reaches the clamping level and the current error is still larger than the dead zone, current share fault is reported.

Figure 12 Parallel module current sharing

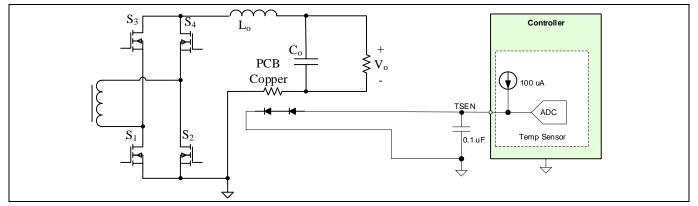

#### 4.2.5.2 Temperature sense

The device supports both, external and internal temperature sensing for protection and monitoring. External temperature sensing is performed with a temperature sensor connected between TSEN and ground. The device supports sensing temperature by diode forward voltage drop. It is recommend using two diodes in series to provide higher resolution. The temperature sensor should be placed close to and tightly coupled to the element of interest, for example the power stage components or the current sense resistor.

**Figure 13** shows the TSEN pin connects to two diodes in series to ground for temperature sense. It also can be configured to use NTC thermistor by replacing the series diodes with a 47 k $\Omega$  NTC in parallel with a 12 k $\Omega$  resistor. The NTC based temperature sense is backward compatible with the <u>XDPP1100-Q024</u> solutions. The temperature is sensed by injecting a 100  $\mu$ A current and measuring the voltage on TSEN. The temperature is used to effectively compensate for the temperature coefficient of the current sense element and to provide over temperature protection by generating warning and fault signals. If the temperature sensor is not required, the TSEN pin must be tied to GND.

When using two-diode voltage drop or  $V_{BE}$  for temperature sensing, the offset and gain can be configured based on the actual diode used. It also supports customized temperature lookup table if other temperature sense device is preferred, such as PTC thermistor temperature sense.

Figure 13 Temperature sensing

A noise decoupling cap is recommended and should be placed between the TSEN pin and GND next to the IC.

The internal temperature sensor is a PTAT (Proportional to Absolute Temperature) voltage generated within the controller die which reflects the junction temperature of the controller.

### 4.2.5.3 **PRISEN**

PRISEN is used to sense primary voltage for input voltage telemetry and feedforward compensation. In isolated converter, the  $V_{IN}$  voltage should be sensed at primary side and feed to the device through isolated amplifier or auxiliary transformer. The slope and offset of the PRISEN are configured by **vin\_pwl\_slope** and **vin\_trim** registers.

The XDPP1140 has the option to use either PRISEN or VSEN for input voltage sense, configured by register **tlm\_vin\_src\_sel**.

When using PRISEN for  $V_{IN}$  sense: The PRISEN is always enabled even when converter is in OFF mode. The general ADC has 0.926 MHz sample rate, and the ADC is shared with three other inputs (temperature sense TSEN, IMON, XADDR1), thus the feedforward response is slower than the VSEN based input voltage sensing.

When using VSEN for  $V_{IN}$  sense (only available for XDPP1140): uses high speed ADC VSEN1 or VSEN2 selected by register **vsen\_select**. The VSEN ADC has 50 MHz sample rate, provides very fast feedforward response and OV/UV protection. When using VSEN (1 or 2) for  $V_{IN}$  telemetry, it can be configured to sense DC input voltage by setting the **vsen\_vrect\_mode** register to "VIN mode", or set to " $V_{RECT}$  mode" when sensing at transformer secondary winding. When set to " $V_{RECT}$  mode", the  $V_{IN}$  telemetry is active only after the converter starts switching.

The PRISEN and VSEN voltage sensing could be combined for the best system performance. The XDPP1140 allows to configure the input voltage telemetry and input voltage feedforward independently. Using PRISEN for input voltage telemetry allows continuous input voltage monitoring and pre-startup protections, using V<sub>RECT</sub> sensing through VSEN for fast feedforward response and flux balancing functions.

# 4.2.6 Fast trigger input

The device has up to 2 fast trigger inputs – GPI1 and GPI2 - which can be used as external fault shutdown control to increase system reliability; or used for special timing control such as the SR timing of LLC.

Any PWM pin can be configured as the fast trigger input, see **Table 7**.

# 4.2.7 Fast fault output

The XDPP114x could config MP\_IMON, MP\_SMBALERT# or MP\_SYNC pin as fault output pin. The fault output will change polarity when a loop fault or a common fault is triggered. The response time from fault triggering to the fault pin reporting is less than  $t_{FSF}$ . The list of fault and fault mask bit assignment are described in chapter **4.4**. To disable the fault pin responding to a particular fault, set the assigned bit of the **fault\_gpio\_mask\_loop** or the **fault\_gpio\_mask\_com** to 1.

# 4.3 Control loop subsystems

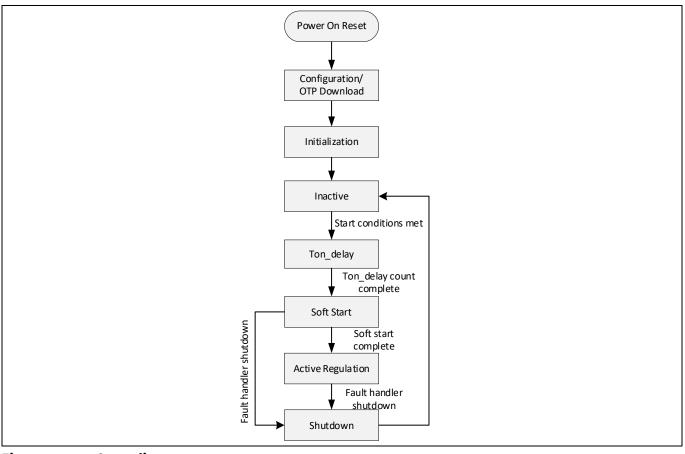

# 4.3.1 State diagram

The state diagram is shown in **Figure 14**.

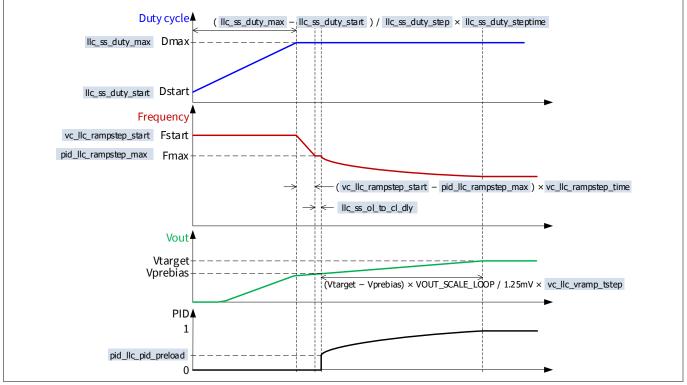

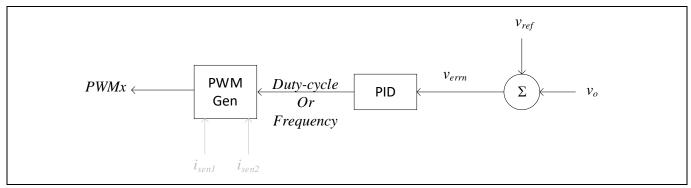

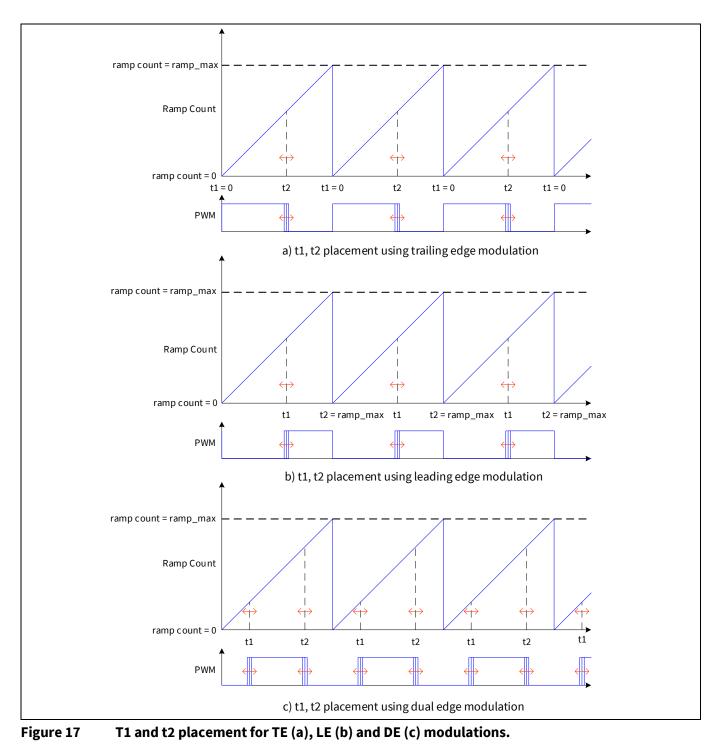

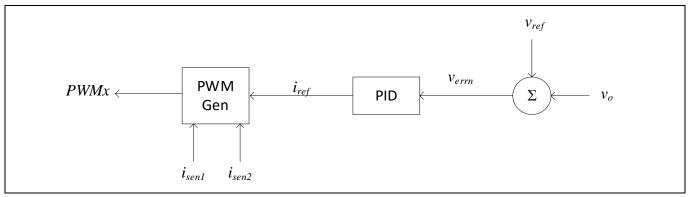

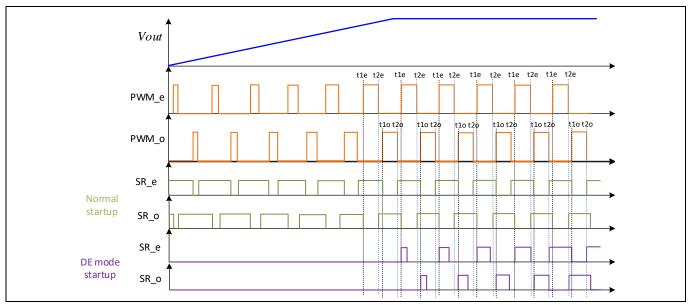

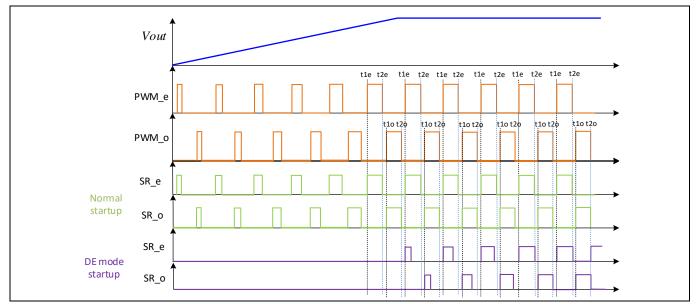

Controller operation is initialized by a power-on UVLO circuit. During controller configuration, the content of the OTP NVM is downloaded onto the control registers. During this period, the GPIO pins are held in high impedance (Hi-Z) state, allowing board pull-up or pull-down resistors to set the correct default levels for static input signals such as the I<sup>2</sup>C address (XADDR1).