### **Datasheet**

## **Product Highlights**

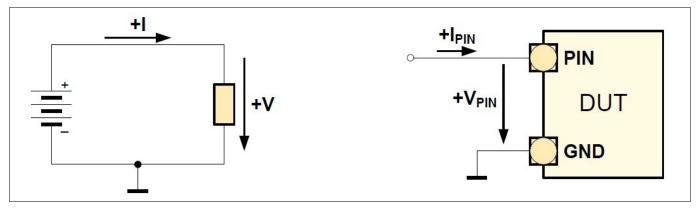

- Digital combo controller for PFC-boost and dc-dc hybrid-flyback in DSO-14 (150mil) package

- Novel ZVS hybrid-flyback (asymmetrical half-bridge) topology for ultra-high system efficiency

- Integrated gate drivers supporting GaN and Si switches

- 600V high voltage start-up cell for fast VCC charging

- Burst mode operation control for lowest no-load stand-by power

- Adaptive PFC bus voltage and PFC enable/disable control to maximize average and light load efficiency

- Configurable parameters for protection modes and system performance

- Pb-free lead plating, halogen-free (according to IEC61249-2-21), RoHS compliant

### **PFC** control

- Configurable PFC QRM operation for improved average efficiency

- Pulse skipping for improved light load efficiency

- Automatic PFC disable/enable-control depending on operating conditions

- Adaptive PFC bus voltage level following operating conditions

## **Hybrid-flyback control**

- Peak current mode control for robust and fast input and load control

- ZVS operation of high-side and low-side switch (with ZVS pulse insertion in DCM)

- Configurable multimode operation for improved average and light load efficiency

## **Description**

The XDPS2221 PWM controller is a highly integrated device combining a multimode ac-dc PFC controller and a multimode dc-dc hybrid-flyback controller. The integration of PFC and hybrid-flyback into a single package enables the reduction of external bill of material components and optimizes the system performance by harmonized operation of the two stages.

## **Ordering Information**

| Product Name | Marking  | Marking Ordering Code |       | Package   |

|--------------|----------|-----------------------|-------|-----------|

| XDPS2221     | XDPS2221 | SP005630569           | 3.1.4 | PG-DSO-14 |

## **Potential Applications**

Ultra high power density chargers / adapters

### **Product Validation**

Qualified for industrial applications according to the relevant tests of JEDEC47/20/22.

# Table of contents

**Table of contents**

|         | Table of contents                                                             | 2  |

|---------|-------------------------------------------------------------------------------|----|

| 1       | Pin Configuration and Functionality                                           | 5  |

| 2       | Representative Block Diagram                                                  | 7  |

| 3       | Introduction                                                                  | 8  |

| 4       | Functional description                                                        | 11 |

| 4.1     | Power-supply and high voltage start-up cell management                        | 11 |

| 4.1.1   | VCC capacitor charge-up and start-up sequence                                 | 11 |

| 4.1.2   | Bang-bang mode operation during brown-in phase                                | 13 |

| 4.1.3   | Bang-bang mode during protection mode operation                               | 13 |

| 4.1.4   | VCC supply during burst mode (BM) operation                                   | 14 |

| 4.2     | PFC control                                                                   | 14 |

| 4.2.1   | Combined current sense (CS) and zero crossing detection (ZCD) function        | 16 |

| 4.2.2   | Multimode operation and frequency law                                         | 16 |

| 4.2.2.1 | Quasi-resonant mode (QRM)                                                     | 17 |

| 4.2.2.2 | Low power mode                                                                | 17 |

| 4.2.3   | PFC bus voltage sensing and regulation                                        |    |

| 4.2.4   | PFC bus voltage target setting                                                |    |

| 4.2.5   | PFC soft-start                                                                | 18 |

| 4.2.6   | PFC gate driver                                                               | 18 |

| 4.2.7   | PFC disable                                                                   | 18 |

| 4.3     | Hybrid-flyback control                                                        | 18 |

| 4.3.1   | PWM control schemes                                                           |    |

| 4.3.1.1 | CRM control scheme                                                            | 19 |

| 4.3.1.2 | ZV-RVS control scheme                                                         | 20 |

| 4.3.1.3 | Valley skipping control                                                       | 21 |

| 4.3.1.4 | DCM control scheme                                                            | 22 |

| 4.3.1.5 | Mode transition between CRM and ZV-RVS                                        | 22 |

| 4.3.2   | Output control                                                                | 22 |

| 4.3.2.1 | Output current control law                                                    | 23 |

| 4.3.2.2 | Keeping ZVS operation for wide Vbus voltage range                             | 24 |

| 4.3.2.3 | Keeping ZVS operation for wide output voltage range                           | 24 |

| 4.3.2.4 | ZVS operation and body-diode cross-conduction prevention during CRM operation | 24 |

| 4.3.2.5 | Propagation delay compensation (PDC)                                          | 24 |

| 4.3.3   | Vout start-up control                                                         | 24 |

| 4.3.4   | Frequency jitter                                                              | 24 |

| 4.3.5   | Half-bridge gate driver                                                       |    |

| 4.4     | Combo-control functions                                                       |    |

| 4.4.1   | Burst mode control                                                            | 26 |

|         |                                                                               |    |

### **Table of contents**

| 4.4.1.1    | Burst mode entry                           | . 26 |

|------------|--------------------------------------------|------|

| 4.4.1.2    | Burst mode operation                       | . 26 |

| 4.4.1.3    | Burst mode bootstrap precharge             | . 26 |

| 4.4.1.4    | Burst mode exit                            | . 27 |

| 4.4.2      | PFC enable/disable control                 | 27   |

| 4.4.3      | Variable bus voltage target level          | . 27 |

| 4.5        | Protections                                | 28   |

| 4.5.1      | Protection modes                           | . 28 |

| 4.5.1.1    | Deactivate IC after undervoltage lockout   | . 29 |

| 4.5.1.2    | Auto-restart mode                          | . 29 |

| 4.5.1.3    | Latch mode                                 | . 29 |

| 4.5.1.4    | Fast restart mode                          | . 29 |

| 4.5.2      | Protection features                        | . 29 |

| 4.5.2.1    | VCC undervoltage lockout                   | 29   |

| 4.5.2.2    | HSVCC undervoltage lockout                 | . 29 |

| 4.5.2.3    | VCC overvoltage protection                 | . 29 |

| 4.5.2.4    | Brown-in protection                        | 29   |

| 4.5.2.5    | Brown-out protection                       | . 30 |

| 4.5.2.6    | Start-up timeout protections               | . 30 |

| 4.5.2.7    | PFC bus overvoltage protection             | . 30 |

| 4.5.2.8    | AC overvoltage protection                  | . 30 |

| 4.5.2.9    | PFC bus undervoltage protection            | . 30 |

| 4.5.2.10   | PFC overcurrent protection                 | . 31 |

| 4.5.2.11   | PFC CCM cycle protection                   | . 31 |

| 4.5.2.12   | Hybrid-flyback overcurrent protection      | . 31 |

| 4.5.2.12.1 | Output overcurrent protection              | . 31 |

| 4.5.2.12.2 | Primary side overcurrent protection CSPROT | . 32 |

| 4.5.2.13   | Output voltage protection                  | . 32 |

| 4.5.2.13.1 | Vout overvoltage protection                | . 32 |

| 4.5.2.13.2 | Vout undervoltage protection               | . 32 |

| 4.5.2.13.3 | Vout short circuit protection              | . 33 |

| 4.5.2.14   | CS pin short circuit protection            | . 33 |

| 4.5.2.15   | FB pin start-up protection                 | 33   |

| 4.5.2.16   | Hybrid-flyback open loop protection        | 33   |

| 4.5.2.17   | External overtemperature protection        | . 33 |

| 4.5.2.18   | Memory parity check                        | . 34 |

| 4.5.3      | Error read-out at MFIO-pin                 | . 34 |

| 5          | Configuration                              | . 35 |

| 5.1        | Configurable parameters and functions      | . 35 |

| 5.1.1      | System settings                            |      |

| 5.1.2      | Supply management                          |      |

| 5.1.3      | Start-up                                   |      |

|            |                                            |      |

### **Table of contents**

|        | Disclaimer                                                | EC |

|--------|-----------------------------------------------------------|----|

| 8      | Revision history                                          | 55 |

| 7      | Package dimensions                                        | 54 |

| 6.4.12 | Central control functions                                 | 53 |

| 6.4.11 | PFC gate driver (PFCGD pin)                               | 52 |

| 6.4.10 | Low-side gate driver (LSGD pin)                           | 52 |

| 6.4.9  | Hybrid-flyback output feedback (FB pin)                   | 52 |

| 6.4.8  | Hybrid-flyback current sensing (CS pin)                   | 51 |

| 6.4.7  | Multifunctional input and output (MFIO pin)               | 51 |

| 6.4.6  | Hybrid-flyback zero crossing detection (ZCD pin)          | 51 |

| 6.4.5  | PFC current sense and zero crossing detection (PFCCS pin) |    |

| 6.4.4  | Bus voltage sensing (PFCVS pin)                           |    |

| 6.4.3  | Floating HS domain (HSGND, HSVCC and HSGD pin)            | 50 |

| 6.4.2  | Power supply (VCC pin)                                    |    |

| 6.4.1  | High voltage (HV pin)                                     |    |

| 6.4    | Characteristics                                           |    |

| 6.3    | Operating conditions                                      |    |

| 6.2    | Package Characteristics                                   |    |

| 6.1    | Absolute maximum ratings                                  |    |

| 6      | Electrical characteristics                                |    |

| 5.2    | Tolerance classes for configurable parameters             | 41 |

| 5.1.7  | Protections                                               |    |

| 5.1.6  | PFC bus voltage target settings                           | 39 |

| 5.1.5  | PFC operation                                             |    |

| 5.1.4  | Hybrid-flyback operation                                  |    |

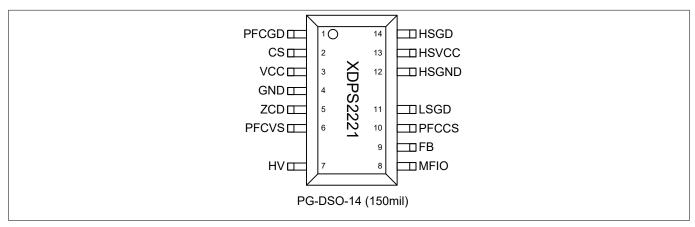

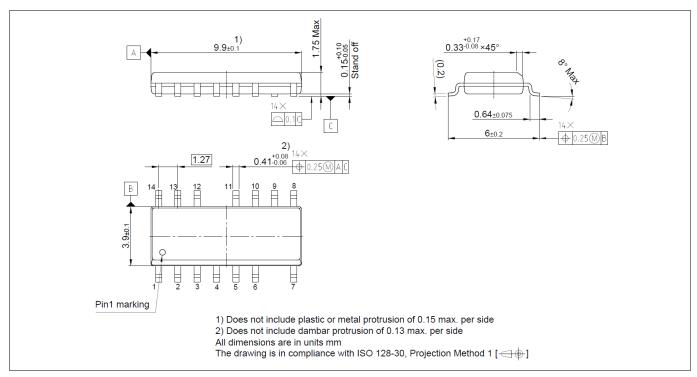

## 1 Pin Configuration and Functionality

### **Pin Configuration and Functionality** 1

The pin configuration is shown in the figure below and the functions are described in the following table.

| Table 1 | Pin Definitions and | Functions |

|---------|---------------------|-----------|

|---------|---------------------|-----------|

| Symbol | Pin | Type | Function                                                                                                                                                                                                                                            |

|--------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PFCGD  | 1   | 0    | PFC gate driver                                                                                                                                                                                                                                     |

|        |     |      | This pin drives the PFC transistor via a gate resistor.                                                                                                                                                                                             |

| CS     | 2   | 1    | Hybrid-flyback current sense                                                                                                                                                                                                                        |

|        |     |      | Input pin for current sensing during the hybrid-flyback high-side gate driver turn-on phase.                                                                                                                                                        |

| VCC    | 3   | 1    | Power supply                                                                                                                                                                                                                                        |

|        |     |      | This pin supplies the IC. During start-up VCC is supplied from the AC via the HV-pin, while during normal operation VCC is supplied from the auxiliary winding to the hybrid-flyback stage.                                                         |

| GND    | 4   | 0    | Ground level of the IC for supply voltage, gate drive and sense signals.                                                                                                                                                                            |

| ZCD    | 5   | I    | Hybrid-flyback zero crossing detection                                                                                                                                                                                                              |

|        |     |      | This pin provides zero crossing detection after low-side gate driver turned off and during pause phase in burst mode. Furthermore, the reflected output voltage at the auxiliary winding can be measured during low-side gate driver turn-on phase. |

| PFCVS  | 6   | I    | PFC bus voltage sense                                                                                                                                                                                                                               |

|        |     |      | This pin is connected to a high impedance resistor divider from the PFC controller output for bus voltage sensing.                                                                                                                                  |

| HV     | 7   | I    | High voltage input                                                                                                                                                                                                                                  |

|        |     |      | The HV pin is connected to the input AC voltage. An internal HV startupcell is used for initial VCC charging and AC brown-in detection.                                                                                                             |

| MFIO   | 8   | 1    | Multi-functional Input Output                                                                                                                                                                                                                       |

|        |     |      | This pin is connected to GND through an external NTC resistor used to detect ambient temperature. Furthermore, UART communication for parameter configuration and error code reporting is provided by this pin.                                     |

| FB     | 9   | I    | Feedback                                                                                                                                                                                                                                            |

|        |     |      | This pin receives feedback from the secondary side via an optocoupler.                                                                                                                                                                              |

| PFCCS  | 10  | 1    | PFC current sense and PFC zero crossing detection                                                                                                                                                                                                   |

|        |     |      | This pin is configured for PFC current sensing in combination with zero crossing detection of the PFC choke current.                                                                                                                                |

| LSGD   | 11  | 0    | Hybrid-flyback low-side gate driver                                                                                                                                                                                                                 |

|        |     |      | This pin drives the low-side transistor of the hybrid-flyback half-bridge.                                                                                                                                                                          |

| HSGND  | 12  | I    | High-side Ground                                                                                                                                                                                                                                    |

|        |     |      | Ground reference node for hybrid-flyback floating high-side driver domain.                                                                                                                                                                          |

| HSVCC  | 13  | 1    | High-side power supply                                                                                                                                                                                                                              |

|        |     |      | Power supply input for hybrid-flyback floating high-side driver domain.                                                                                                                                                                             |

(table continues...)

## 1 Pin Configuration and Functionality

## Table 1 (continued) Pin Definitions and Functions

| Symbol | Pin | Туре | Function                                                                                                    |

|--------|-----|------|-------------------------------------------------------------------------------------------------------------|

| HSGD   | 14  | 0    | High-side gate driver                                                                                       |

|        |     |      | This pin drives the high-side transistor of the hybrid-flyback half-bridge from the floating driver domain. |

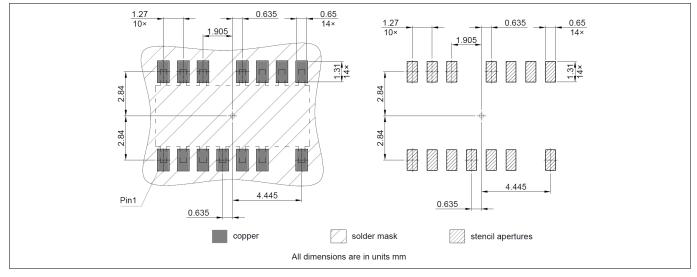

Figure 1 Pin configuration

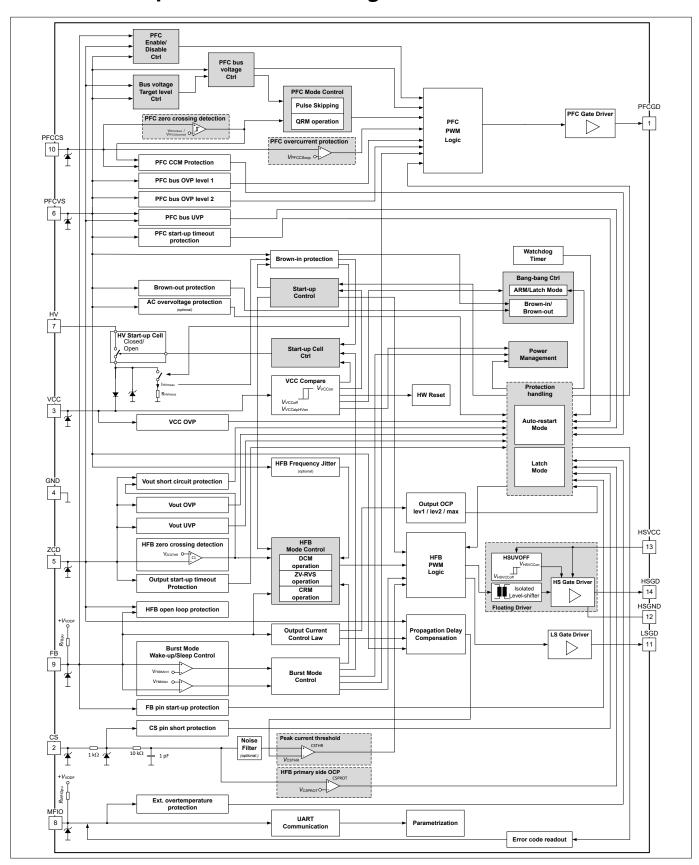

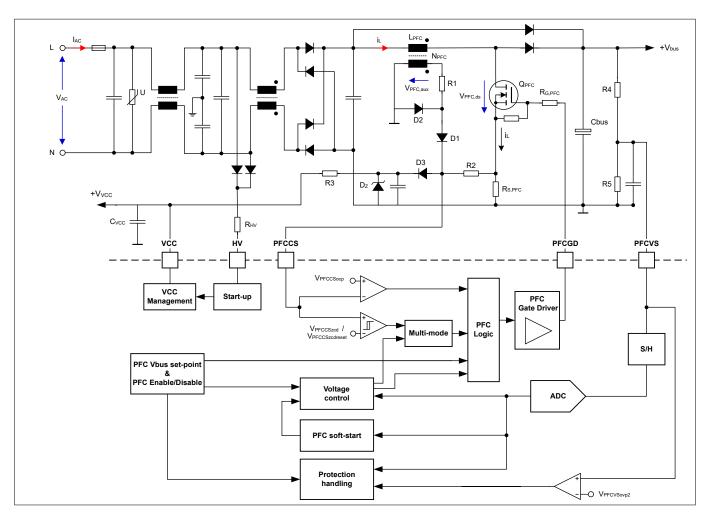

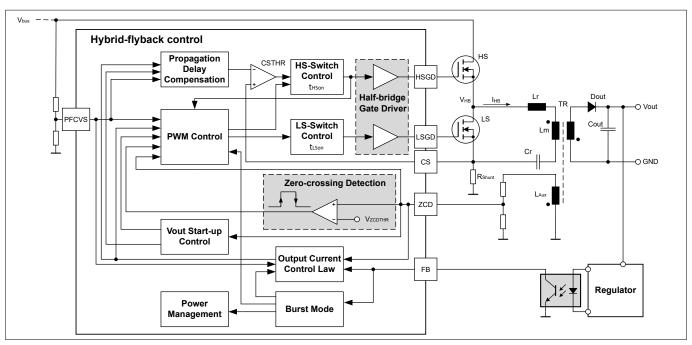

### 2 Representative Block Diagram

### **Representative Block Diagram** 2

Figure 2 **Block diagram**

### **Datasheet**

### Introduction 3

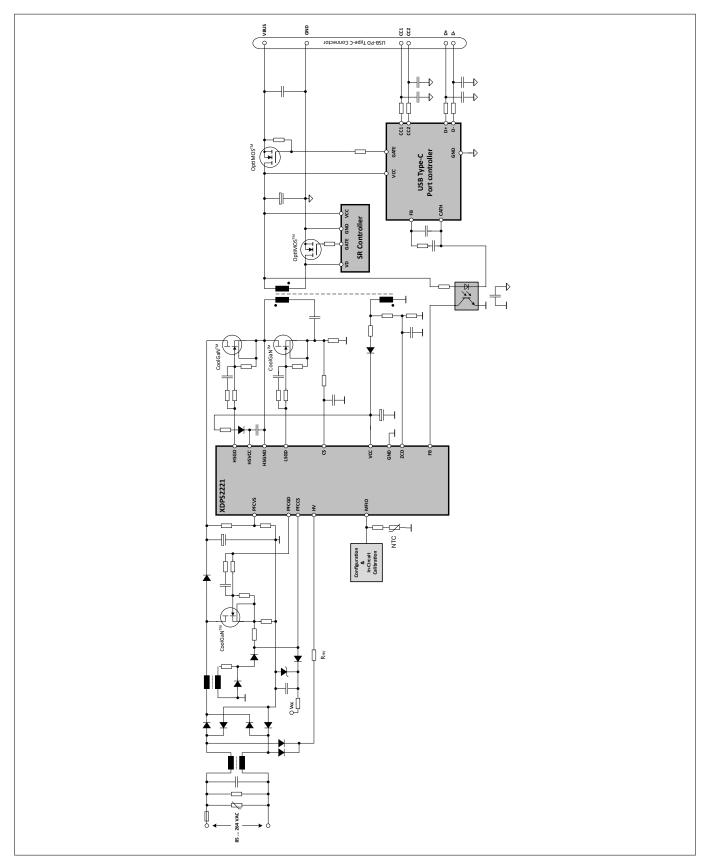

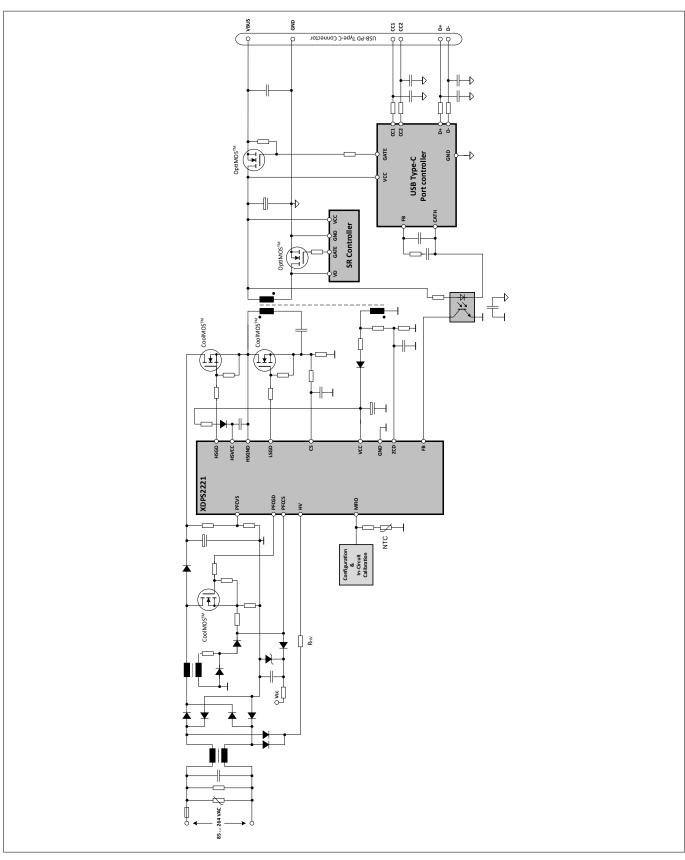

The XDPS2221 PWM controller is a highly integrated device combining a multimode ac-dc PFC controller and a multimode dc-dc hybrid-flyback controller. The integration of PFC and hybrid-flyback into a single controller enables reduction of external parts and optimizes performance by joint operation of the two stages. It is meant to be used in USB-PD chargers / adapters with wide output voltage up to 28 V.

The system efficiency can further be increased using Infineon CoolMOS<sup>TM</sup>, CoolGaN<sup>TM</sup> and OptiMOS™ transistors. Below a typical application schematics in a USB-PD application are depicted.

Figure 3 shows the potential application schematic using CoolGaN<sup>TM</sup> and OptiMOS<sup>TM</sup> transistors for highest efficiency and power density.

Figure 4 shows the potential application schematic using CoolMOS<sup>TM</sup> and OptiMOS<sup>TM</sup> transistors.

## **Datasheet**

### 3 Introduction

Typical application in combination with CoolGaN™ transistors Figure 3

### **Datasheet**

Figure 4 Typical application in combination with CoolMOS<sup>TM</sup> transistors

### **Datasheet**

### 4 Functional description

### **Functional description** 4

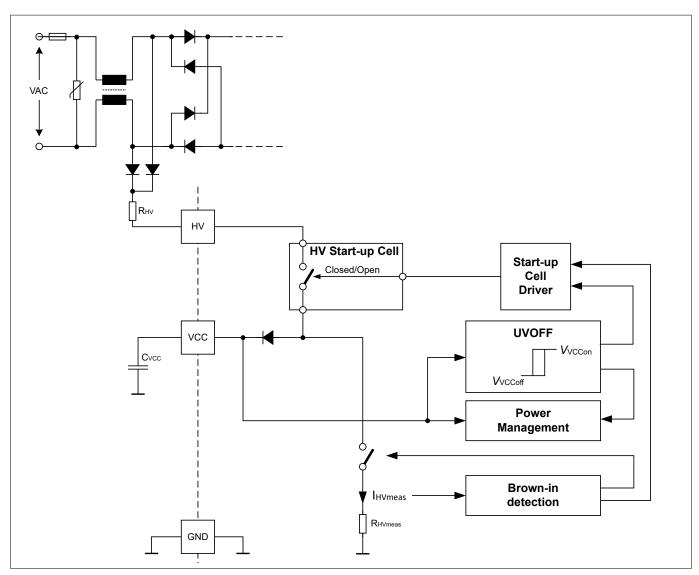

### 4.1 Power-supply and high voltage start-up cell management

The power supply management ensures a reliable and robust IC operation. Depending on the operation mode of the control IC, the power supply management unit runs in different ways for VCC supply, which are described as in the sequel.

### VCC capacitor charge-up and start-up sequence 4.1.1

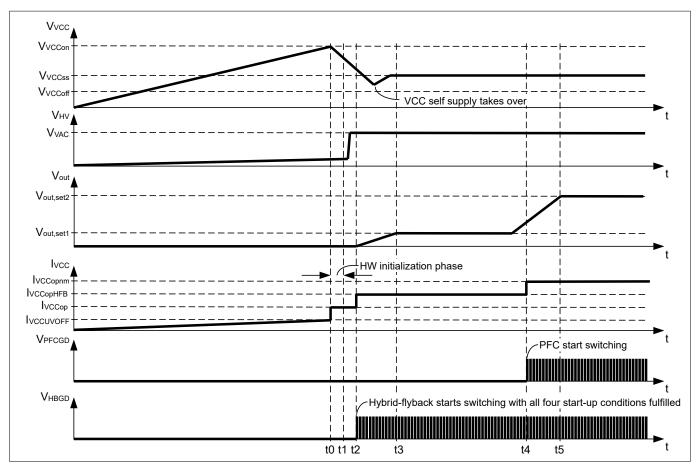

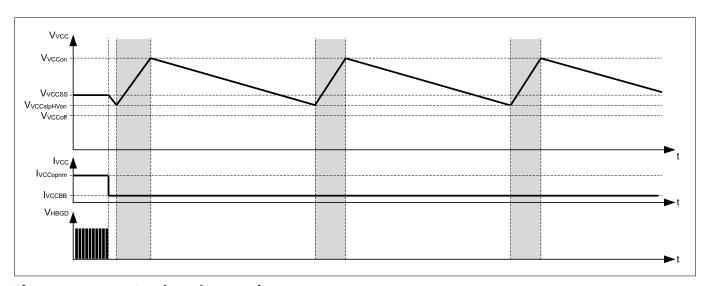

At VCC start-up the capacitor C<sub>VCC</sub> is charged by the internal HV start-up cell via HV pin (see Figure 5). The internal HV start-up cell is turned on for V<sub>VCC</sub> lower than the IC deactivation voltage threshold V<sub>VCCoff</sub>. Once the voltage at pin VCC exceeds the threshold V<sub>VCCon</sub> at time t0 the HV start-up cell is turned off and the IC is starting up (see Figure 6).

The IC operation is started at time t1 and the start-up conditions are validated afterwards.

Following conditions need to be fulfilled to start the hybrid-flyback operation at time t2 (hybrid-flyback switching is indicated by signal V<sub>HBGD</sub>):

- Two-level brown-in condition with V<sub>in</sub> > V<sub>inbi</sub> and V<sub>bus</sub> > V<sub>busbi</sub> (see Chapter 4.5.2.4))

- 2. No input overvoltage with V<sub>bus</sub> < V<sub>busACovp</sub> (see Chapter 4.5.2.8)

- Feedback signal out of regulation range with V<sub>FB</sub> > V<sub>FBBMctrl</sub> 3.

- 4. No overtemperature condition with  $R_{MFIO} > R_{MFIOOTPrel}$ . (see Chapter 4.5.2.17)

The conditions need to be met within the time period t<sub>HVbito</sub>. With hybrid-flyback switching, the the external VCC self-supply takes over the IC supply. In case one of those conditions is not met the IC enters bang-bang during brown-in phase (see Chapter 4.1.2).

Note:

In the typical application the output voltage target value is set by the USB-PD controller. At start-up, no load is applied and the target value is first set by the USB-PD controller to e.g.  $V_{\text{out,set1}} = 5 \text{ V}$  and only after having reached a stable output voltage condition the USB-PD controller activates the load and sets the proper output voltage required by the attached device.

PFC operation depends on operating conditions and might not be required at start-up. Hybrid-flyback operation starts first, if required, PFC operation comes up afterwards. Figure 6 shows a situation with an output voltage request from USB-PD controller with V<sub>out.set2</sub> > V<sub>out.set1</sub> after a while. In this case PFC operation is started at t₄.

## **Datasheet**

## 4 Functional description

Figure 5 HV control for start-up and brown-in detection

### **Datasheet**

### 4 Functional description

Figure 6 Typical start-up sequence

### 4.1.2 Bang-bang mode operation during brown-in phase

In order to support a fast activation as soon as brown-in condition is fulfilled, the VCC voltage is kept at a high level. A bang-bang mode operation for the start-up check phase is ensuring a high VCC level.

For example, after a brown-out event the IC enters a sleep mode with reduced current consumption I<sub>VCCBB</sub>. The HV start-up cell turns on and tries to charge up the VCC voltage to the threshold V<sub>VCCon</sub>. When AC input voltage comes back  $V_{VCC}$  can reach  $V_{VCCon}$  and the IC gets active for brown-in detection for a short time. If AC input voltage is high enough the IC detects the brown-in condition.

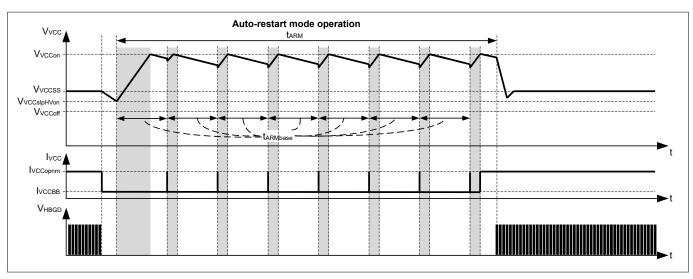

### Bang-bang mode during protection mode operation 4.1.3

In auto-restart operation, the the HV start-up cell is regularly turned on after a time period t<sub>ARMbase</sub> and turned off when reaching VCC pin voltage threshold V<sub>VCCon</sub>. During this bang-bang mode operation the VCC is kept at a high voltage level in order to support a proper restart operation (see Figure 7). A system restart happens after the auto-restart time t<sub>arm</sub> is expired.

In latch mode operation, the HV start-up cell is turned on at VCC pin voltage threshold V<sub>VCCslpHVon</sub> and turned off when reaching VCC pin voltage threshold V<sub>VCCon</sub> (see Figure 8). A reset can only be achieved by disconnecting the AC line once the VCC voltage drops below the threshold  $V_{VCCoff}$ .

### **Datasheet**

### 4 Functional description

Figure 7 Auto-restart mode operation

Latch mode operation Figure 8

### VCC supply during burst mode (BM) operation 4.1.4

During burst mode operation the IC enters repeatedly a power saving mode, in which the IC current consumption is reduced to I<sub>VCCBMpsm</sub>. During the burst active time, VCC should be supplied externally from the auxiliary winding.

In burst-mode the controller can also be configured to use the HV start-up cell to support VCC supply. When enabled and the VCC voltage drops below the threshold V<sub>VCCsIpHVon</sub>, the HV start-up cell is activated and charges the VCC capacitor.

### **PFC** control 4.2

The PFC controller turns on and off the PFC gate driver PFCGD so that a desired bus voltage V<sub>bus</sub> is maintained while the AC input current I<sub>AC</sub> follows the instantaneous line input voltage V<sub>AC</sub> resulting in high power factor and low harmonic content. The operation mode is based on quasi-resonant operation mode (QRM), thus critical conduction mode, but with valley switching and valley skipping. The oscillation of the switch voltage V<sub>PEC ds</sub> after choke current demagnetization is detected via an integrated zero crossing detection (ZCD) mechanism. The ZCD-function is combined with a PFC overcurrent protection at pin PFCCS. Figure 9 shows the PFC circuit arrangement including the AC input stage and the PFC control part of the IC.

### **4 Functional description**

Figure 9 QRM-PFC circuit arrangement and associated PFC control

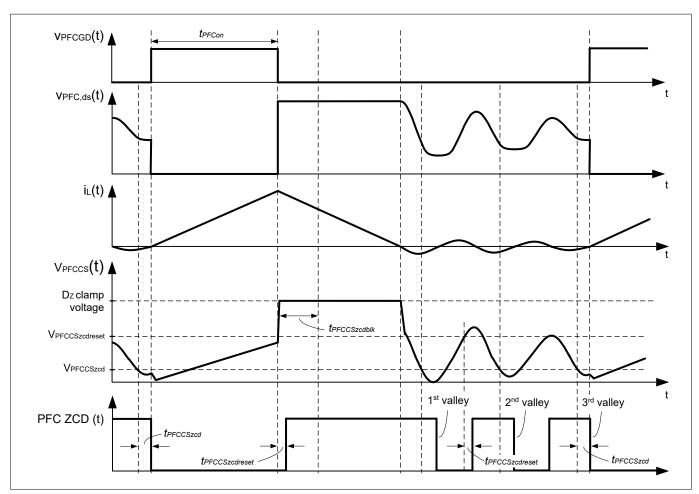

The PFC controller is operating in quasi-resonant mode (QRM) with valley switching. Typical waveforms are depicted in Figure 10. In the shown case, the PFC is turned on in the third valley.

### **Datasheet**

# **i**nfineon

### 4 Functional description

Figure 10 PFC switching cycle with transistor turn-on in the 3rd valley (QRM3)

# 4.2.1 Combined current sense (CS) and zero crossing detection (ZCD) function

The PFC stage uses a combined current sense (CS) and zero crossing detection (ZCD) functionality at pin PFCCS. During the PFC gate driver on-time the pin acts as a current sense (CS), while during the gate driver off-time the pin acts as a zero-crossing-detector (ZCD) for valley switching. Please refer to Figure 9 for the related circuitry for ZCD and CS.

Valley detection is done through an external circuit connected to the auxiliary winding of the PFC inductor. A hysteretic comparator with a lower threshold of  $V_{PFCCSzcd}$  for falling edges and an upper threshold  $V_{PFCCSzcdreset}$  for rising edges of the signal at PFCCS is used. A ZCD event is triggered in case  $V_{PFCCS}$  falls below the threshold  $V_{PFCCSzcd}$ . In case the target valley is reached, the gate driver output PFCGD only goes high after the delay time  $t_{PFCCSzcd}$ . However, a (new) ZCD event can only be detected after the voltage at PFCCS was above the upper comparator threshold  $V_{PFCCSzcdreset}$  for longer than the configurable filter and delay time  $t_{PFCCSzcdreset}$ . For ringing suppression due to switching, the ZCD signal is blanked for  $t_{PFCCSzcdblk}$  after PFGGD falling edge. The signal showing the hysteretic comparator output in Figure 10 illustrates this mechanism.

The measured voltage at the shunt resistor  $R_{S,PFC}$  during the PFC gate driver on-time is used for PFC overcurrent limitation. Once the voltage at pin PFCCS exceeds the overcurrent threshold  $V_{PFCCSocp}$  for longer than the blanking time  $t_{PFCCSocp}$  the PFC gate PFCGD is turned off.

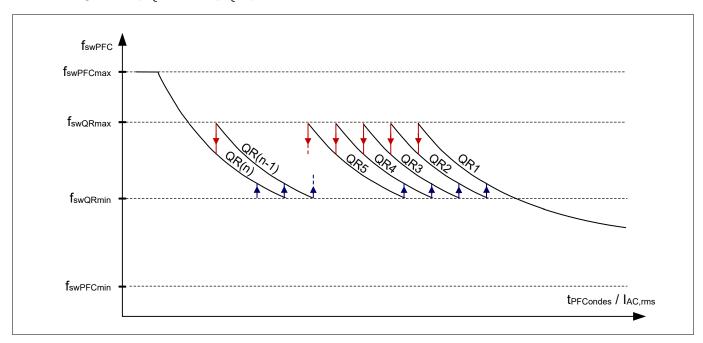

## 4.2.2 Multimode operation and frequency law

The PFC controller provides various modes of operation. When going from full to no load several operation modes are used in order to optimize efficiency and EMI behavior.

### **Datasheet**

### 4 Functional description

A PFC converter is used to emulate a resistive load  $R_e = V_{AC,rms} / I_{AC,rms}$  to the AC input. The output of the PFC bus voltage controller  $t_{PFCon,des}$  is inversely proportional to the emulated resistive load  $R_e$ . Thus,  $t_{PFCon,des}$  varies as the AC line voltage magnitude varies and is proportional to the RMS input current  $I_{AC,rms}$ .

The frequency law depicted in Figure 11 indicates the operation mode for the complete range, which can be  $t_{PFCon,des}$  or  $I_{ac,rms}$  range. A limitation within a minimum switching frequency  $f_{swPFCmin}$  and a maximum switching frequency  $f_{swPFCmax}$  is applied in every switching cycle. In QRM exceeding the thresholds  $f_{swQRmax}$  and  $f_{swQRmin}$  for longer than the given blanking time lead to a change of valley to bring the switching frequency back into the range from  $f_{swQRmin}$  and  $f_{swQRmax}$  (see Chapter 4.2.2.1).

Figure 11 Frequency law

## 4.2.2.1 Quasi-resonant mode (QRM)

In quasi-resonant operation mode (QRM) the PFC switch is turned on in the valley of the oscillation seen at the switch's drain-source voltage after demagnetization. QRM reduces PFC transistor switching losses and ensures highest possible efficiency of the system.

In QR1 operation the first valley is used. The transistor is turned on as soon as the first ZCD event is detected.

With decreasing load or increasing input voltage switching frequency is increasing and the maximum switching frequency  $f_{swQRmax}$  is hit. In this case the valley number should be increased. With load getting higher or input voltage decreasing, the lower frequency limit  $f_{swQRmin}$  will be hit and the valley number should be decreased.

However, in order to prevent valley number change within each AC half cycle, valley change blanking times  $\underline{t}_{QRblkinc}$  and  $\underline{t}_{QRblkinc}$  apply.

In order to ensure good ZCD detection before the PFCCS signal gets too small in amplitude, only 1st valley (QR1) to a configurable  $n^{th}$  valley  $N_{PFCvalleymax}$  are supported. In case  $N_{PFCvalleymax}$  is reached the frequency is only limited by  $f_{swPFCmax}$ .

The time during QR valley oscillation, when neither PFC switch nor PFC diode is conducting, is responsible for some AC input current waveform distortion and affects the PFC THD performance. The multimode PFC controller uses an algorithm that optimizes the applied on-time on a cycle by cycle basis so as to ensure good input current shaping and improve PFC THD performance.

### 4.2.2.2 Low power mode

In softstart and steady operation, as soon as the on-time  $t_{\text{PFCondes}}$  determined by the bus voltage controller is less than a value  $t_{\text{PFConskip}}$  the switching pulse is skipped and PFC gate driver is not switching. Depending on the configuration of parameter  $\text{CFG}_{\text{PFContime}}$ , the value of  $t_{\text{PFConskip}}$  is equal to a constant on-time  $t_{\text{PFConmin}}$ , with  $t_{\text{PFConmin}} \ge t_{\text{PFCCSleb}}$ , or it can be set to be scaled with the AC line rms voltage.

### **Datasheet**

### 4 Functional description

At low output load, the combo controller IC goes into burst mode. The PFC burst mode operation is synchronous to the hybrid-flyback burst mode operation.

### PFC bus voltage sensing and regulation 4.2.3

The controller senses the PFC output voltage V<sub>bus</sub> via pin PFCVS. The bus voltage is maintained by a nonlinear PIT1 controller that calculates the desired on-time t<sub>PFCondes</sub> in response to the sensed voltage.

The PFC on-time from regulation t<sub>PFCondes</sub> is limited to a configurable minimum value t<sub>PFConmin</sub> and a maximum value t<sub>PFConmax</sub>.

The PFC target bus voltage and the bus voltage undervoltage protection level V<sub>busUVP</sub> are set dynamically by the controller. In case the bus voltage V<sub>bus</sub> drops and is getting close to V<sub>busUVP</sub>, the controller reacts and increases the on-time to the maximum on-time t<sub>PFConmax</sub> in order to boost up the bus voltage.

In order to compensate for the AC line gain dependency of the boost power stage, the PIT1-controller processes the previous sample of t<sub>PECondes</sub> in nonlinear way. This is used as a kind of AC input feedforwardcontrol.

### 4.2.4 PFC bus voltage target setting

In contrast to a conventional PFC boost converter, the bus voltage target level V<sub>bustarget</sub> is not fixed but changing with operation conditions. On the one hand, the hybrid-flyback stage is requesting some bus voltage target level depending on the output voltage V<sub>out</sub>. On the other hand, the PFC itself can set a target bus voltage level following the AC peak voltage. This feature is described in more detail in Chapter 4.4.3.

### **PFC soft-start** 4.2.5

Each time the PFC is enabled, the PFC initiates a soft start to minimize the switching stress on the power MOSFET, diode and inductor. During a soft start, the PFC operates in QR1-mode. The soft-starts ends as soon as the bus voltage has reached 93.75% of the target value  $V_{bustarget}$  or when PFC pulse skipping mode is entered. The initial on-time depends on the configuration of parameter CFG<sub>PFContime</sub>: It is either fixed or will be scaled with the AC line rms voltage.

### 4.2.6 **PFC** gate driver

A PFC gate driver is integrated in the controller at pin PFCGD. In order to drive discrete GaN-HEMT devices, a dedicated external RC-network is recommended.

### 4.2.7 **PFC disable**

The PFC can be disabled completely and permanently by configuration. At the same time all PFC related protections are automatically disabled. The hybrid-flyback and related house-keeping functions are still enabled.

The controller with disabled PFC functionality is meant to be combined with a separate, standalone PFC controller providing a regulated bus voltage V<sub>bus</sub> which is high enough for reliable operation of the hybridflyback in all operation conditions. Otherwise, PFC bus undervoltage protection will trigger (see Chapter 4.5.2.9).

### 4.3 **Hybrid-flyback control**

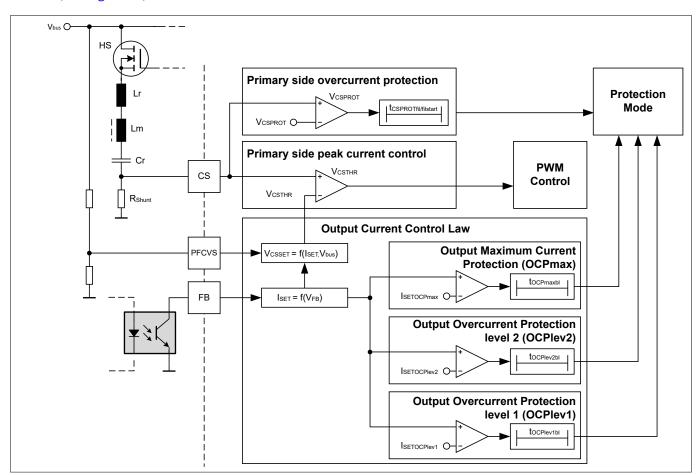

The hybrid-flyback converter is based on a resonant asymmetrical half-bridge topology with flyback output. Figure 12 shows the hybrid-flyback stage with the associated control blocks.

The hybrid-flyback power stage can achieve zero voltage switching (ZVS) operation on primary side and zero current switching (ZCS) operation on secondary side under all conditions of bus voltage V<sub>bus</sub> and output voltage V<sub>out</sub> with proper system design. In order to achieve ZVS operation, two control methods are implemented:

- Continuous resonant mode (CRM) operation

- Zero voltage resonant valley switching (ZV-RVS) operation

### **Datasheet**

### 4 Functional description

Figure 12 Hybrid-flyback circuit arrangement with associated control blocks

The output current control uses the CSTHR-comparator for peak current control via high-side switch on-time  $t_{HSon}$ .

### 4.3.1 PWM control schemes

In the following chapter the pulse width modulation (PWM) control methods for the different control modes and the associated mode transition are discussed. Depending on load, output voltage and bus voltage the control scheme is adjusted to ensure ZVS operation for both low-side and high-side switches.

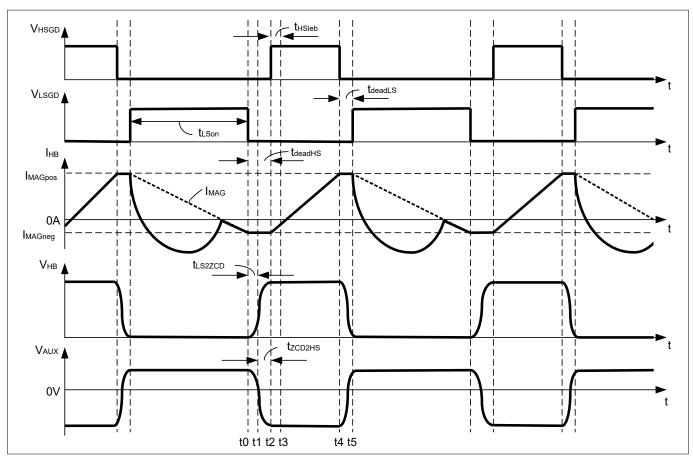

### 4.3.1.1 CRM control scheme

In continuous resonant mode (CRM) the switching of high-side switch HS and low-side switch LS is done in a continuous alternating manner with short dead-times  $t_{\rm deadHS}$  for the high-side switch turn-on and  $t_{\rm deadLS}$  for the LS switch turn-on.

It targets a ZVS operation for every half-bridge switching cycle by tuning the negative current level  $I_{MAGneg}$ . In Figure 13 typical waveforms are shown. The dead-time  $t_{deadLS}$  between HS and LS switch is fixed as the peak current is high enough to provide proper ZVS operation for LS switch.

### **Datasheet**

# **i**nfineon

### 4 Functional description

Figure 13 Half-bridge timings for CRM operation

In CRM operation the dead-time t<sub>deadHS</sub> consists of two time intervals:

$$t_{deadHS}(CRM) = t_{LS2ZCD} + t_{ZCD2HS}$$

### **Equation 1**

The LS on-time is adjusted cycle-by-cycle for a target delay time  $t1 - t0 = t_{LS2ZCD}(V_{bus})$ , based on the configurable corners  $t_{LS2ZCDmax} = t_{LS2ZCD}(V_{bus} = V_{Cr})$  and  $t_{LS2ZCDmin} = t_{LS2ZCD}(V_{bus} = V_{busACovp})$ .

The configurable time period  $t2 - t1 = t_{ZCD2HS}$  is delaying the HS switch turn-on at time t2 so that HS ZVS is possible.

The HS switch is activated when the deadtime  $t_{deadHS}(CRM)$  is over or when the switching period exceeds 327  $\mu s_{typ}$ .

After the HS switch is activated, the peak current control determines the HS on-time. The magnetizing current can be measured after a leading edge spike blanking period  $t_{HSleb}$ , which therefore determines the minimum on-time of HS switch operation.

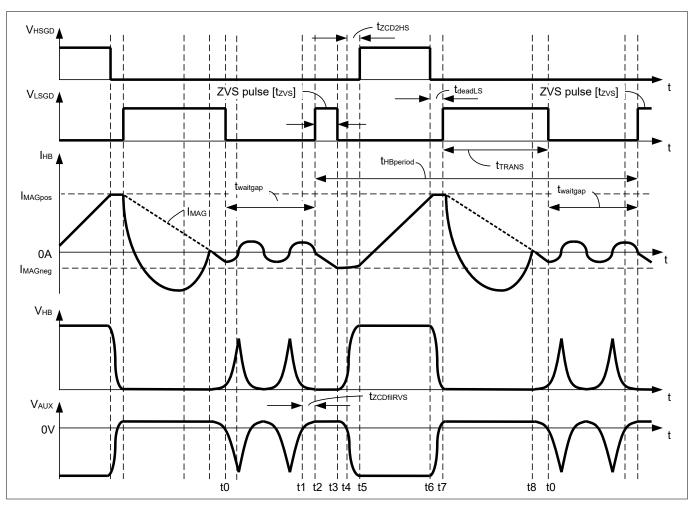

### 4.3.1.2 ZV-RVS control scheme

When decreasing the load the amount of circulating magnetization energy is increasing compared to the transmitted energy in CRM operation. When decreasing  $V_{out}$  the demagnetization time is becoming much longer than half of the resonant period of the LrCr tank, which can lead to further resonant half-bridge oscillations. Turning off the LS switch during an ongoing  $I_{HB}$  oscillation can lead to oscillations on the secondary side due to the secondary side leakage inductance.

To overcome these issues the zero voltage resonant valley switching (ZV-RVS) mode is provided. It keeps the peak magnetizing current in the desired range while maintaining soft switching of both HS and LS switch. Lower load is addressed by lower switching frequency. Figure 14 shows typical waveforms when operating in the second valley.

### **Datasheet**

### 4 Functional description

Compared to CRM, there are two LS pulses during HS off-time with a wait gap t<sub>waitgap</sub> in-between. The first LS pulse demagnetizes the LrCr tank and charges the output capacitor on the secondary side. The waiting time gap t<sub>waitgap</sub> is inserted at time t0 after a HS and LS switch half-bridge cycle. During the wait gap, a free-wheeling oscillation takes place which is sensed by pin ZCD with a comparator. The second LS pulse, the so-called ZVS pulse t<sub>ZVS</sub>, starts shortly after the first or a later rising edge detection of the ZCD comparator at time t1 and a configurable delay time period t<sub>ZCDfiRVS</sub> so that the LS switch turns on at a valley of the drain-source voltage and zero magnetizing current. Hence, a resonant valley switching (RVS) operation is achieved. Selecting a later valley increases the wait gap duration  $t_{waitgap}$  and lowers the switching frequency. The ZVS pulse further demagnetizes the the LrCr tank to a negative value I<sub>MAGneg</sub> for zero-voltage switching (ZVS) of the HS switch. The required ZVS pulse length t<sub>ZVS</sub> is determined by the target negative magnetization level I<sub>MAGneg</sub>, the transformer magnetizing inductance Lm and depends on the output voltage Vout. The minimum ZVS pulse length occurs at lowest input and highest output voltage. In addition a lower limit t<sub>7VSmin</sub> applies.

During the first switching cycles of the hybrid-flyback start-up the dead-time for turning on the HS switch after the ZVS pulse is fixed with using the value  $t_{deadHSRVS}$ . The subsequent dead-time  $t_{deadLS}$  is same as in CRM operation.

Selecting the appropriate valley and adjusting the magnetizing peak current within the desired range controls the load.

Figure 14 Hybrid-flyback operating in zero voltage resonant valley switching mode (ZV-RVS)

### 4.3.1.3 Valley skipping control

When operating in ZV-RVS mode, valley detection is taking place to determine the time for turning on the ZVS pulse. The waiting time  $t_{waitgap}$  is controlled based on the target number of detected valleys.

The target valley number is chosen so that the magnetizing peak current is in the desired range to ensure an optimum operation. If the target valley cannot be detected, the controller will enter DCM operation with a similar fixed frequency.

### **Datasheet**

### 4 Functional description

### 4.3.1.4 DCM control scheme

ZV-RVS mode operation at light-load is limited by the maximum number of detectable zero-crossings at ZCD due to decreasing oscillation magnitude with prolongation of the inserted waiting time gap  $t_{waitgap}$ . When further reducing the output current the waiting time gap  $t_{waitgap}$  is further increased until the ZVS pulse is initiated without zero-crossing detection. The subsequent half-bridge cycle is then again performed under ZVS condition. Increasing  $t_{waitgap}$  takes only place until the half-bridge period  $t_{HBperiod}$  reaches the associated minimum half-bridge switching frequency  $f_{swDCMmin}$ .

### 4.3.1.5 Mode transition between CRM and ZV-RVS

The mode transition control is based on the target peak current  $I_{MAGpos}$  and the voltage measured at ZCD pin. First, a transition from CRM to ZV-RVS mode and vice versa is only possible in case the output voltage, sensed via ZCD, has a certain value. The transition from ZV-RVS to CRM is only possible with a detected output voltage greater than  $V_{outRVS2CRM}$  (in order to have some hysteresis, the transition from CRM back to ZV-RVS only happens for an output voltage smaller than  $V_{outCRM2RVS}$ ). Second, the feedback signal  $V_{FB}$  is determining the internal current set-point  $V_{SET}$  and compared with the internal thresholds for changeover.

### 4.3.2 Output control

Similar as in standard flyback controllers primary peak current control is implemented to support a  $1^{st}$  order system for easier control loop compensation. The input power per half-bridge switching cycle is depending on the voltage at the resonant capacitor  $C_r$  that is charged by the half-bridge current  $I_{HB}$  during the on-time  $t_{HSon}$ . The input power in CRM-mode can be calculated as shown in the following equation:

$$P_{in} = \frac{1}{2} \cdot V_{Cr, avg} \cdot \left( I_{MAGpos} + I_{MAGneg} \right)$$

### **Equation 2**

$V_{\text{Cr,avg}}$  is the average voltage on the resonant capacitor  $C_r$ , which is the reflected output voltage  $V_{\text{out}}$  multiplied with the transformer turns ratio. The output voltage is reflected at winding  $L_{\text{AUX}}$  during the on-time period of LS switch.

$$V_{Cr, avg} = N \cdot V_{out}$$

### **Equation 3**

Assuming an ideal system leads to a direct correlation between input half-bridge current I<sub>HB</sub> and average output current I<sub>out</sub>:

$$I_{out} = \frac{P_{out}}{V_{out}} = \frac{1}{2} \cdot N \cdot \left(I_{MAGpos} + I_{MAGneg}\right)$$

### **Equation 4**

Compared to CRM operation the ZV-RVS mode is adding waiting time gaps t<sub>waitgap</sub>, where no energy transfer is happening. The average output current I<sub>out</sub> is decreasing with increasing t<sub>waitgap</sub> according to

$$I_{out} = \frac{P_{out}}{V_{out}} = \frac{t_{HBperiod} - t_{waitgap}}{t_{HBperiod}} \cdot \frac{1}{2} \cdot N \cdot \left(I_{MAGpos} + I_{MAGneg}\right)$$

### **Equation 5**

The output current is only controlled by means of the positive magnetization current level  $I_{MAGpos}$ . During continuous operation the output current  $I_{out}$  is controlled by means of a linear relationship between the feedback voltage at FB pin and the associated internal current set-point  $I_{SET}$ , which is described in Chapter 4.3.2.1. The negative current  $I_{MAGneg}$  is chosen so that ZVS of the HS is achieved. The value of  $I_{MAGneg}$  is a function of  $V_{bus}$ .

### **Datasheet**

### 4 Functional description

The output voltage is measured via pin ZCD at the auxiliary winding and is used for protection features, for compensation to ensure ZVS operation over wide output voltage range (see Chapter 4.3.2.3) as well as for estimating the average voltage V<sub>Cr,avg</sub> on the resonant capacitor according to Chapter 4.3.2. The internal averaging uses a filter with configurable filter time constant T<sub>CVzcdavg</sub>.

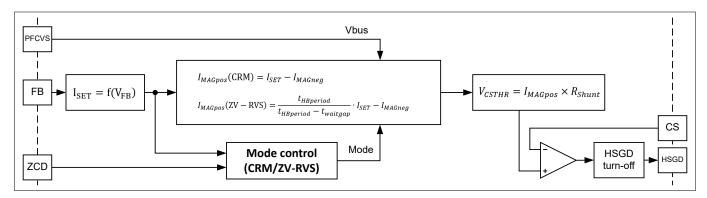

### 4.3.2.1 **Output current control law**

The positive magnetization level I<sub>MAGpos</sub> equals the positive half-bridge peak current that is controlled via CS pin at the shunt resistor R<sub>Shunt</sub>:

$$V_{CSpeak} = I_{MAGpos} \cdot R_{Shunt}$$

### **Equation 6**

Peak current regulation is prone to error due to noise. CS pin related PCB design should consider this sensitivity. An external high-frequency R-C-filter at CS pin is recommended. In addition, a digital filter using a configurable filter time t<sub>CSTHRfil</sub> can be set to blank the CSTHR comparator event.

Figure 15 shows the control path from feedback signal input at FB pin to peak current setting at CS pin. The requested output current equals to the internal I<sub>SET</sub> for the corresponding feedback signal. The required peak current setting is then calculated based on V<sub>bus</sub> measurement and mode operation.

Figure 15 Control path from feedback input to peak current setting

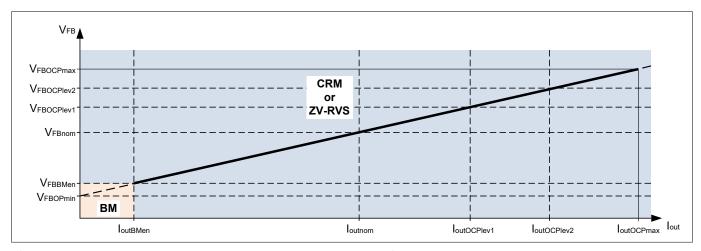

The feedback pin has a pull-up resistor R<sub>FBpu</sub> to V<sub>FBoc</sub>. The value of the pull-up resistor R<sub>FBpu</sub> is configurable. The feedback voltage V<sub>FB</sub> has a linear correlation with the output current I<sub>out</sub> between burst mode entry current level I<sub>outBMen</sub> and the maximum output current I<sub>outOCPmax</sub>. Figure 16 shows the relationship between output current and feedback voltage.

Figure 16 Control law for feedback voltage at FB pin

In the IC output current I<sub>out</sub> is represented by the equivalent internal current set-point I<sub>SET</sub>, which is then mapped to the positive magnetization level I<sub>MAGpos</sub>. The peak current I<sub>MAGpos</sub> is controlled by a comparator with variable threshold at pin CS. The relation between I<sub>SET</sub> and I<sub>MAGpos</sub> is different for CRM and ZV-RVS mode.

### **Datasheet**

### 4 Functional description

## 4.3.2.2 Keeping ZVS operation for wide Vbus voltage range

The ZVS operation in CRM is explained in Chapter 4.3.1.1. In ZV-RVS, the ZVS pulse length is set targeting a negative current  $I_{MAGneg}$  as described in Chapter 4.3.1.2. Here,  $I_{MAGnegnom}$  is the target negative current at  $V_{bus} = V_{Cr}$ . For higher bus voltages the absolute value of the target negative current is increased considering the configurable value of an equivalent capacitance  $C_{Oeg}$ .

## 4.3.2.3 Keeping ZVS operation for wide output voltage range

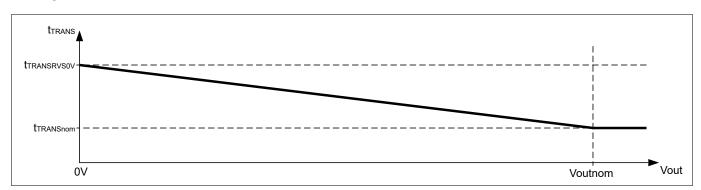

When output voltage Vout is decreasing the demagnetization takes longer. In CRM, ZVS operation is ensured by adjusting the on time of the LS switch  $t_{LSon}$  to match with the changed Vout. In ZV-RVS, the ZVS pulse on-time  $t_{ZVS}$  is calculated from  $I_{MAGneg}$  and Vout and the first LS on-time  $t_{TRANS}$  decreases with increasing Vout (see Figure 17).

Figure 17 Vout compensation for  $t_{TRANS}$  in ZV-RVS mode

# 4.3.2.4 ZVS operation and body-diode cross-conduction prevention during CRM operation

A too short LS on-time can cause hard switching or even body diode cross conduction if the magnetizing current is still positive when LS is turned off. A too long on-time increases the reactive current and conduction losses and can even saturate the transformer. In order to exclude hard switching and body diode cross conduction, the controller activates the HS switch only after the voltage at pin ZCD indicates a changing half-bridge voltage V<sub>HB</sub> (ZCD event). The controller adjusts the LS on-time to always ensure ZVS condition.

## 4.3.2.5 Propagation delay compensation (PDC)

During peak current control a propagation delay is impacting the peak current resulting in higher values. The overshoot depends on the voltage at the input voltage  $V_{bus}$  and reflected output voltage at resonant capacitor  $V_{Cr}$ . This dependency on  $V_{bus}$  and  $V_{Cr}$  impacts the current set-point threshold accuracy seen in the application and is therefore compensated to avoid errors on the feedback signal  $V_{FB}$  and the internal current set point  $V_{SET}$ .

## 4.3.3 Vout start-up control

A hybrid-flyback start-up takes place after the start-up conditions are met, see Chapter 4.1.1. At first several LS pulses are applied to precharge the bootstrap capacitor at HSVCC pin. After that ZV-RVS switching cycles smoothly ramp up the output voltage. Here, the first switching cycles run with a low fixed frequency until the voltage at pin ZCD is high enough for valley switching. The startup-phase is finished once the feedback loop takes over the peak current control.

During the first HS pulse the CS pin is checked for short circuit. For the ZVS pulse duration a maximum applies to prevent too long ZVS pulse due to very low ZCD voltage measurement. A transition from ZV-RVS to CRM may take place during the startup-phase if the voltage sampled at pin ZCD exceeds the related thresholds.

## 4.3.4 Frequency jitter

In order to reduce the EMI noise spectrum a switching frequency jitter is available. The jitter function is working in CRM and in ZV-RVS operation. In CRM-operation the jitter function is only active in case the bus voltage

### **Datasheet**

### 4 Functional description

exceeds the configurable bus voltage threshold V<sub>bus Jitteren</sub>, while in ZV-RVS mode the jitter is enabled once the configurable parameter I<sub>MAGnegiitter</sub> has a non-zero value.

The switching frequency jitter is done by modulating the magnetizing current. In CRM, the modulation of the magnetizing current is done by changing the LS on-time t<sub>LSon</sub>, while in ZV-RVS the ZVS pulse length t<sub>ZVS</sub> is changed.

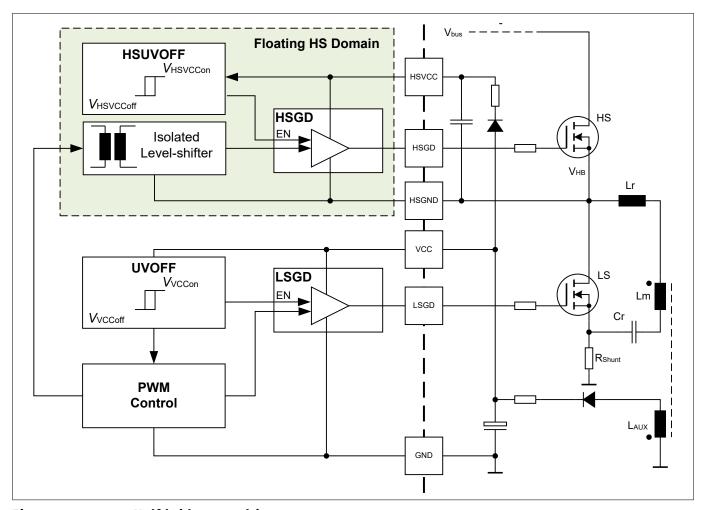

### Half-bridge gate driver 4.3.5

The half-bridge gate driver consists of a low-side gate driver for LS switch, which is supplied by VCC and GND pin. The HS switch is driven by a floating high-side gate driver supplied by HSVCC and HSGND. The floating HS domain is galvanically isolated and steered via a coreless pulse transformer. The LS and HS gate drivers are enabled/disabled based on the corresponding undervoltage lockout thresholds (V<sub>VCCon</sub>, V<sub>VCCoff</sub>) and (V<sub>HSVCCon</sub>, V<sub>HSVCCoff</sub>) (see Chapter 4.5.2.1 and Chapter 4.5.2.2). Both drivers are clamping the maximum gate driver output voltage to V<sub>LSGDhigh</sub>. If disabled the gate driver outputs are actively kept pulled down. When HSVCC exceeds the threshold V<sub>HSVCCon</sub> the high-side gate driver is enabled after a time period of t<sub>HSGDendel</sub>.

Figure 18 Half-bridge gate driver

In order to drive discrete GaN-HEMT devices in the half-bridge, a dedicated external RC-network is recommended, see Figure 3.

For the high voltage level V<sub>LSGDhigh</sub> of the LS gate driver two different values can be set by configuration.

### **Combo-control functions** 4.4

In the following section the combo-controller functions with PFC and Hybrid-flyback controller interaction for an optimum system control are described.

### **Datasheet**

### 4 Functional description

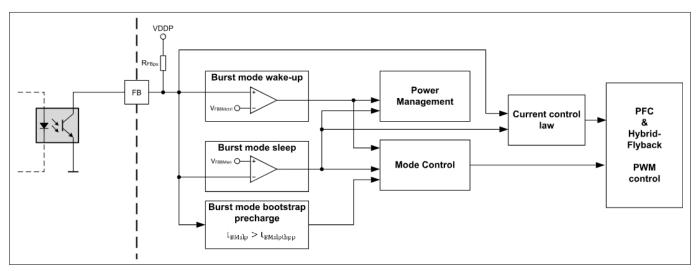

### 4.4.1 **Burst mode control**

The IC contains a burst mode control block to enter a highly efficient operation mode at light-load. By introducing longer non-switching phases with IC entering a sleep mode the average switching and bias losses are reduced during burst mode operation. Both, the PFC stage and the hybrid-flyback, go into burst mode at low load. The burst mode operation is controlled by the hybrid-flyback controller in relation to the output current reflected by the feedback voltage V<sub>FB</sub>. In general, the burst-mode operation of PFC and hybrid-flyback is synchronized. Figure 19 shows the main functions for the burst mode control.

Figure 19 **Burst mode control block**

### 4.4.1.1 **Burst mode entry**

Once V<sub>FB</sub> is dropping below V<sub>FBBMen</sub> the generation of next switching pulse is stopped and burst mode is enabled by entering sleep mode with the reduced current consumption I<sub>VCCBMpsm</sub>. At burst mode entry the HV start-up cell is turned on to charge up VCC until V<sub>VCC on</sub> is reached.

### 4.4.1.2 **Burst mode operation**

The steady state burst mode operation is based on a burst frame on/off control by means of comparing the voltage at FB pin with the feedback thresholds V<sub>FBBMen</sub> and V<sub>FBBMctrl</sub>. The threshold V<sub>FBBMen</sub> determines when the IC enters the sleep phase. During the sleep phase the threshold V<sub>FBBMctrl</sub> is used for for waking up. The burst frame duty cycle and burst frame frequency is fully controlled by means of V<sub>FB</sub>, VCC current consumption is reduced during the sleep phases.

The PFC is enabled and disabled synchronously with the hybrid-flyback. However, depending on the operation conditions, PFC might also be disabled (see Chapter 4.4.2), while the hybrid-flyback is switching.

### 4.4.1.3 **Burst mode bootstrap precharge**

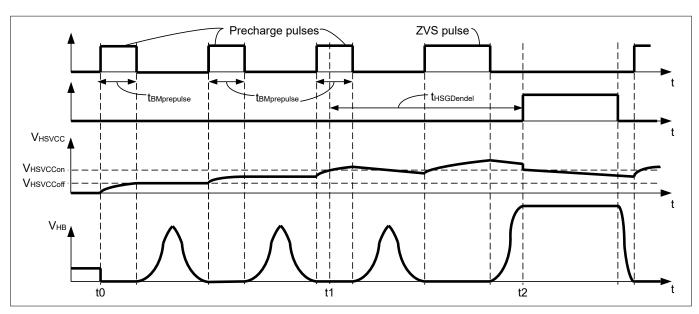

Operation in burst mode at very light-load leads to long sleep phases without switching activities. During this sleep time period the HSVCC voltage may drop below the off-threshold V<sub>HSVCCoff</sub> and deactivate the floating HS gate driver. To ensure that a proper HSVCC supply is in place for turning on the HS switch after a long IC sleep phase, a train of N<sub>BMprepulse</sub> precharge pulses is introduced before the first ZV-RVS switching cycle. The precharge pulse train is only introduced when the captured burst mode sleep time has exceeded the threshold t<sub>BMslpthrpp</sub>. Figure 20 shows a precharge pulse train pattern for the case N<sub>BMprepulse</sub>=3.

Note: If a HS pulse is missing due to improper HSVCC supply, the subsequent LS pulse may lead to hard switching. Therefore, the controller tries to detect this case and may stop the switching operation.

### **Datasheet**

# fineor

### 4 Functional description

Figure 20 Precharge pulse train pattern

### 4.4.1.4 **Burst mode exit**

Burst mode exit is a smooth transition from on/off control back to the closed feedback control loop at load increase, no matter if the load jumps or increases slowly. In these cases the controller it will wake-up (in case it was not active yet) and starts switching. Since the load and the voltage at pin FB are high, the controller is not going to sleep anymore but changes to normal operation. This smooth transition is possible as in regular burst mode active phase regular peak current control based on the feedback control applies.

### 4.4.2 PFC enable/disable control

The PFC stage is enabled and active, when the load is above a certain level where power factor correction could be mandatory or the hybrid-flyback stage requires a minimum input voltage level for proper operation.

Whether the load requires PFC operation is decided by a hysteretic comparator with two thresholds P<sub>PFCenable</sub> and P<sub>PFCdisable</sub>. However, the PFC may be enabled although the estimated power is below P<sub>PFCdisable</sub> to ensure proper hybrid-flyback operation. Whether the hybrid-flyback stage requires PFC operation is decided by a hysteretic comparator evaluating the AC line peak voltage with two thresholds derived from the sensed output voltage.

For the power-based disabling of the PFC with the estimated power going below P<sub>PFCdisable</sub> a configurable blanking time t<sub>PFCblkdisable</sub> applies.

### Variable bus voltage target level 4.4.3

Compared to conventional PFC boost operation, the PFC bus voltage is not regulated to a fixed target value but the target voltage depends on the operation conditions and is set either by the hybrid-flyback stage or by the PFC itself. This functionality is closely related to the PFC enable/disable control (see Chapter 4.4.2).

For optimum operation of the hybrid-flyback stage over a wide output voltage range, the PFC bus voltage target level V<sub>bustarget,HFB</sub> requested by the hybrid-flyback stage is determined by the controller depending on the reflected output voltage  $N \cdot V_{out}$ , which is determined from the voltage at pin ZCD.

A proper PFC operation is only possible in case the target bus voltage target level is somewhat above the given AC line peak voltage |V<sub>ACpk</sub>|. For that reason the PFC controller also determines a bus voltage target level V<sub>bustarget,PFC</sub> which is the detected rectified AC peak voltage plus an offset V<sub>bustargetVacpkoffset</sub>.

Whenever PFC is enabled and switching the higher value of V<sub>bustarget,HFB</sub> and V<sub>bustarget,PFC</sub> is used as target value for the PFC regulation.

Furthermore, the bus voltage target value is limited to a minimum value V<sub>bustargetmin</sub> as well as to a maximum value V<sub>bustargetmax</sub>.

### 4 Functional description

### 4.5 Protections

The IC supports several protection functions resulting in different protection reactions.

For most protection events the IC enters a protection mode (see Chapter 4.5.1). In many cases the protection mode is configurable.

Table 2 Protection Features and Reaction

| <b>Protection Feature</b>               | Symbol    | <b>Protection Reaction</b>                                                      |

|-----------------------------------------|-----------|---------------------------------------------------------------------------------|

| VCC undervoltage lockout                | UVOFF     | HW reset and restart                                                            |

| HSVCC undervoltage lockout              | HSUVOFF   | Disable HS gate driver                                                          |

| VCC overvoltage protection              | VCCOVP    | Configurable: Auto-restart or latch                                             |

| Brown-in protection                     | BIP       | Bang-bang mode, waiting for brown-in in start-<br>up check phase                |

| Brown-out protection                    | ВОР       | Stop operation and enter fast restart mode                                      |

| PFC Start-up timeout protection         | PFCSTTOP  | Configurable: Auto-restart or latch                                             |

| Output start-up timeout protection      | VoutSTTOP | Configurable: Auto-restart or latch                                             |

| AC overvoltage protection               | ACOVP     | Configurable: Auto-restart or latch                                             |

| PFC bus overvoltage protection level 1  | PFCOVP1   | Stop PFC switching                                                              |

| PFC bus overvoltage protection level 2  | PFCOVP2   | Stop PFC switching (cycle-by-cycle)                                             |

| PFC bus undervoltage protection         | PFCUVP    | Configurable: Auto-restart, latch or stop operation and enter fast restart mode |

| PFC overcurrent protection              | PFCOCP    | Stop PFC switching (cycle-by-cycle)                                             |

| PFC CCM protection                      | PFCCCM    | Configurable: Auto-restart or latch                                             |

| Output overcurrent protection level 1   | OCPlev1   | Configurable: Auto-restart or latch                                             |

| Output overcurrent protection level 2   | OCPlev2   | Configurable: Auto-restart or latch                                             |

| Output maximum current protection       | OCPmax    | Configurable: Auto-restart or latch                                             |

| HFB primary side overcurrent protection | CSPROT    | Configurable: Auto-restart or latch                                             |

| Vout overvoltage protection             | VoutOVP   | Configurable: Auto-restart or latch                                             |

| Vout undervoltage protection            | VoutUVP   | Configurable: Auto-restart or latch                                             |

| Vout short circuit protection           | VoutSCP   | Configurable: Auto-restart or latch                                             |

| CS pin short protection                 | CSSCP     | Configurable: Auto-restart or latch                                             |

| FB pin start-up protection              | FBSTUP    | Stop operation and enter bang-bang mode for start-up check phase                |

| HFB open loop protection                | HFBOLP    | Configurable: Auto-restart or latch                                             |

| External overtemperature protection     | extOTP    | Configurable: Auto-restart or latch                                             |

| Watchdog timer                          | WDOG      | Configurable: Auto-restart or latch                                             |

| Memory parity check                     | MEMPAR    | Configurable: Auto-restart or latch                                             |

|                                         | -         |                                                                                 |

### 4.5.1 Protection modes

Once the protection mode is entered, the IC stops the gate driver switching at the PFCGD, LSGD and HSGD pins and enters stand-by mode. During stand-by mode, the HV start-up cell is operating in the bang-bang mode (see

### **Datasheet**

# infineon

### 4 Functional description

Chapter 4.1.3) to keep the VCC voltage at a high level to have enough energy stored in the VCC capacitor for the system start-up. Three protections modes are supported as described in the sequel.

### 4.5.1.1 Deactivate IC after undervoltage lockout

In case VCC drops below  $V_{VCCoff}$  the undervoltage lockout protection is triggered, the IC is completely deactivated and is only restarted with the regular start-up mechanism, see Chapter 4.1.1.

### 4.5.1.2 Auto-restart mode

When auto-restart mode is activated, the controller stops switching at the gate driver pins. After a configurable auto restart time  $t_{ARM}$ , the control IC resumes its operation. During the auto restart time  $t_{ARM}$  the controller wakes up very  $t_{ARMbase}$  in order to re-charge VCC to  $V_{VCCon}$  (see Chapter 4.1.3).

### 4.5.1.3 Latch mode

In latched operation the system stays in stand-by mode without any restart attempt. The latched operation can only be reset by VCC dropping below the UVOFF HW reset threshold  $V_{VCCoff}$ . In latch mode operation, the HV start-up cell is turned on at VCC pin voltage threshold  $V_{VCCoff}$  and turned off when reaching VCC pin voltage threshold  $V_{VCCoff}$  (see Chapter 4.1.3).

### 4.5.1.4 Fast restart mode

In fast restart mode operation the IC enters bang-bang during brown-in phase (see Chapter 4.1.2). After entering the sleep mode the HV start-up cell turns on and charges up the VCC voltage until the threshold  $V_{VCCon}$ . Then the IC is activated again for restart.

### 4.5.2 Protection features

## 4.5.2.1 VCC undervoltage lockout

The implemented VCC undervoltage lockout (UVOFF) ensures a defined activation and deactivation of the IC operation depending on the supply voltage at pin VCC. The UVOFF contains a hysteresis with the upper voltage threshold  $V_{VCCon}$  for activating the IC. A VCC voltage level dropping below the bottom threshold  $V_{VCCoff}$  resets and deactivates the IC during normal operation. In reset state the HV start-up cell is turned on, starting the next VCC charge cycle until VCC voltage exceeds  $V_{VCCon}$  (see Chapter 4.1.1).

## 4.5.2.2 HSVCC undervoltage lockout

The implemented HSVCC undervoltage lockout (UVOFF) ensures a defined activation and deactivation of the floating high-side driver. The HSUVOFF contains a hysteresis with the upper voltage threshold V<sub>HSVCCon</sub> for activating the high-side gate driver. A HSVCC voltage level dropping below the bottom threshold V<sub>HSVCCoff</sub> turns off and deactivates immediately the high-side driver. During deactivation phase the high-side driver current consumption is reduced.

## 4.5.2.3 VCC overvoltage protection

There is an over voltage detection at pin VCC. The detection function consists of a threshold  $V_{VCCOVP}$  and a blanking time of  $t_{VCCOVP}$ . The protection reaction once the overvoltage protection is triggered can be configured.

### 4.5.2.4 Brown-in protection

For successful brown-in two conditions must be fulfilled:

- 1. Input voltage above threshold with  $V_{in} > V_{inbi}$  sensed via pin HV

- 2. PFC bus voltage above threshold with V<sub>bus</sub> > V<sub>busbi</sub> sensed via pin PFCVS

When AC brown-in condition is not met before the timeout duration  $t_{HVbito}$  is expired, the AC brown-in time out protection reaction is triggered.

### **Datasheet**

# infineon

### 4 Functional description

Since the brown-in is also based on the sensed bus voltage, this protection also acts as PFC open-loop protection during start-up.

### 4.5.2.5 Brown-out protection

Brown-out detection is based on AC peak voltage estimation: In case the PFC is disabled, the AC peak voltage is determined from the bus voltage  $V_{bus}$  sensed at pin PFCVS. In case the PFC is enabled the AC peak voltage is determined using the captured PFC switching cycle timings. If the estimated AC peak voltage is below the configurable threshold  $V_{inbo}$  for longer than the blanking time  $t_{bo}$ , the protection mode will be triggered and the IC enters brown-in detection phase. Please be aware, that the blanking time is only counted during active time, so that during burst-mode with sleep phases the duration to detect a brown-out is increased.

Afterwards, as described in Chapter 4.1.2, bang-bang mode is entered for an fast re-start in case AC input voltage comes back.

## 4.5.2.6 Start-up timeout protections

After the PFC is activated, the PFC performs a soft-start. In case the softstart cannot be completed within  $t_{\text{startPFC}}$ , the configured protection mode (auto-restart or latch) is entered.

A second start-up timeout function is implemented for the hybrid-flyback output. In case of overload during start-up the output voltage  $V_{out}$  may not reach the regulation target voltage, preventing the system from entering regulation. A timeout is detected if the current set-point determined by  $V_{FB}$  is not dropping below the current set-point determined by  $V_{out}$  start-up control within the maximum time period  $t_{startto}$ .

## 4.5.2.7 PFC bus overvoltage protection

The first overvoltage protection (PFCOVP1) threshold is given by the configurable parameter  $V_{PFCVSovp1}$ . Latest within  $t_{SLWTASK}$  after this threshold is exceeded, the PFC stops switching. The hybrid-flyback stage continues switching. The PFC resumes operation when the measured voltage falls below the threshold  $V_{PFCVSovp1res}$ .

A second overvoltage protection mechanism (PFCOVP2) is implemented using an hardware comparator. It protects the system in case the bus voltage increases above the first OVP threshold in very short time without triggering PFCOVP1. The corresponding threshold  $V_{PFCVSovp2}$  is a fixed voltage. In case the voltage sensed at PFCVS exceeds the threshold, no new PFC gate driver pulse is generated. As soon as the voltage at PFCVS is below the threshold  $V_{PFCVSovp2}$  again, PFC pulses are generated again.

Neither in case of OVP1 nor in case of OVP2 a protection mode is entered. Hybrid-flyback switching remains unaffected.

## 4.5.2.8 AC overvoltage protection

The AC overvoltage protection (ACOVP) is also based on the bus voltage measured at PFCVS via external voltage divider. Compared to the bus overvoltage protections OVP1 and OVP2, which only stop PFC from switching (see Chapter 4.5.2.7), the ACOVP stops PFC and hybrid-flyback operation and enters protection mode. In case of AC overvoltage, the PFC stops switching due to OVP2, the bus voltage and thus the voltage at pin PFCVS represent the AC peak. In case the voltage measured at PFCVS is greater than the threshold  $V_{\text{PFCVSacovp}}$  for longer than the configurable blanking time  $t_{\text{ACovp}}$  the configured protection mode (auto-restart or latch) is entered.

ACOVP can be enabled or disabled by configuration using parameter EN<sub>ACOVD</sub>.

## 4.5.2.9 PFC bus undervoltage protection

Undervoltage detection of the PFC bus voltage is sensed at the PFCVS pin and acts as protection mechanism for the hybrid-flyback stage.

The bus voltage undervoltage protection compares the bus voltage with the voltage  $V_{busUVP}$  every  $t_{sample}$  whereas the value of  $V_{busUVP}$  is set to the minimum of  $V_{CrUVPoffset} + V_{Cr,avg}$  and  $1.5 \cdot V_{Cr,avg}$ . The undervoltage protection is blanked with the configurable blanking time  $t_{busUVP}$  and is sampled with a time period  $t_{sample}$ .

Once the protection is triggered, the configured protection mode (latch, auto-restart or fast restart mode) is entered. It is possible to choose different reactions for the protection being triggered during start-up and normal operation.

### **Datasheet**

### 4.5.2.10 PFC overcurrent protection

Once the voltage at pin PFCCS exceeds the overcurrent threshold  $V_{PFCCSocp}$  for longer than the blanking time  $t_{PFCCSocp}$  the PFC gate PFCGD is turned off. Afterwards, the ZCD signal or the PFC maximum period timeout signal initializes the next switching cycle. This protection mechanism is active in every switching cycle.

## 4.5.2.11 PFC CCM cycle protection

During CCM operation, the magnetizing current in the PFC choke does not decay to zero prior to switch turn on. Quasi-resonant oscillation is missing in the  $V_{PFCCS}$  signal before the maximum switching period timeout is reached that turns the transistor on. This turn-on event without ZCD oscillation is monitored to protect the PFC converter from continuous CCM operation. If the ZCD signal is missing for longer than the blanking time  $t_{PFCCSccm}$  the protection is triggered and the configured protection mode (auto-restart or latch) is entered.

## 4.5.2.12 Hybrid-flyback overcurrent protection

The hybrid-flyback overcurrent protection contains several detection functions, which protect the application when operating under output overcurrent conditions or when exceeding a primary side peak current (see Figure 21).

Figure 21 Overcurrent protection overview

## 4.5.2.12.1 Output overcurrent protection

The output overcurrent protection is implemented as a three level protection:

- Output overcurrent protection level 1

- Output overcurrent protection level 2

- Output maximum current protection

using different overcurrent level thresholds I<sub>SETOCPlev1/lev2/max</sub> and blanking times t<sub>OCPlev1bl/lev2bl/maxbl</sub>.

### **Datasheet**

### 4 Functional description

The output overcurrent protection levels I<sub>SETOCPlev1/lev2/max</sub> are defined by the output current control law, whereas I<sub>SETOCPmax</sub> corresponds to the maximum output current level. Once the current set-point I<sub>SET</sub> crosses the threshold levels a timer is started. The configured protection mode (auto-restart or latch) is entered when the timer reaches the thresholds t<sub>OCPlev1bl/lev2bl/maxbl</sub>. The timer is reset when I<sub>SET</sub> is dropping back below the thresholds.

Be aware, that once a higher output current corresponding to a current set point  $I_{SET} > I_{SETOCPmax}$  is requested via V<sub>FB</sub> control, the output current is kept limited. During this phase the output voltage is dropping because output current is higher than what is provided by the converter.

### Primary side overcurrent protection CSPROT 4.5.2.12.2

V<sub>CSPROT</sub> is a fixed threshold at CS pin and beyond the maximum operating range V<sub>CSTHRmax</sub>. The CSPROT function is not blanked during the leading edge blanking time t<sub>HSleb</sub>. Once exceeded the configured protection mode (auto-restart or latch) is entered.

In order to avoid false CSPROT events configurable blanking times t<sub>CSPROTfilstart</sub> and t<sub>CSPROTfil</sub> apply.

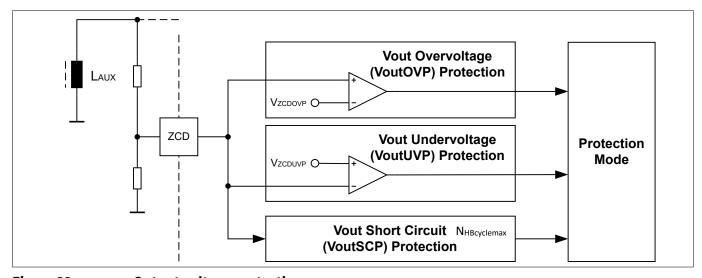

### **Output voltage protection** 4.5.2.13

The IC provides two output voltage Vout protection mechanisms for output undervoltage and output overvoltage to ensure a reliable operation within a defined Vout operating range. The measurement is done at pin ZCD via the reflected voltage at the auxiliary winding of the transformer during the demagnetization phase when the LS switch is turned on (see Figure 22). Furthermore the zero-crossing detection during start-up phase is observed to detect short circuit conditions at the output.

Figure 22 **Output voltage protections**

### 4.5.2.13.1 Vout overvoltage protection

The IC provides primary side output overvoltage detection via the voltage measured every switching cycle during the LS on-time at the ZCD-pin from the auxiliary transformer winding. Output overvoltage is detected when the reflected output voltage is exceeding the threshold V<sub>ZCDOVP</sub> (corresponding to the configurable threshold V<sub>outOVP</sub>) longer than the configurable blanking time t<sub>outOVPbl</sub>. Once detected a protection mode is immediately triggered and the configured protection mode (auto-restart or latch) is entered.

### 4.5.2.13.2 **Vout undervoltage protection**

Output undervoltage detection is detected via the voltage measured at the ZCD-pin. After the start-up is finished Vout undervoltage can triggered when the voltage measured at pin ZCD is dropping below the threshold V<sub>ZCDUVP</sub>, which corresponds to the configurable threshold V<sub>outUVP</sub>. Once detected the configured protection mode (auto-restart or latch) is entered.

### **Datasheet**

### 4 Functional description

In burst-mode operation, after wake-up from sleep, the voltage measured at pin ZCD might be distorted due to various reasons. In order to avoid mis-triggering the output undervoltage protection the detection can be blanked. The blanking time can be configured using the parameter Configuration

### **Vout short circuit protection** 4.5.2.13.3

For a short circuit protection at the output, two different mechanisms are implemented. One is only active during start-up, the other one is meant for protection during active operation.

During start-up, the Vout short circuit protection limits the number of half-bridge switching cycles. After a startup request only a maximum of N<sub>HBcyclemax</sub> consecutive half-bridge switching cycles without zero-crossing detection are allowed. If N<sub>HBcyclemax</sub> is exceeded, the (re-)start phase is stopped and the configured protection mode (prematurely auto-restart mode sleeping phase or latch) is entered.

During operation another Vout short circuit protection mechanism is active using two criteria. If the difference between the actual voltage V<sub>ZCD</sub> and its internally averaged value V<sub>ZCDavg</sub> is bigger than the internal threshold ΔV<sub>ZCDshort</sub>, an output short circuit protection is triggered and the configured protection mode (auto-restart or latch) is entered.

### CS pin short circuit protection 4.5.2.14

During Vout start-up a short circuit detection at CS pin is activated for the very first HS switch pulse to protect the application operating with a shortened R<sub>Shunt</sub>.

### 4.5.2.15 FB pin start-up protection

During the start-up check phase, the voltage at pin FB is evaluated for error. The system will only start up in case V<sub>FB</sub> > V<sub>FBBMctrl</sub>. In case the system cannot be started due to too low voltage at pin FB the configured protection event with parameter EV<sub>StartFBlow</sub> will be triggered.

### Hybrid-flyback open loop protection 4.5.2.16

The open control loop protection is using a similar method as the output short protection (see Chapter 4.5.2.13.3). Only in case of a saturated feedback voltage at FB, the reflected output voltage measured via ZCD pin is evaluated: If the difference between the actual voltage  $V_{7CD}$  and its internally averaged value  $V_{7CDavg}$  is bigger than the internal threshold  $\Delta V_{7CDolp}$ , which is related to the configurable output voltage threshold  $\Delta V_{outolp}$ , an open loop protection is triggered and the configured protection mode (auto-restart or latch) is entered.

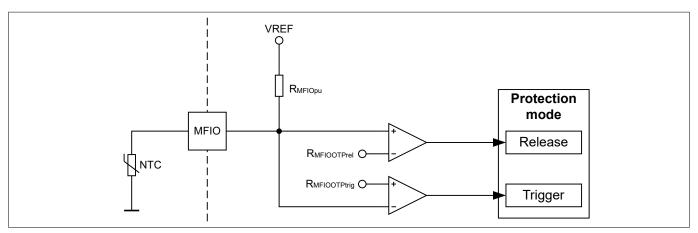

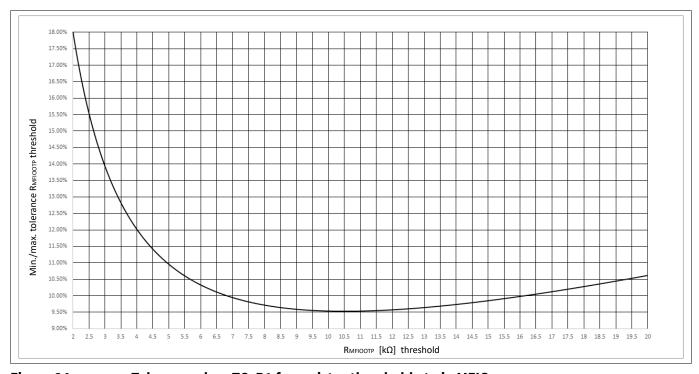

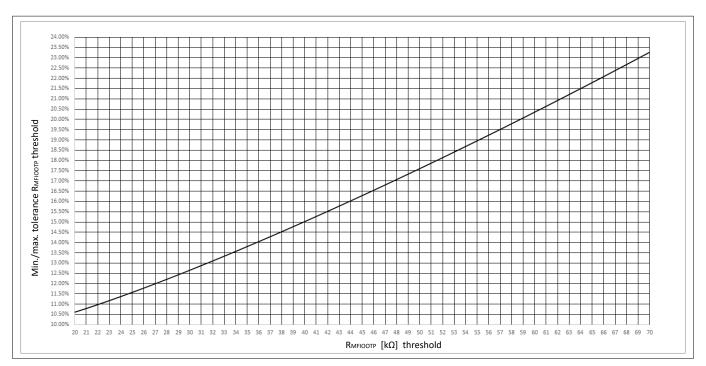

### **External overtemperature protection** 4.5.2.17