# Automotive front light LED reference design with SEPIC topology

#### **Design overview**

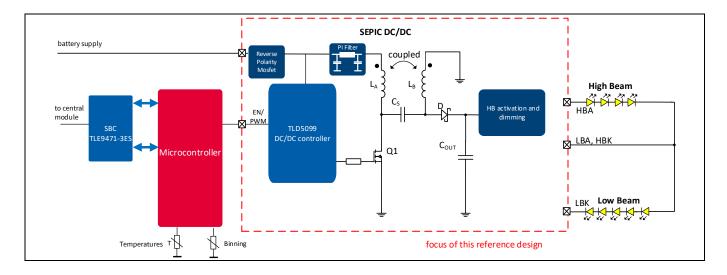

This Infineon reference design guide describes a detailed implementation of an automotive front light high beam/low beam combination using the flexible multi-topology DC-DC controller TLD5099EP of the LITIX<sup>™</sup> Power family in current controlled buck-boost SEPIC configuration. One single DC-DC channel is used to drive the high beam and low beam. The high beam can be activated in conjunction with the low beam or the low beam can be activated standalone. This represents a cost saving approach especially suitable for entry level LED headlamps. A PWM dimming feature enables furthermore control of brightness and enables derating in extreme operating conditions. State of the art diagnosis is provided as well as transient robustness. Compliant EMC performance is verified according to the CISPR25 standard. Thermal performance information is given and discussed.

#### **Highlighted components**

- TLD5099EP Multi-topology DC-DC controller from the LITIX™ Power family

- IPD60N10S4L OptiMOS<sup>™</sup> -T2 as power stage switching MOSFET

- IPD50P04P4L-11 OptiMOS™ -P2 as reverse battery protection MOSFET

#### **Applications**

- Automotive front light

- High beam, low beam

- Daytime running light, turn indicator

- Motorcycle headlamp

#### **Highlighted design aspects**

EMC tested

Cost optimized

Space saving

Transient pulse tested

#### **Block diagram**

# Automotive front light LED reference design with SEPIC topology

#### **Table of contents**

# **Table of contents**

| Table   | of contents                                         | 2   |

|---------|-----------------------------------------------------|-----|

| Impo    | rtant Notice                                        | 4   |

| 1       | System description                                  | 5   |

| 1.1     | Design specifications                               |     |

| 2       | System design                                       | 7   |

| 2.1     | TLD5099EP constant current controller               |     |

| 2.1.1   | Power supply                                        |     |

| 2.1.2   | Switching frequency & spread spectrum               | .10 |

| 2.1.3   | Output current configuration                        | .11 |

| 2.1.4   | Switch current sense                                | .13 |

| 2.1.5   | PWM dimming                                         | .13 |

| 2.1.5.  | 1 External PWM dimming                              | .13 |

| 2.1.5.2 | 2 Embedded PWM dimming                              | .14 |

| 2.1.6   | Compensation network                                | .14 |

| 2.1.7   | Overvoltage protection                              | .15 |

| 2.2     | SEPIC power stage and input filter                  | .16 |

| 2.2.1   | Passive components                                  | .17 |

| 2.2.2   | Switching MOSFET                                    | .22 |

| 2.2.2.  | 1 Switching losses                                  | .22 |

| 2.2.2.2 | 2 Conduction losses                                 | .27 |

| 2.2.2.3 | 3 Simulated losses                                  | .28 |

| 2.2.2.4 | 4 Thermal considerations                            | .30 |

| 2.2.3   | Switching diode                                     | .31 |

| 2.2.4   | Input filter                                        |     |

| 2.3     | High beam activation, PWM dimming and output filter | .33 |

| 2.4     | Reverse polarity and input protection               |     |

| 2.4.1   | Ceramic transient voltage suppressor                |     |

| 2.4.2   | Reverse polarity protection                         |     |

| 2.5     | Layout considerations                               |     |

| 2.5.1   | Layer stackup                                       |     |

| 2.5.2   | General recommendations                             |     |

| 2.5.3   | Power stage and input filter                        |     |

| 2.5.4   | TLD5099EP                                           | .43 |

| 3       | System performance                                  |     |

| 3.1     | General operating characteristics                   |     |

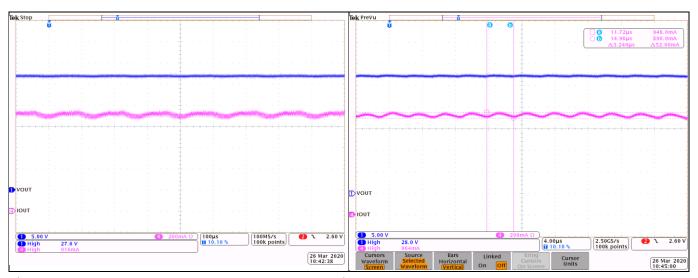

| 3.1.1   | Output voltage and current                          |     |

| 3.1.2   | Switching node                                      |     |

| 3.1.3   | PWM dimming                                         |     |

| 3.1.4   | High beam activation                                |     |

| 3.2     | Transient immunity                                  |     |

| 3.2.1   | Jump start                                          |     |

| 3.2.2   | Load dump                                           |     |

| 3.2.3   | Start pulses                                        |     |

| 3.2.3.  |                                                     |     |

| 3.2.3.2 |                                                     |     |

| 3.2.4   | Reverse polarity                                    |     |

| 3.3     | Electromagnetic compatibility                       | .54 |

### Table of contents

| Revis | sion history                          | 69 |

|-------|---------------------------------------|----|

| 5     | Reference documents                   | 68 |

| 4     | Abbreviations and definitions         | 67 |

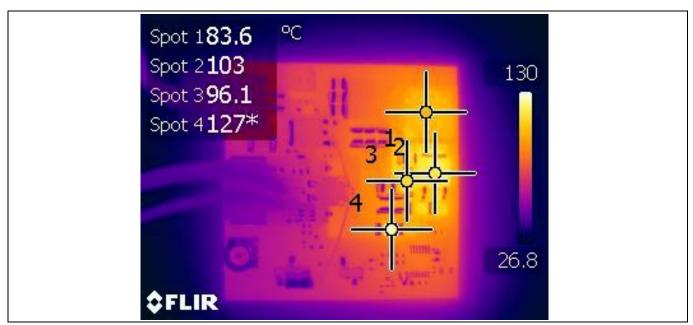

| 3.5   | Thermal performance                   | 66 |

| 3.4.1 | · · · · · · · · · · · · · · · · · · · |    |

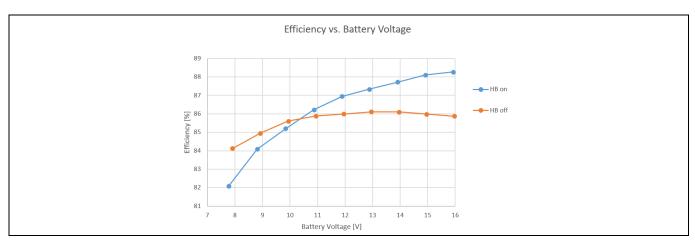

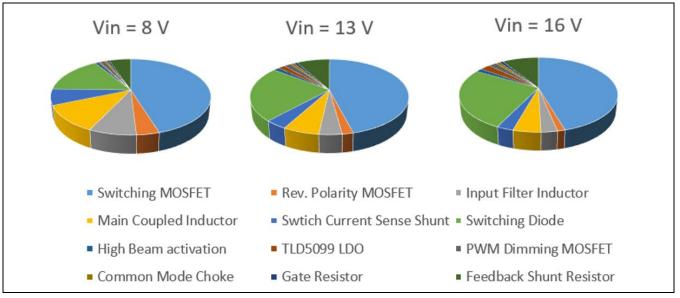

| 3.4   | Efficiency                            | 60 |

| 3.3.3 | Summary and discussion                | 59 |

| 3.3.2 |                                       |    |

| 3.3.1 | Conducted emissions                   | 54 |

#### Automotive front light LED reference design with SEPIC topology

# **Important Notice**

The Evaluation Boards and Reference Boards and the information in this document are solely intended to support designers of applications to evaluate the use of products of Infineon Technologies in the intended application.

Environmental conditions have been considered in the design of the Evaluation Boards and Reference Boards provided by Infineon Technologies. The design of the Evaluation Boards and Reference Boards is **tested by** Infineon Technologies only as described in this document. The design is not qualified in terms of safety requirements, manufacturing and operation over the entire operating temperature range or lifetime.

The Evaluation Boards and Reference Boards provided by Infineon Technologies are **subject to functional testing only under typical load conditions**. Evaluation Boards and Reference Boards are not subject to the same procedures as regular products regarding returned material analysis (RMA), process change notification (PCN) and product discontinuation (PD).

Evaluation Boards and Reference Boards are not commercialized products and are **solely intended to be used for evaluation and testing purposes**. They shall in particular not be used for reliability testing or production. Hence, the Evaluation Boards and Reference Boards may not comply with CE or similar standards (including but not limited to the EMC Directive 2004/EC/108 and the EMC Act) and may not fulfill other requirements of the country in which they are operated by the customer. The customer shall ensure that each Evaluation Boards and Reference Board will be handled in a way which is compliant with all relevant requirements and standards in the country in which they are operated.

The Evaluation Boards and Reference Boards and any information in this document are addressed **only to qualified and skilled technical staff, for laboratory usage,** and shall be used and managed according to the terms and conditions set forth in this document and in any other related documentation provided with the respective Evaluation Boards or Reference Board.

It is the **responsibility of customer's technical departments to evaluate the suitability** of the Evaluation Boards and Reference Boards for the intended application and the completeness and correctness of the information provided in this document with respect to such application.

The customer accepts that the Evaluation Boards and Reference Boards are not intended to be used for life-endangering applications such as medical, nuclear, military, life-critical or other applications, where failure of the Evaluation Boards and Reference Boards or any results from the use thereof can reasonably be expected to result in personal injury.

The Evaluation Boards and Reference Boards and any information in this document is provided "as is" and Infineon Technologies disclaims any and all warranties, express or implied, including but not limited to warranties of non-infringement of third party rights and implied warranties of fitness for any purpose, or for merchantability.

Infineon Technologies shall not be responsible for any damages resulting from the use of the Evaluation Boards and Reference Boards and/or from any information provided in this document. The customer is obliged to defend, indemnify and hold harmless Infineon Technologies from and against any claims or damages arising out of or resulting from any use thereof.

Infineon Technologies reserves the right to change this document and/or any information provided herein at any time without further notice.

#### Automotive front light LED reference design with SEPIC topology

**System description**

# 1 System description

This reference design describes a solution for the illumination light functions of an automotive LED headlamp with 25 W to 30 W (depending on the cooling effort) output power. It is considered that this design can be scaled to the needs of a motorcycle headlamp where the output power is typically lower than 25 W to 30 W. For front light LED designs neither the number of LEDs per light function nor the current per LED is standardized but typically the required output power is higher than for exterior rear lighting. Typically, DC-DCs are used as drivers for front light systems to keep the power losses within an acceptable range and to allow the output voltage to be higher than the battery supply. The TLD5099EP design, being a DC-DC boost controller that supports boost and buck-boost topologies was used for this design.

Traditional car headlamp LED designs for high-beam + low-beam consider a maximum power higher than 30 W, however, today this feature is unnecessary to fulfill the requirements for the light output of an LED headlamp. The key is to use highly efficient automotive LEDs with sufficient cooling that enables front light designs with a reduced number of LEDs.

State of the art LEDs that are available on the market today offer highly luminous flux values with >100 lm/W under real application conditions.

Two examples for LEDs for HB/LB are: Nichia NCSW170D and OSRAM Black Flat S where a typical luminous flux of >300 lm at  $I_F$ =1000 mA is expected. Using highly efficient LEDs in combination with a direct topology DC-DC such as TLD5099EP a compact design with few external components and low power losses can be achieved. In the following sections the system design for TLD5099EP with coupled coil and a shorting switch for high-beam and low-beam is described. A heatsink (metal ECU) that would significantly improve the heat conduction was not considered as this is specific for each ECU design and all measurements were done with 5 LEDs for low beam and 4 LEDs for high beam.

# 1.1 Design specifications

Table 1 Design specifications

| Parameter            | Symbol                  |                                          | Values |                                       | Unit | Comment                                                    |  |  |

|----------------------|-------------------------|------------------------------------------|--------|---------------------------------------|------|------------------------------------------------------------|--|--|

|                      |                         | Min.                                     | Тур.   | Max.                                  |      |                                                            |  |  |

| System parameter     | Min.   Typ.   Max.      |                                          |        |                                       |      |                                                            |  |  |

| Input voltage        | $V_{IN}$                | 8                                        | 13.5   | 16                                    | V    |                                                            |  |  |

|                      | $V_{ m IN,Tran}$        | 4.5                                      |        | 35                                    | ٧    | Min. value due to cranking,<br>max. value due to load dump |  |  |

|                      | $V_{	extsf{F,LED}}$     | 2.75                                     | 3      | 3.4                                   | ٧    | LED: OSRAM OSLON® Compact<br>PL KW CELNM1.TG               |  |  |

| voltage of binning   | $V_{	extsf{F,LED,BIN}}$ | 2.75                                     |        | 3.00                                  | V    | LED forward voltage of specific<br>binning class (15)      |  |  |

| Output voltage       | V <sub>OUT</sub>        | 5 x V <sub>F,LED,BIN,min</sub> = 13.75 V |        | 9 x V <sub>F,LED,BIN,max</sub> = 27 V | V    | LB active: 5 x LED<br>LB and HB active: 9 x LED            |  |  |

| LED current          | / <sub>LED</sub>        |                                          | 900    |                                       | mA   | Regulated                                                  |  |  |

| LED current ripple   | $\Delta I_{LED}$        |                                          |        | 200                                   | mA   | Peak to peak current ripple in LED string                  |  |  |

| -                    | $V_{RP}$                |                                          |        | -14                                   | V    | Input voltage in reverse polarity situation                |  |  |

|                      | f <sub>SW</sub>         |                                          | 310    |                                       | kHz  | Switching frequency of the<br>SEPIC power stage            |  |  |

| Dimming<br>frequency | f <sub>DIM</sub>        |                                          | 500    |                                       | Hz   | PWM dimming frequency                                      |  |  |

# Automotive front light LED reference design with SEPIC topology

# System description

| Parameter             | Symbol         |           | Values |                | Unit    | Comment                      |

|-----------------------|----------------|-----------|--------|----------------|---------|------------------------------|

|                       |                | Min. Typ. |        | Max.           |         |                              |

| Thermal               | ·              |           |        |                |         |                              |

| Operating temperature | T <sub>A</sub> | -40       | 25     | 105            | °C      | Derating needs to be applied |

| Transient immun       | ity            |           |        |                |         |                              |

| Jumpstart             |                |           |        | Functional cl  | ass A   |                              |

| Load dump             |                |           |        | Functional cl  | ass A   |                              |

| Start pulses          |                |           |        | Functional cla | ss B/C  | Cold and hot pulses          |

| Reverse polarity      |                |           |        | Functional cl  | ass C   |                              |

| Electromagnetic       | compatibility  |           |        |                |         |                              |

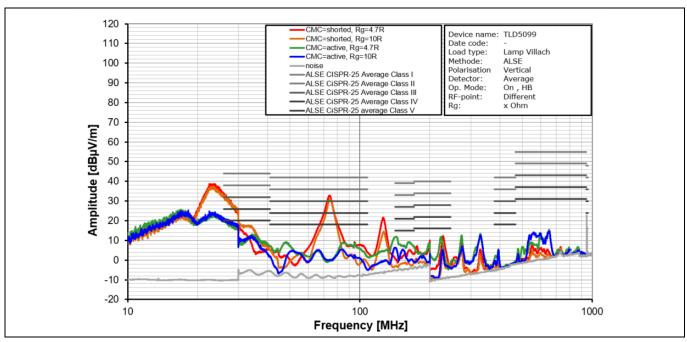

| Conducted emissi      | ons            |           |        | Class V to Cla | ıss III | CISPR25, 150 kHz - 108 MHz   |

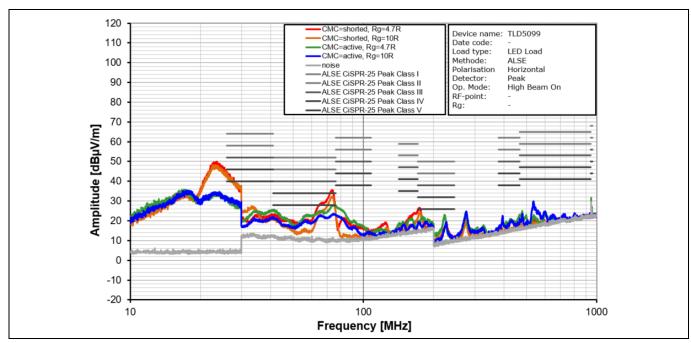

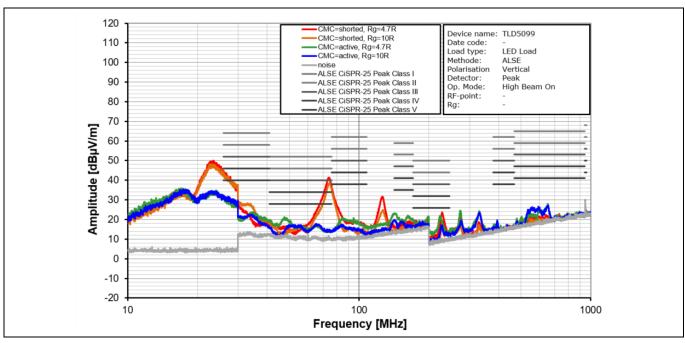

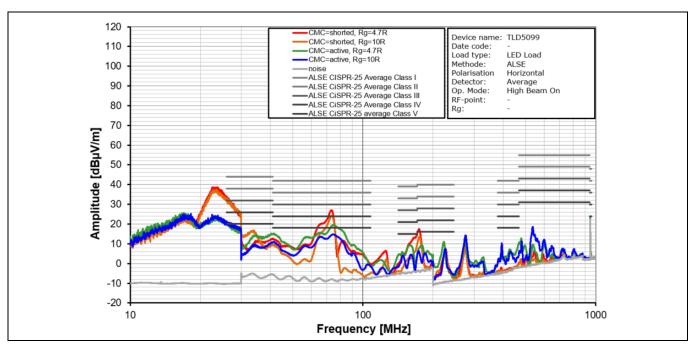

| Radiated emission     | ıs             |           |        | Class V        |         | CISPR25, 30 MHz - 1 GHz      |

#### Automotive front light LED reference design with SEPIC topology

System design

# 2 System design

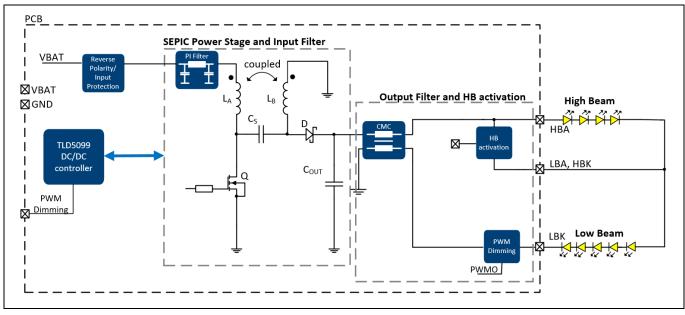

The system design follows the design specifications and can be divided in four main subsystem which are:

- TLD5099EP multi-topology DC-DC controller

- SEPIC power stage and input filter

- HB activation, PWM dimming and output filter

- Reverse polarity and input protection

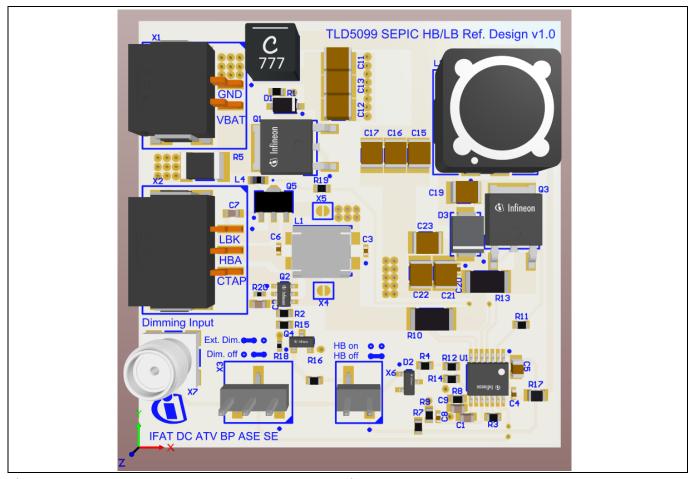

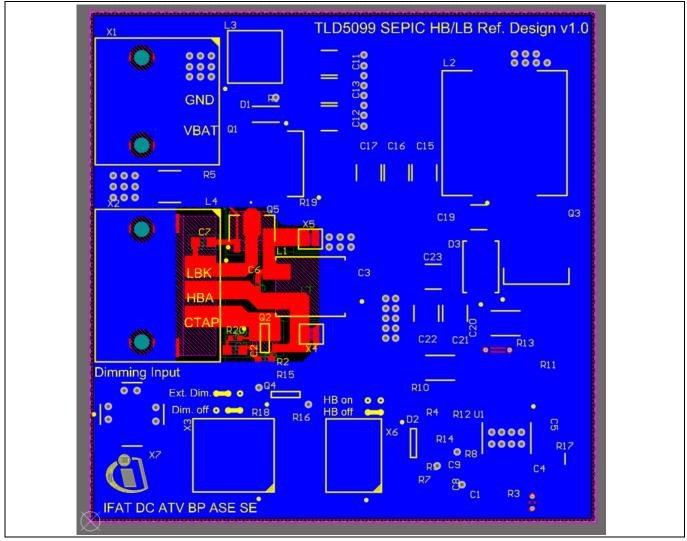

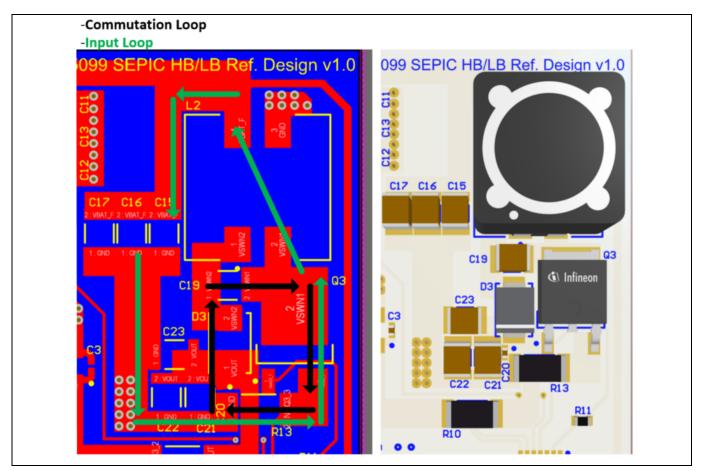

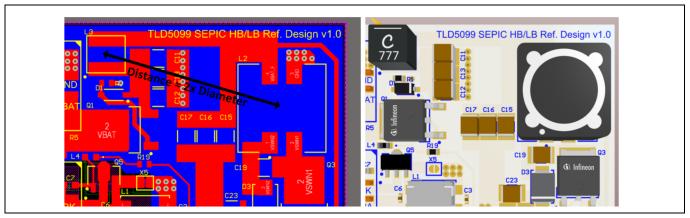

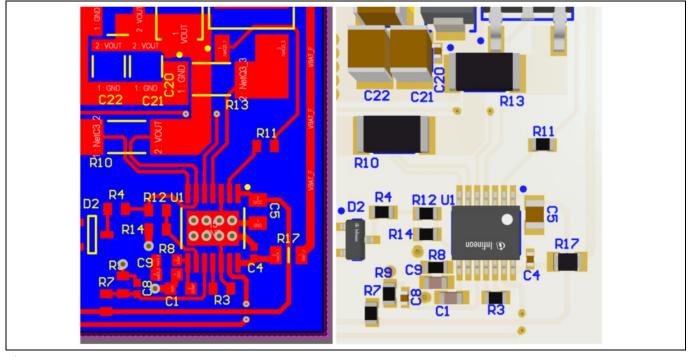

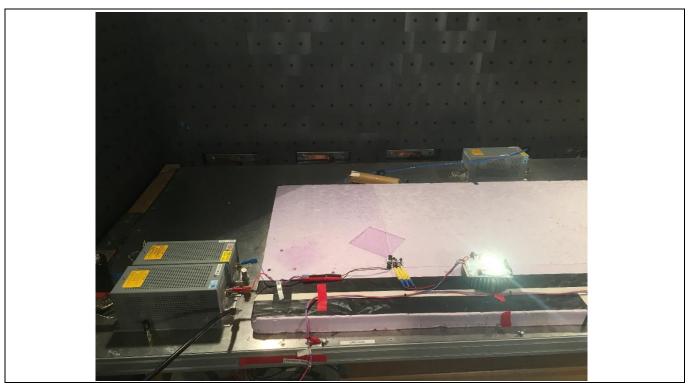

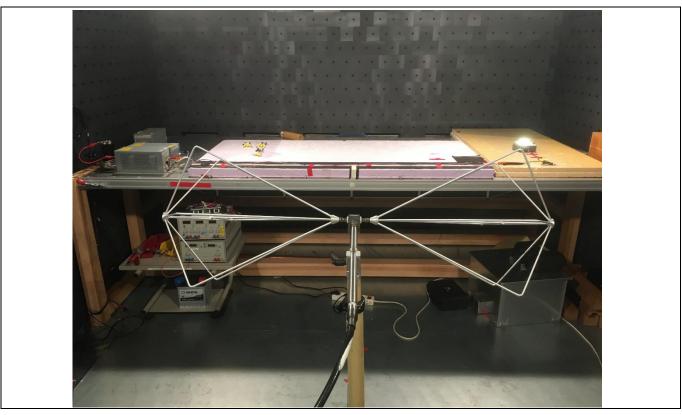

The PCB with the TLD5099EP is depicted in Figure 1 and a simplified block diagram of the overall system is depicted in Figure 2. A reverse polarity and input protection circuit ensures that no destructive events occur during transient disturbances along the supply line and in a reverse polarity situation. The TLD5099EP multitopology DC-DC controller drives and monitors the SEPIC power stage. The power stage provides the output power to the LED strings and is configured for current control mode. To provide EMC compliance according to CISPR25 for conducted and radiated emissions a PI-filter is placed at the input and a common mode choke is placed at the output. The HB activation circuit provides the possibility to drive only the LB or a combination of LB and HB. Furthermore, PWM dimming is also implemented to regulate the intensity of the LED string and to achieve a derating strategy under extreme operating conditions.

Figure 1 TLD5099EP SEPIC HB/LB reference design PCB

#### Automotive front light LED reference design with SEPIC topology

System design

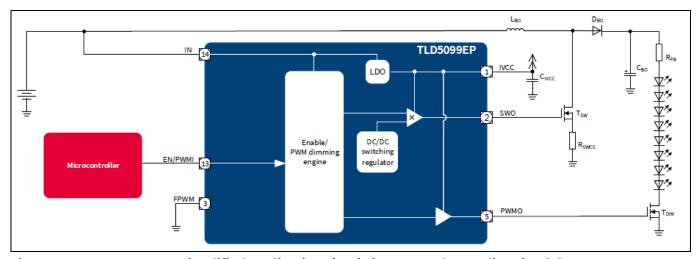

Figure 2 TLD5099EP SEPIC HB/LB reference design block diagram

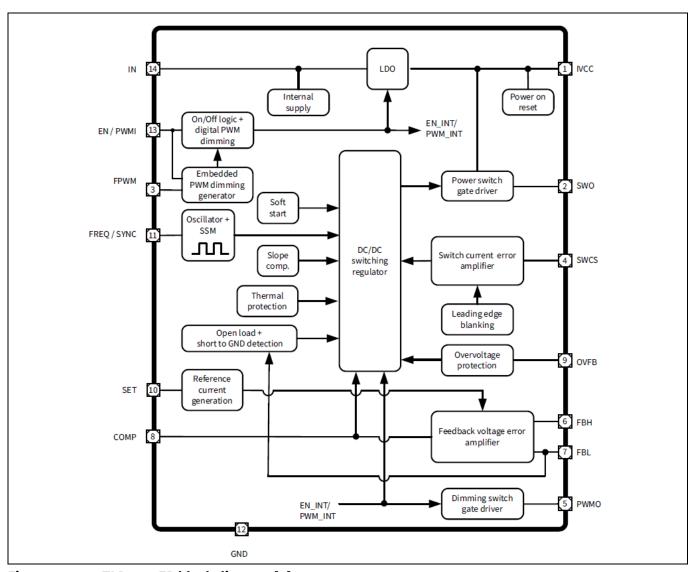

#### 2.1 TLD5099EP constant current controller

The TLD5099EP is an automotive qualified multi-topology DC-DC controller with built in diagnosis and protection features. The controller IC operates in an asynchronous topology, driving a low side n-channel power MOSFET from an internal 5 V linear regulator. In order to configure the power stage switching frequency, either the implemented oscillator with spread spectrum modulator, or an external clock source can be used. Below Table 2 summarizes the key product parameters.

Table 2 TLD5099EP main parameters

| Parameter                         | Symbol               | Range                                                      |

|-----------------------------------|----------------------|------------------------------------------------------------|

| Nominal supply voltage range      | $V_{IN}$             | 8 V to 34 V                                                |

| Extended supply voltage range     | $V_{IN}$             | 4.5 V to 45 V                                              |

| Switching frequency range         | $f_{\sf FREQ}$       | 100 kHz to 500 kHz oscillator frequency adjustment range   |

|                                   |                      | 250 kHz to 500 kHz synchronization frequency capture range |

| Maximum duty cycle                | $D_{max,fixed}$      | 91% fixed frequency mode                                   |

|                                   | $D_{max,sync}$       | 88% synchronization mode                                   |

| Gate driver peak sourcing current | $I_{\rm SWO,SRC}$    | 380 mA (typical)                                           |

| Gate driver peak sinking current  | I <sub>SWO,SNK</sub> | 550 mA (typical)                                           |

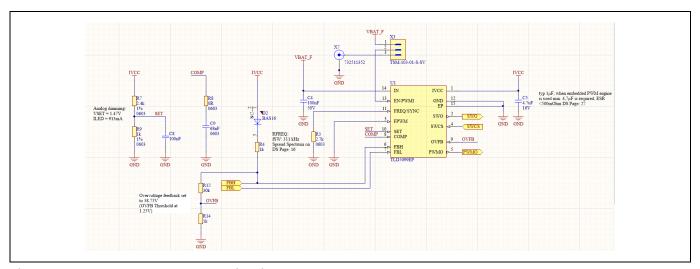

In the following section, the functions of the TLD5099EP will be explained briefly, in order to give guidance for proper partitioning. Figure 3 shows a block diagram of the TLD5099EP and Figure 4 shows the controller IC with its external circuitry. Before defining the SEPIC power stage, the protection features and configuration possibilities of the device will be discussed in the following sections.

# Automotive front light LED reference design with SEPIC topology

#### System design

Figure 3 TLD5099EP block diagram [1]

Figure 4 TLD5099EP schematic with external components

#### Automotive front light LED reference design with SEPIC topology

System design

# 2.1.1 Power supply

The TLD5099EP is powered by a reverse polarity protected supply voltage at the IN pin. In order to start-up the device, the input voltage must exceed the threshold of  $V_{\text{IN},\text{on}} = 4.85 \text{ V}$ . Additionally, the voltage applied to the EN/PWMI pin must be above  $V_{\text{EN/PWMI},\text{ON}} = 3 \text{ V}$  during startup. In the configuration given in Figure 4, an input undervoltage shutdown occurs at voltages below  $V_{\text{IN}_{\text{off}(\text{min})}} = 3.5 \text{ V}$ . This threshold is defined by the minimum rating of the IN pin at decreasing input voltage. Using the three-pin jumper X3, the EN/PWMI pin can either be supplied by the reverse polarity protected input voltage, or by applying an external PWM signal via the SMA-Connector X7. Therefore, an external PWM signal is used for the PWM dimming feature. More details on the PWM dimming feature and how the EN/PWMI pin needs to be connected in case the embedded PWM engine is used is given in Chapter 2.1.5. Once the supply voltages are above their undervoltage thresholds, the internal linear regulator delivers 5 V with up to 90 mA (max.) to the gate drivers. An external capacitor with an ESR below  $R_{\text{INCC,ESR}} = 0.5 \Omega$  must be placed close to the IVCC pin for stability and buffering purposes. According to the datasheet, a typical ceramic capacitor  $C_{\text{IVCC}} = 1 \text{ } \mu\text{F}$  is proposed. If embedded PWM dimming is used, the capacitance needs to be increased to  $C_{\text{IVCC}} = 4.7 \text{ } \mu\text{F}$ .

# 2.1.2 Switching frequency & spread spectrum

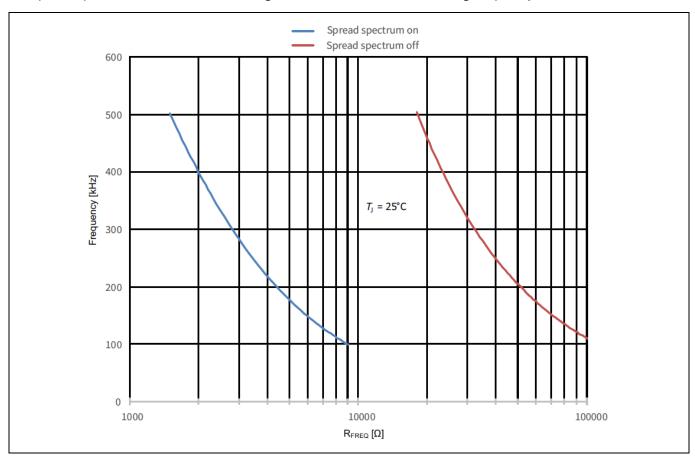

As listed in Table 2, the frequency of the internal oscillator can be configured in the range from 100 kHz to 500 kHz. This is done by connecting an external resistor  $R_{\text{FREQ}}$  between the FREQ pin and ground. The range of usable resistor values is divided into two sections. In Figure 5 below, it is seen that low resistor values activate the spread spectrum modulation, while higher resistances set the switching frequency without modulation.

Figure 5 TLD5099EP switching frequency versus  $R_{FREO}[1]$

#### Automotive front light LED reference design with SEPIC topology

#### System design

As the spread spectrum modulation helps to improve the EMC performance, the resistor is chosen such that the modulation is activated. While the modulation frequency is fixed to  $f_{\text{FM}} = 7$  kHz, the modulation depth varies with 15% of  $f_{\text{SW}}$ . The required resistance to configure a spread spectrum modulated switching frequency of  $f_{\text{SW}} = 310$  kHz, which is defined in the design specification and is determined by using Eq. 1.

$$R_{FREQ,SSMon} = \frac{1}{(600*10^{-12}*f_{SW})^{0.943}} - 600 = \frac{1}{(600*10^{-12}*310\,kHz)^{0.943}} - 600 = 2.69\,k\Omega \qquad ^{Eq.\,1}$$

Due to the off-the-shelf availability of the resistor, a resistance of  $R_{\text{FREQ}} = 2.7 \text{ k}\Omega$  is used in the application. This deviation leads to the real switching frequency calculated in Eq. 2.

$$f_{SW} = \frac{\left(\frac{1}{R_{FREQ,SSMon} + 600}\right)^{\frac{1}{0.943}}}{600 * 10^{-12}} = \frac{\left(\frac{1}{2.7 k\Omega + 600}\right)^{\frac{1}{0.943}}}{600 * 10^{-12}} = 309.5 kHz$$

To operate without spread spectrum modulation, the resistor calculated in Eq. 3 may be used.

$$R_{FREQ,SSMoff} = \frac{1}{(340 * 10^{-12} * f_{SW})^{1.13}} = \frac{1}{(340 * 10^{-12} * 310 \text{ kHz})^{1.13}} = 31.2 \text{ k}\Omega$$

Eq. 3

# 2.1.3 Output current configuration

The controlled output current of the TLD5099EP is set via a sensing resistor in the output path of the converter. Based on the design specification, a load current of  $I_{OUT} = 0.9$  A is desired for this application. This requirement is fulfilled in two steps. Firstly, the nominal output current is set to  $I_{OUT} = 1$  A, before using the analog dimming feature to fine-tune the current. The feedback resistor  $R_{FB}$ , represented by R10 in Figure 11, is calculated as given in Eq. 4.

$$R_{FB} = \frac{V_{REF}}{I_{OUT}} = \frac{0.3 V}{1 A} = 0.3 \Omega$$

Eq. 4

The maximum power loss of the shunt resistor is calculated in Eq. 5.

$$P_{RFR} = R_{FR} * I_{OUT}^2 = 0.3 \,\Omega * (0.9 \,A)^2 = 243 \,mW$$

To avoid overheating of the resistor, the WSL2010R3000FEA18 with a power rating of 1 W is considered.

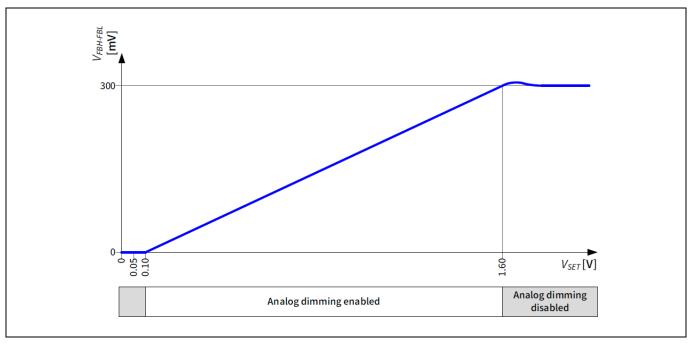

In the second step, the analog dimming feature is used to reduce the nominal output current to the desired value of  $I_{\text{OUT}} = 0.9 \text{ A}$ . To do so, the voltage level across the SET pin has to be configured accordingly. Figure 6 visualizes the relationship between  $V_{\text{SET}}$  and the controller feedback reference voltage  $V_{\text{REF}}$ . It is seen, that the reference voltage can be varied linearly based on a  $V_{\text{SET}}$  in the range between 100 mV and 1.6 V. In case the analog dimming is not needed, the SET pin must be connected to IVCC or an external voltage supply higher than 1.6 V.

### Automotive front light LED reference design with SEPIC topology

#### System design

Figure 6 Reduction of  $V_{REF}$  via  $V_{SET}$  [1]

To reduce the set nominal output current to the desired  $I_{OUT} = 0.9$  A, an analog dimming of 90% is necessary. For this purpose, the controller feedback reference voltage has to be lowered to 270 mV. The corresponding SET voltage is calculated using Eq. 6.

Eq. 6

$$V_{SET} = 5*R_{FB}*I_{OUT} + 0.1\ V \rightarrow 5*0.3\ \varOmega*0.9\ A + 0.1\ V = 1.45\ V$$

This voltage level can easily be supplied to the SET pin using a resistor divider with reference to IVCC. By choosing  $R_{\text{SET2}} = 1 \text{ k}\Omega$ ,  $R_{\text{SET1}}$  can be determined with Eq. 7. It is recommended to use a tolerance of  $\pm$  1% when choosing the SET resistor to increase accuracy.

$$R_{SET1} = \frac{V_{IVCC} * R_{SET2}}{V_{SET}} - R_{SET2} = \frac{5 V * 1 k\Omega}{1.45 V} - 1 k\Omega = 2.448 k\Omega$$

Eq. 7

$$\rightarrow$$

chosen = 2.4  $k\Omega$

Due to the deviation from the ideal  $R_{\text{SET1}}$  resistance, the resulting output current is as in below Eq. 8.

$$V_{SET} = V_{IVCC} * \frac{R_{SET2}}{R_{SET1} + R_{SET2}} = 5 V * \frac{1 k\Omega}{2.4 k\Omega + 1 k\Omega} = 1.47 V$$

$$I_{OUT} = \frac{V_{SET} - 0.1 V}{5 * R_{FR}} = \frac{1.47 V - 0.1 V}{5 * 0.3 \Omega} = 0.913 A$$

#### Automotive front light LED reference design with SEPIC topology

System design

#### 2.1.4 Switch current sense

Besides the sensing resistor for the output current, one further resistor is required for the current mode control loop and the switch current limitation. The so called  $R_{SWCS}$ , which is represented by R13 in Figure 11, limits the current through the n-channel MOSFET to a certain value.

The maximum voltage across the sensing resistor must not reach the threshold of  $V_{SWCS,min}$  = 125 mV. As this condition must not only be valid for the steady state, but also for the transition phase, the current limit is set 25% above the actual switch peak current as safety margin. Using the peak current calculated in Chapter 2.2.2, the resistance is determined in Eq. 9.

$$R_{SWCS} = \frac{V_{SWCS,min}}{1.25 * I_{Q,peak}} = \frac{125 \ mV}{1.25 * 5.13 \ A} \approx 18 \ m\Omega$$

Eq. 9

The maximum power loss of the shunt resistor is calculated in Eq. 10.

$$P_{RSWCS} = R_{SWCS} * I_{O,RMS}^2 = 18 \, m\Omega * (3.92 \, A)^2 = 0.277 \, W$$

To avoid overheating of the resistor, the WSL2010R0180FEA18 with a power rating of 1 W is considered.

# 2.1.5 PWM dimming

The PWM dimming feature is used to modulate the average current in the load to a desired value. This feature is useful for brightness control and to implement derating strategies in extreme operating conditions. The output current which was set is not modified in amplitude but is modulated with a lower PWM frequency (100 Hz to 500 Hz) by an additional dimming MOSFET. The modulation can be done in two different ways which are external PWM dimming or embedded PWM dimming. In this reference design the external PWM dimming approach is used. In this case, the FPWM pin is also connected to GND because this is necessary only for embedded PWM dimming.

# 2.1.5.1 External PWM dimming

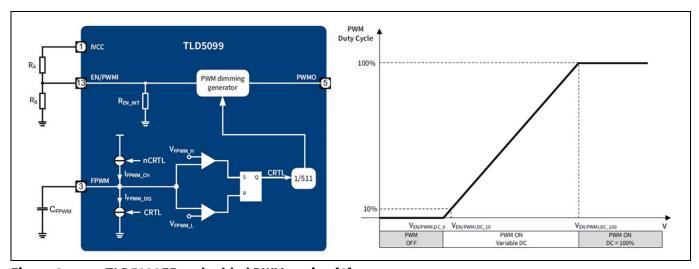

Figure 7 TLD5099EP simplified application circuit for external PWM dimming [1]

The concept of the external PWM dimming is shown in Figure 7. An external source (e.g. microcontroller) is used to implement the PWM dimming. In case a constant logic high signal is present at the EN/PWMI pin no PWM dimming is used. However, if a PWM is applied in the range of 100 Hz to 500 Hz by the external source, the PWM

#### Automotive front light LED reference design with SEPIC topology

#### System design

dimming feature is activated. When the PWM dimming is active, the device differentiates between enable off and PWM dimming signal by requiring the signal at the EN/PWMI pin to stay low for the  $t_{\text{EN,OFF,DEL,typ}}$  = 10 ms which corresponds to 100 Hz.

# 2.1.5.2 Embedded PWM dimming

In case no external source is in place to provide a PWM signal to achieve the PWM dimming one can also use the internal embedded PWM engine of the device. Figure 8 depicts the concept. A voltage divider at the EN/PWMI pin is used to provide a specific voltage which correlates to a specific DC. Furthermore, a capacitor is used at the FPWM pin to set the PWM frequency (100 Hz to 500 Hz).

Note:

If the internally generated voltage  $V_{\text{IVCC}}$  is used to power the voltage divider at the EN/PWMI pin, a specific startup circuit is necessary. This startup circuit is necessary because the EN/PWMI needs to have a voltage above  $V_{\text{EN/PWMI,ON}} = 3 \text{ V}$  during startup that the internal LDO can start to operate, as discussed in Chapter 2.1.1.

For more details regarding embedded PWM dimming and the startup circuit please refer to the product datasheet [1].

Figure 8 TLD5099EP embedded PWM engine [1]

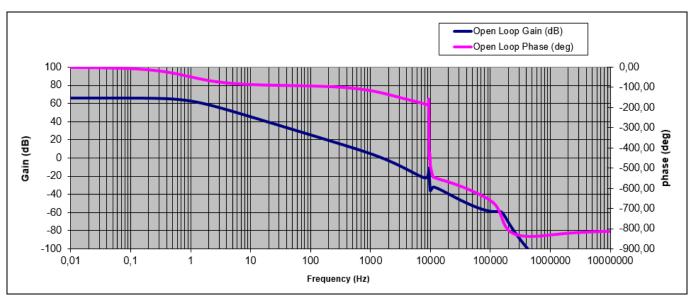

# 2.1.6 Compensation network

The compensation network consisting of a serial RC-network determines the stability of the control loop. In order to select the proper values for the given partitioning, a calculation sheet is used. Under consideration of every possible input and output voltage condition, the best fitting component values were chosen. Figure 9 represents the Bode plot of the controller at typical input voltage and activated high beam. The compensation network which ensures a stable system over the whole operational range is  $R_{\text{COMP}} = 0 \Omega$  and  $C_{\text{COMP}} = 68 \text{ nF}$ .

### Automotive front light LED reference design with SEPIC topology

System design

Figure 9 TLD5099EP Bode plot with  $C_{COMP} = 68 \text{ nF}$  and HB active at typical input voltage

# 2.1.7 Overvoltage protection

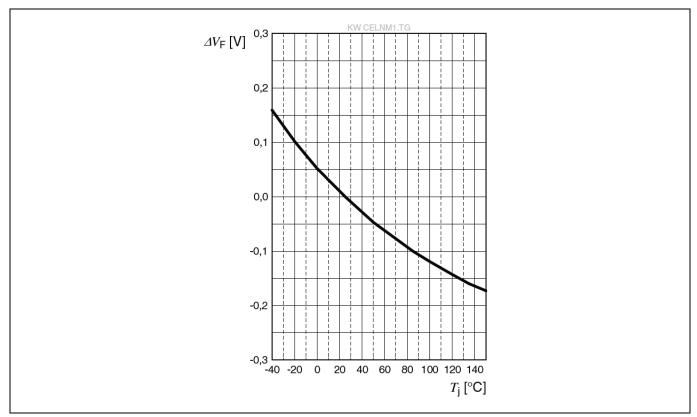

The output overvoltage protection feature helps to avoid too high voltage levels during an open load condition. In the case of the considered application, the maximum output voltage occurs when the HB and the LB is active. In Figure 10, the temperature dependency of the LED forward voltage is shown.

Figure 10 Temperature dependency of the LED forward voltage [2]

#### Automotive front light LED reference design with SEPIC topology

#### System design

It is seen, that the forward voltage increases by up to 0.16 V per LED at negative temperatures. The output voltage at negative temperature of -40°C is calculated in Eq. 11. In this case the maximum possible forward voltage  $V_{\text{F,LED,max}}$  for every LED is considered.

$$V_{OUT,neg40} = \#LEDs * V_{F,LED,max} + \#LEDs * \Delta V_F = 9 * 3.4 V + 9 * 0.16 V = 32.04 V$$

Eq. 11

An overvoltage fault is triggered, once the voltage at the OVFB pin reaches  $V_{\text{OVFB,TH,typ}} = 1.25 \text{ V}$ . By using a resistor divider and selecting the lower resistor as  $R_{\text{OVL}} = 1 \text{ k}\Omega$ , the upper resistor  $R_{\text{OVH}}$  can be calculated using Eq. 12. Including a safety margin, the overvoltage threshold is selected as 38 V.

$$R_{OVH} = \frac{V_{OUTOV} * R_{OVL}}{V_{OVFB,TH,typ}} - R_{OVL} = \frac{38 \, V * 1 \, k\Omega}{1.25 \, V} - 1 \, k\Omega = 29.4 \, k\Omega$$

Eq. 12

$$\rightarrow$$

chosen = 30  $k\Omega$

Due to the slightly higher resistance, the actual overvoltage threshold increases as given in Eq. 13.

$$V_{OUTOV} = V_{OVFB,TH,typ} * \frac{R_{OVH} + R_{OVL}}{R_{OVL}} = 1.25 V * \frac{30 k\Omega + 1 k\Omega}{1 k\Omega} = 38.75 V$$

Once this threshold is reached, the TLD5099EP will stop the switching activities, until the voltage at the OVFB pin decreases by the hysteresis value  $V_{\text{OVFB,HYS,min}} = 50 \text{ mV}$ .

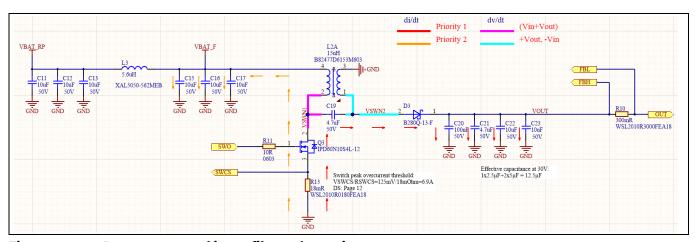

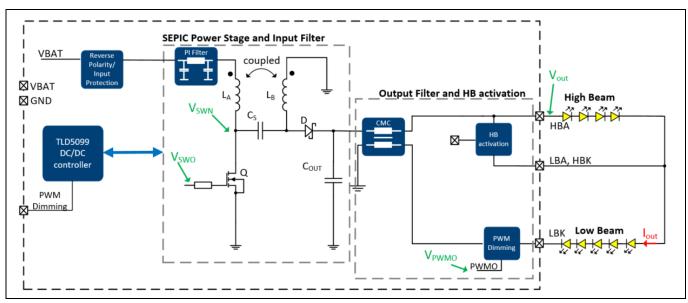

# 2.2 SEPIC power stage and input filter

Figure 11 Power stage and input filter schematic

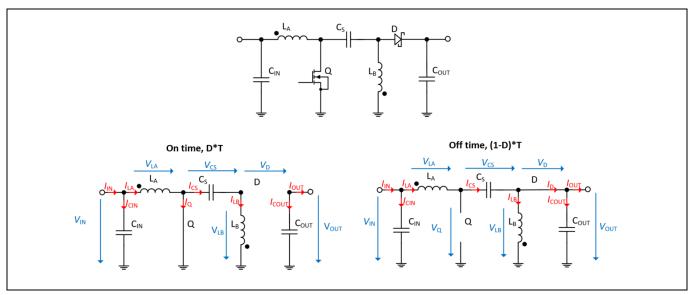

As given in the system description, the target of this design is to drive a combination of LB and HB LEDs based on the SEPIC topology. The SEPIC topology offers a buck-boost behavior which is beneficial to stabilize the varying input voltage from a battery supply in a car. Furthermore, it has an inherent short to GND protection due to the SEPIC coupling capacitor compared for example to the classical boost converter topology. However, there are also drawbacks related to the SEPIC topology as for example higher current/voltage stress on the active components and the need for two inductors or one coupled inductor. Therefore, thermal design considerations are extremely important when designing a SEPIC power stage. The operating current and voltage waveforms for the main components of the SEPIC power stage can be seen in Figure 12 and Figure 13.

System design

Figure 12 SEPIC power stage during on and off time

Figure 13 SEPIC power stage voltage and current waveforms in steady state and CCM

### 2.2.1 Passive components

One of the fundamental parameters of every switched mode power supply is the DC with which the MOSFET is driven. In case of the SEPIC topology, this parameter is as given in Eq. 14. The diode forward voltage  $V_D$  is also impacting the DC due to the asynchronous topology. However, a Schottky diode is used and the effect of the forward voltage drop is considered as small compared to the input and output voltage and is therefore neglected in the calculations.

#### Automotive front light LED reference design with SEPIC topology

System design

$$D = \frac{V_{OUT} + (V_D)}{V_{IN} + V_{OUT} + (V_D)}$$

Eq. 14

While the maximum duty cycle occurs at  $V_{\text{IN,min}}$ , the minimum duty cycle is computed considering  $V_{\text{IN,max}}$ . As the output voltage of the converter changes depending on the HB activation, the number of operating points is doubled. Referring to the  $V_{\text{IN}}$  and  $V_{\text{OUT}}$  voltage levels given in Table 1, four extreme operating points can be calculated. Table 3 summarizes the resulting duty cycles.

Table 3 Duty cycle variation with respect to  $V_{IN}$  and  $V_{OUT}$

|                                     | $V_{\rm IN,max}$ = 16 V | <i>V</i> <sub>IN,min</sub> = 8 V | $V_{\rm IN,typ}$ = 13.5 V |

|-------------------------------------|-------------------------|----------------------------------|---------------------------|

| $V_{\text{OUT,max}} = 27 \text{ V}$ | 62.8%                   | 77.1%                            | 66.6%                     |

| V <sub>OUT,min</sub> = 13.75 V      | 46.2%                   | 63.2%                            | 50.4%                     |

In the following calculation steps, these operating points are used to determine the power stage components. Based on an assumed converter efficiency of  $\eta = 85\%$ , the maximum input current is calculated. As seen in Eq. 15, the maximum input current  $I_{\text{IN,max}}$  occurs at  $V_{\text{IN,min}}$  and  $V_{\text{OUT,max}}$ .

$$\eta = \frac{V_{OUT.max} * I_{OUT}}{V_{IN,min} * I_{IN,max}} \rightarrow I_{IN,max} = \frac{I_{OUT}}{\eta} * \frac{V_{OUT,max}}{V_{IN,min}}$$

Eq. 15

$$I_{IN,max} = \frac{0.9 A}{0.85} * \frac{27 V}{8 V} = 3.57 A$$

The inductor size depends on the allowed current ripple  $\Delta I_L$ . When defining the peak-to-peak value of the ripple, the target is to ensure CCM operation. However, the TLD5099EP can also operate and control the power stage in DCM but one has to keep in mind that the transfer function on the power stage will change and could cause instability. A typical proposal is to select 20% of the maximum input current as allowed inductor current ripple. Using the previously calculated maximum input current results in the ripple given in Eq. 16.

$$\Delta I_L = 0.2 * I_{IN,max} = 0.2 * 3.57 A = 0.714 A$$

Eq. 16

With the current ripple calculated in Eq. 16, the required inductor can be determined. One must consider, that for a coupled inductor, approximately half the inductance value compared to uncoupled coils can be assumed due to mutual inductance and a coupling factor of approximately one. The minimum required coupled inductor value is calculated in the following Eq. 17.

$$L_{Coupled} \ge \frac{1}{2} * \frac{V_{IN,min} * D_{max}}{\Delta I_L * f_{SW}} \ge \frac{1}{2} * \frac{8 \ V * 0.771}{0.714 \ A * 310 \ kHz}$$

$$L_{Coupled} \ge 13.9 \ \mu H \to 15 \ \mu H \ chosen$$

Eq. 17

As already mentioned previously, it is recommended to ensure that the CCM is guaranteed in the different operating points of the converter. The transition to the DCM occurs when the  $\Delta I_{L}$  ripple exceeds double the output current. Using Eq. 18, the  $\Delta I_{L}$  at varying DC can be determined.

$$\Delta I_L = \frac{V_{IN} * D}{2 * L_{Coupled} * f_{SW}}$$

Eq. 18

#### Automotive front light LED reference design with SEPIC topology

#### System design

Due to the fact, that the inductor current ripple is proportional to the DC, only the operating cases at maximum output voltage were considered for the calculations summarized in Table 4. It is seen, that CCM is given over the complete static input voltage range.

Table 4 Ripple current with respect to input voltage

|                                     | V <sub>IN,max</sub> = 16 V |        | <i>V</i> <sub>IN,min</sub> = 8 V |        | $V_{\rm IN,typ}$ = 13 V |        |

|-------------------------------------|----------------------------|--------|----------------------------------|--------|-------------------------|--------|

| $V_{\text{OUT,max}} = 27 \text{ V}$ | Duty cycle                 | 62.8%  | Duty cycle                       | 77.1%  | Duty cycle 66.6%        |        |

| $V_{OUT,max} = 21 \text{ V}$        | $\Delta I_{L}$             | 1.08 A | $\Delta I_{L}$                   | 0.66 A | $\Delta I_{L}$          | 0.93 A |

With the calculated current ripples, the peak currents through both inductors can be determined. The peak current in inductor  $L_A$  is given by the maximum input current plus half the current ripple. In case of  $L_B$  the maximum output current plus half the current ripple is considered. As the maximum input current occurs at minimum input voltage, a ripple of  $\Delta I_L = 0.66$  A is considered in Eq. 19.

$$I_{LA,peak} = I_{IN,max} + \frac{\Delta I_L}{2} = 3.63 A + \frac{0.69 A}{2} = 3.98 A$$

$$I_{LB,peak} = I_{OUT} + \frac{\Delta I_L}{2} = 0.9 A + \frac{0.69 A}{2} = 1.25 A$$

Eq. 19

To avoid saturation effects, the inductor saturation current should be approximately 20% higher than the peak current. For the selection of the inductor, the components from Table 5 were compared. From this comparison, the 15  $\mu$ H coupled coil TDK B82477D6 was selected.

Table 5 Possible candidates for the main coupled inductor

| Manuf.    | Series      | Induct. | Shielded | RMS curr.<br>(both wind.) | Sat. curr.           | DCR     | Max.<br>temp | PCB area            |

|-----------|-------------|---------|----------|---------------------------|----------------------|---------|--------------|---------------------|

| Coilcraft | MSD1260T    | 22 μΗ   | Yes      | 1.76 A <sup>1)</sup>      | 5.02 A <sup>2)</sup> | 116 mΩ  | 165°C        | 151 mm <sup>2</sup> |

| Coilcraft | MSD1260T    | 15 μΗ   | Yes      | 2.06 A <sup>1)</sup>      | 5.8 A <sup>2)</sup>  | 85 mΩ   | 165°C        | 151 mm <sup>2</sup> |

| Coilcraft | MSD1278     | 22 μΗ   | Yes      | 1.99 A <sup>1)</sup>      | 6.8 A <sup>2)</sup>  | 96 mΩ   | 165°C        | 151 mm <sup>2</sup> |

| Coilcraft | MSD1278     | 15 μΗ   | Yes      | 2.3 A <sup>1)</sup>       | 9.1 A <sup>2)</sup>  | 72 mΩ   | 165°C        | 151 mm <sup>2</sup> |

| TDK       | B82477D4    | 22 μΗ   | Yes      | 2.8 A <sup>3)</sup>       | 4.5 A                | 70 mΩ   | 150°C        | 156 mm <sup>2</sup> |

| TDK       | B82477D4    | 15 μΗ   | Yes      | 3.25 A <sup>3)</sup>      | 5.5 A <sup>5)</sup>  | 52.5 mΩ | 150°C        | 156 mm <sup>2</sup> |

| TDK       | B82477D6    | 15 μΗ   | Yes      | 4.92 A <sup>3)</sup>      | 8.7 A <sup>5)</sup>  | 29.6 mΩ | 150°C        | 156 mm <sup>2</sup> |

| Vishay    | IHCL-4040DZ | 22 μΗ   | Yes      | 2.5 A <sup>1)</sup>       | 4.75 A <sup>4)</sup> | 177 mΩ  | 155°C        | 108 mm <sup>2</sup> |

| Vishay    | IHCL-4040DZ | 15 μΗ   | Yes      | 3.3 A <sup>1)</sup>       | 6 A <sup>4)</sup>    | 110 mΩ  | 155°C        | 108 mm <sup>2</sup> |

<sup>1)</sup> Current applied to both windings simultaneously which causes a 40°C temperature rise

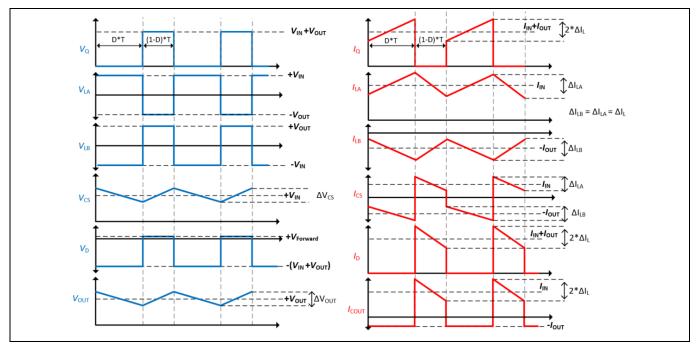

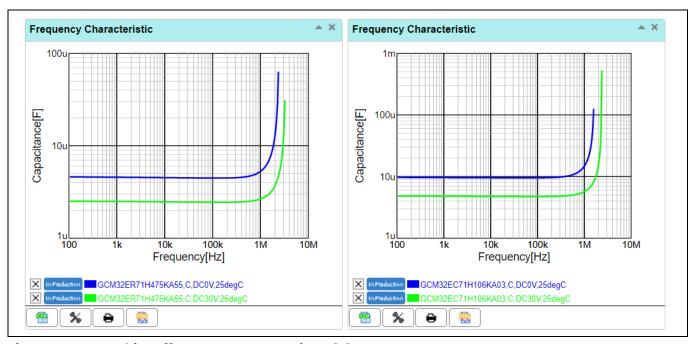

The forward current through the LED string will vary depending on the output voltage ripple. In order to select the proper output capacitor, firstly the maximum allowed voltage ripple has to be defined. It depends on the transresistance of the LED chain in the operating point and the maximum allowed peak to peak current ripple in the LED string. The resistance is determined using the forward current graph shown in Figure 14.

<sup>2) 30%</sup> drop of inductance, current in both windings simultaneously

<sup>3)</sup> Current which can be applied (sum of both windings) up to 105°C ambient

<sup>4) 20%</sup> drop of inductance, current in both windings simultaneously

<sup>5) 10%</sup> drop of inductance, current in both windings simultaneously

#### Automotive front light LED reference design with SEPIC topology

System design

Figure 14 I/V curve from the load LED OSRAM OSLON® Compact PL, KW CELNM1.TG [2]

From the read values, the transresistance is calculated in Eq. 20.

$$R_{LED} = \frac{\Delta V_F}{\Delta I_F} = \frac{3.05 - 2.95}{1.25 - 0.75} = 200 \, m\Omega$$

The maximum output voltage ripple, computed in Eq. 21, distributes equally over the number of LEDs. Here, the worst case occurs when only the five LB LEDs are active.

$$\Delta V_{LED} = \frac{\Delta V_{OUT}}{\# LEDs} = R_{LED} * \Delta I_{LED} \rightarrow \Delta V_{OUT} = \# LEDs * R_{LED} * I_{LED}$$

Eq. 21

$$\Delta V_{OUT} = 5 * 200 \, m\Omega * 200 \, mA = 200 \, mV$$

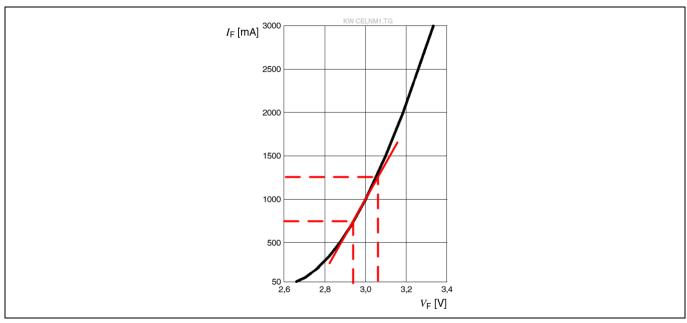

Based on the output voltage ripple requirements, the output capacitor can be calculated. During the on-time, the output capacitor needs to provide the output current. ESR considerations should be included if they have a relevant contribution. In this case ceramic capacitors will be used in parallel which offers very low ESR. The worst-case output current ripple occurs at maximum duty cycle. These parameters, including the switching frequency, are required to calculate the output capacitor using Eq. 22.

$$C_{OUT} \ge \frac{I_{OUT} * D_{max}}{\left(\Delta V_{OUT} - \Delta V_{OUTESR}\right) * f_{SW}}$$

$$C_{OUT} \ge \frac{0.9 \, A * 0.771}{(0.2 \, V) * 310 \, kHz} \ge 11.2 \, \mu F$$

$$\rightarrow$$

chosen 1 x 4.7  $\mu F$  + 2 x 10  $\mu F$  = 24.7  $\mu F$   $\rightarrow$  effective @30V  $\approx$  12.5  $\mu F$

#### Automotive front light LED reference design with SEPIC topology

#### System design

The chosen output capacitors are:

- 1x 4.7 μF, X7R, 50 V (GCM32ER71H475KA55)

- 2x 10 μF (GCM32EC71H106KA03)

These capacitors sum up in total to nominal 24.7  $\mu$ F. However, when considering the DC-bias effect of multilayer ceramic capacitors the effective capacitance drops to approximately half the nominal value which is shown in Figure 15, where the blue line corresponds to 0 V DC-bias and the green line to 30 V DC-bias [3]

Note:

The DC-bias effect reduces the nominal capacitance at the output capacitors approximately to the half value (@ 30 V output voltage). Switching from a 50 V rated capacitor to for example a 100 V capacitor does not significantly improve the DC-bias effect.

Figure 15 DC-bias effect on output capacitors [3]

The ripple current rating of the output capacitor can be calculated using Eq. 23. During the on-time, the negative output current and during the OFF-time, the input current flows into the output capacitor. Here, the worst case occurs at minimal input voltage, thus maximal input current. Since low ESR ceramic capacitors are used in parallel, the ripple current rating of the capacitors is sufficient.

$$I_{COUT,RMS} = \sqrt{\frac{-I_{OUT}^2}{T}} * \int_0^{D_{max}*T} d_t + \frac{I_{IN,max}^2}{T} * \int_{D_{max}*T}^T d_t$$

$$= \sqrt{-I_{OUT}^2 * D_{max} + I_{IN,max}^2 * (1 - D_{max})}$$

$$I_{COUT,RMS} = \sqrt{-0.9 A^2 * 0.771 + 3.57 A^2 * (1 - 0.771)} = 1.88 A$$

One of the key components of the SEPIC topology is the coupling capacitor  $C_S$  which has to further provide the input voltage during the switching activities. A reasonable maximal peak to peak voltage variation across the  $C_S$  would be 10% of the minimum input voltage. During the on-time, the negative output current flows through the coupling capacitor. The capacitance is calculated using Eq. 24.

#### Automotive front light LED reference design with SEPIC topology

System design

$$C_S \ge \frac{I_{OUT} * D_{max}}{0.1 * V_{IN,min} * f_{SW}} \ge \frac{0.9 A * 0.771}{0.1 * 8 V * 310 kHz} \ge 2.79 \,\mu F$$

$$\Rightarrow chosen = 4.7 \,\mu F$$

Eq. 24

The RMS current through the coupling capacitor is given in Eq. 25.

$$I_{CS,RMS} = \sqrt{I_{OUT}^2 * D_{max} + I_{IN,max}^2 * (1 - D_{max})}$$

$$= \sqrt{0.9 A^2 * 0.771 + 3.57 A^2 * (1 - 0.771)} = 1.88 A$$

When selecting the capacitor component between the switching node and the output, one must consider the voltage rating. The maximum voltage levels across the coupling capacitor is shown in Figure 13. The static and transient case is shown in Eq. 26.

$$V_{CS,max} = V_{IN,max} = 16 V$$

Eq. 26

$V_{CS,max trans} = V_{IN,Trans max} = 35 V$

# 2.2.2 Switching MOSFET

The switching MOSFET in the SEPIC topology faces high current and voltage stress as it can be seen in the current and voltage waveforms in Figure 13. Peak current and voltage requirements can be calculated using equation Eq. 27.

$$I_{Q,peak} = I_{IN,max} + I_{OUT} + \Delta I_L = 3.57 A + 0.9 A + 0.66 A = 5.13 A$$

$$V_{Q,peak} = V_{IN,max} + V_{OUT,max} = 16 V + 27 V = 43 V$$

$$V_{Q1,peak,Trans} = V_{IN,Trans,max} + V_{OUT,max} = 35 V + 27 V = 62 V$$

Power MOSFETs in switching converters suffer from different loss mechanisms. The most dominating ones are the conduction losses, switching losses and reverse recovery losses due to the switching diode. Switching and conduction losses will be discussed analytically. Reverse recovery losses are not included in the analytical calculations but will be considered in a simulation presented in Chapter 2.2.2.1.

# 2.2.2.1 Switching losses

Switching losses are usually the dominant losses in switching converters. The switching losses increase with switching frequency, peak current and voltage during the switching event and decrease with faster slew rates. However, faster slew rates also have a negative impact on EMC performance, thus a compromise between switching losses and switching slew rates has to be made. In a SEPIC converter, the stress on the power MOSFET is especially high, since the peak voltage during the switching transient is approximately  $V_{\text{IN}}$  plus  $V_{\text{OUT}}$ . Furthermore, the peak current during the switching transient is  $I_{\text{IN}}$  plus  $I_{\text{OUT}}$ . Therefore, an appropriate analysis of the switching losses and thermal design is crucial for the switching MOSFET.

### Automotive front light LED reference design with SEPIC topology

System design

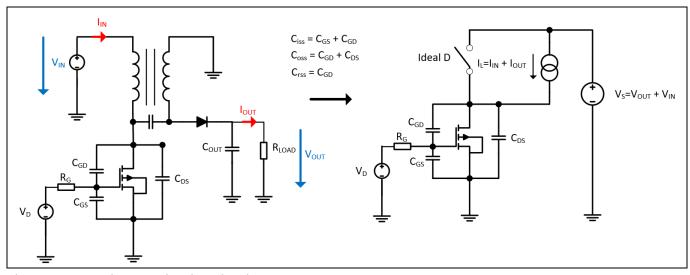

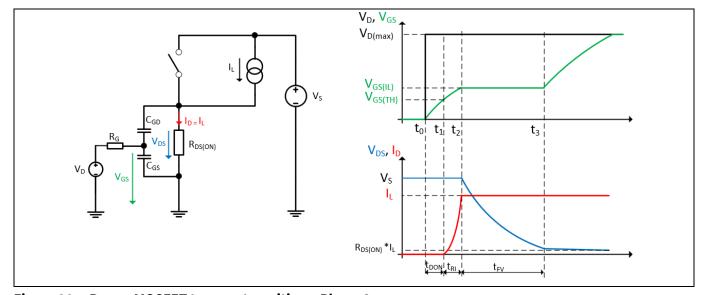

Figure 16 Equivalent circuit switching losses

Power MOSFETs have parasitic capacitances which determine the switching behavior. Figure 16 depicts a circuit which represents what occurs in a hard-switched converter. For simplicity the diode can be replaced with an ideal diode and the inductor can be replaced with a current source. The voltage source is modeled with a magnitude of  $V_{IN}$  plus  $V_{OUT}$  and the load current as  $I_{IN}$  plus  $I_{OUT}$  which gives a reasonable approximation. Refer to Figure 13 for the current and voltage waveforms on the switching MOSFET. The switching process can be separated into four phases and is shown for a turn-on.

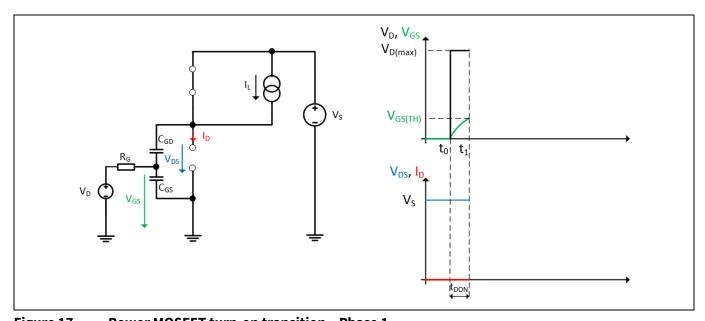

#### Phase 1, $t_0 \le t \le t_1$ :

Figure 17 Power MOSFET turn-on transition – Phase 1

During phase 1, which is depicted in Figure 17, the diode conducts and the load current flows through the diode. At time  $t_0$  the gate drive voltage  $V_{D(max)}$  is applied to the gate of the MOSFET. In this moment  $V_{GS}$  starts to rise.  $V_{GS}$  rises until the threshold voltage  $V_{GS(TH)}$  is reached where the MOSFET begins to conduct. During this time interval, the drain source voltage is clamped by the ideal diode to the supply voltage and the drain current is zero.

#### Automotive front light LED reference design with SEPIC topology

System design

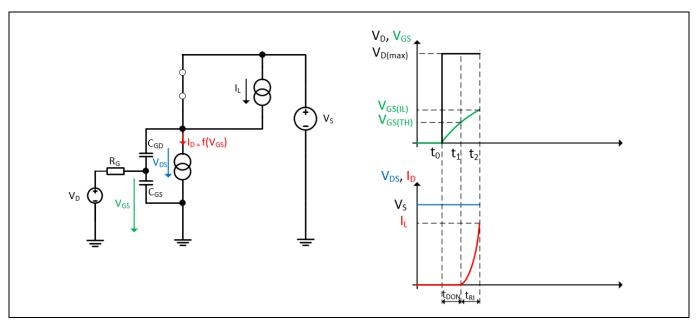

#### Phase 2, $t_1 \le t \le t_2$ :

Figure 18 Power MOSFET turn-on transition - Phase 2

During phase 2, which is depicted in Figure 18, the current in the drain source channel in the MOSFET rises. The drain current is a function of the applied  $V_{GS}$ . The  $V_{GS}$  rises until the drain current reaches the level of the load current. Until that moment the ideal diode still clamps the drain source voltage to the supply voltage since current is flowing through the diode. Delay time  $(t_{DON})$  is the time it takes from when the drive voltage is applied to the gate of the MOSFET  $(t_0)$  until the current starts to flow  $(t_1)$ . The time where the drain current starts to flow  $(t_1)$  until the load current is reached  $(t_2)$  is called current rise time  $(t_{RI})$ .

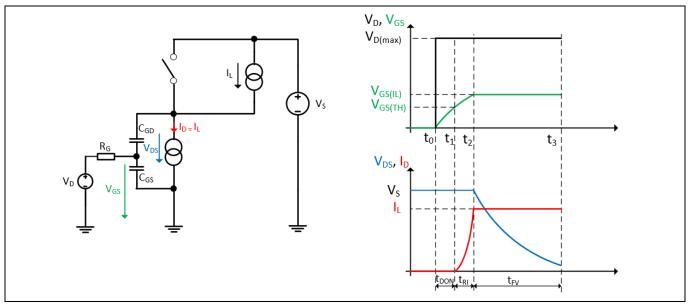

#### Phase 3, $t_2 \le t \le t_3$ :

During phase 3, which is shown in Figure 19, all the load current is now flowing through the MOSFET, thus the diode is turned off. Therefore, the drain source voltage can start to decrease.

Note:

Reverse recovery effects would be visible at this stage and would manifest itself in an increase of the drain current above the load current level. This would provide the reverse recovery charge which is necessary so that the switching diode is able to turn off (= reverse recovery effect)

The potential on the drain of the MOSFET starts to fall. A consequence of a negative voltage slope at the drain is that  $C_{rss}$  capacitor needs to be charged by the gate driver. The gate charge-current flows through  $C_{rss}$  to provide the necessary charge. As a consequence, the gate source voltage cannot increase and stays constant. This is the so called "Miller Plateau". The gate charge current is constant during that time since  $V_D$  and  $V_{GS}$  are constant. Therefore, the assumption would be that the drain source voltage decreases linearly. However, the slope is observed to be steepest at t2 and flattens out to t3. This is due to the fact that the reverse transfer capacitance  $C_{rss}$  is nonlinear.  $C_{rss}$  decreases with increasing drain source voltage. Therefore, at time  $t_2$ ,  $C_{rss}$  is at a minimum since  $V_{DS}$  is at a maximum thus, the slope is steepest at  $t_2$ .

### Automotive front light LED reference design with SEPIC topology

System design

Figure 19 Power MOSFET turn-on transition - Phase 3

#### Phase 4, $t_3 \le t \le t_4$ :

During phase 4, which is shown in Figure 20, the gate source voltage finally can increase further since the reverse transfer capacitance  $C_{rss}$  is fully charged and the gate charge current is used to further increase the gate source voltage. In this phase the on-state resistance is further reduced until the gate is charged up to the gate drive voltage  $V_D$ . The to the load current times the on-state resistance. When the MOSFET is fully switched on, the drain source voltage reduces to the equivalent of  $I_L * R_{DS(ON)}$ .

Figure 20 Power MOSFET turn-on transition - Phase 4

It can be concluded that the total switching losses can be approximated using the following formula.

$$P_{SW} = V_S * I_L * \frac{t_{RI} + t_{FV} + t_{FI} + t_{RV}}{2} * f_{SW}$$

Eq. 28

#### Automotive front light LED reference design with SEPIC topology

#### System design

This formula implies a triangular area formed by  $V_S$  and  $I_L$  which is an overestimation since the drain source voltage and drain current does not decrease/increase linearly due to the voltage dependent reverse transfer capacitance  $C_{rss}$  and the quadratic relationship between  $V_{GS}$  and  $I_D$ , thus leads to overestimated switching losses. Another challenge is to calculate the switching times.

$$t_{RI} = R_G * C_{iss} * \ln\left(\frac{V_D - V_{GS(TH)}}{V_D - V_{GS(IL)}}\right)$$

$$t_{FV} = R_G * C_{rss} * \frac{V_S}{V_D - V_{GS(IL)}}$$

$$t_{FI} = R_G * C_{iss} * \ln\left(\frac{V_{GS(IL)}}{V_{GS(TH)}}\right)$$

$$t_{RV} = R_G * C_{rss} * \frac{V_S}{V_{GS(IL)}}$$

The four switching times can be calculated using Eq. 29.

The following parameters are required for the calculations:

- R<sub>G</sub> ... Gate resistance

- $C_{iss}$  ... Input capacitance  $(C_{gd} + C_{gs})$

- *V*<sub>D</sub>... Gate drive voltage

- V<sub>GS(IL)</sub>... Plateau voltage (Miller plateau)

- $V_{GS(TH)}$  ... Gate source threshold voltage

- V<sub>s</sub>... Drain source voltage during switching event

- $C_{rss}$  ... Reverse transfer capacitance ( $C_{gd}$ )

Some parameters which are necessary to calculate the switching times vary in relation to the drain source voltage, have possible large spread or are difficult to extract from the datasheet. For this design firstly, an analytical calculation of the switching losses and conduction losses is given and secondly, it is compared to a simulation done in SPICE. For this design the Infineon OptiMOS™ –T2 power transistor IPD60N10S4L-12 was selected. Another possible candidate for the switching MOSFET could be also the OptiMOS™ –5 power transistor IAUC28N08S5L230. Table 6 summarizes the most important parameters of the IPD60N10S4L-12 power MOSFET:

Table 6 IPD60N10S4L-12 OptiMOS™-T2 n-channel power transistor parameters [4]

| Parameter                   | Min.  | Тур.    | Max.    | comment                                                      |

|-----------------------------|-------|---------|---------|--------------------------------------------------------------|

| $V_{GS}$                    | -16 V | _       | 16 V    | Maximum gate source voltage                                  |

| $V_{\mathrm{DS}}$           | _     | _       | 100 V   | Maximum drain source voltage                                 |

| T <sub>J</sub>              | -55°C | _       | 175°C   | Operating temperature range                                  |

| V <sub>GS(TH)</sub>         | 1.1 V | 1.6 V   | 2.1 V   | Gate source threshold voltage (logic level)                  |

| R <sub>DS(ON)</sub>         | _     | 12.3 mΩ | 15 mΩ   | Drain source on state resistance (T <sub>J</sub> = 25°C)     |

| C <sub>iss</sub>            | _     | 2440 pF | 3170 pF | Input capacitance                                            |

| C <sub>rss(effective)</sub> | -     | 175 pF  | _       | Extracted from plot $C_{rss} = f(V_{DS})$ -> mean value      |

| $V_{ m plateau}$            | _     | 2.6 V   | _       | Extracted from plot $I_D = f(V_{GS}) @ I_{IN,max} + I_{OUT}$ |

#### Automotive front light LED reference design with SEPIC topology

#### System design

| Parameter    | Min. | Тур. | Max.   | comment                                      |

|--------------|------|------|--------|----------------------------------------------|

| $R_{th(JA)}$ | _    | _    | 62 K/W | Thermal resistance from junction to ambient, |

|              |      |      |        | minimal footprint                            |

The OptiMOS<sup>TM</sup> –T2 power transistor IPD60N10S4L-12 offers sufficient drain source voltage capability which was calculated in Eq. 27. Furthermore a logic level device was selected due to the fact that the gate drive voltage sourced by the TLD5099EP is 5 V. For switching transistors the parasitic capacitances are very important because they determine the switching behavior. When choosing a higher value of  $R_{DS(ON)}$  the parasitic capacitances usually reduce in value because less active area is needed. Thus a compromise between switching losses and conduction losses must be made when choosing the switching MOSFET. Another important factor is the thermal performance which is mostly influenced by the package of the device. All these parameters influencing the decision on choosing the MOSFET.

With following parameters of the OptiMOS™ –T2 power transistor IPD60N10S4L-12 the switching times can be approximated:

- R<sub>G</sub> ... 10 Ω

- C<sub>iss</sub> ... 3170 pF

- V<sub>D</sub>... 5 V

- V<sub>GS(IL)</sub>...2.6 V

- V<sub>GS(TH)</sub>...2.1 V

- $V_{\rm S} ... V_{\rm IN,min} + V_{\rm OUT,max} = 35 \text{ V}$

- C<sub>rss</sub> ... 175 pF

$$t_{RI} = R_G * C_{iss} * \ln\left(\frac{V_D - V_{GS(TH)}}{V_D - V_{GS(IL)}}\right) = 10 \Omega * 3170 pF * \ln\left(\frac{5 V - 2.1 V}{5 V - 2.6 V}\right) = 2.8 ns$$

$$t_{FV} = R_G * C_{rss} * \frac{V_S}{V_D - V_{GS(IL)}} = 10 \Omega * 175 pF * \frac{35 V}{5 V - 2.6 V} = 26 ns$$

$$t_{FI} = R_G * C_{iss} * \ln\left(\frac{V_{GS(IL)}}{V_{GS(TH)}}\right) = 10 \Omega * 3170 pF * \ln\left(\frac{2.6 V}{2.1 V}\right) = 3.2 ns$$

$$t_{RV} = R_G * C_{rss} * \frac{V_S}{V_{GS(IL)}} = 10 \Omega * 175 pF * \frac{35 V}{2.6 V} = 24 ns$$

It can be seen that the current rise/fall times are much shorter than the voltage rise/fall times thus, the voltage rise/fall times have a higher contribution to the switching losses. With the known switching times the switching losses can be calculated using Eq. 31.

$$P_{Q,SW} = (V_{IN,min} + V_{OUT,max}) * (I_{IN,max} + I_{OUT}) * \frac{t_{RI} + t_{FV} + t_{FI} + t_{RV}}{2} * f_{SW} =$$

$$(8 V + 27 V) * (3.57 A + 0.9 A) * \frac{2.8 ns + 26 ns + 3.2 ns + 24 ns}{2} * 310 kHz = 1.36 W$$

#### 2.2.2.2 Conduction losses

Conduction losses can be calculated by multiplying the squared RMS current through the MOSFET with its  $R_{DS(ON)}$ . Since the  $R_{DS(ON)}$  of a MOSFET increases with increasing temperature, the maximum  $R_{DS(ON)}$  at maximum

#### Automotive front light LED reference design with SEPIC topology

#### System design

junction temperature can be used for the calculation. The RMS current in the switching MOSFET can be calculated using Eq. 32.

$$I_{Q,RMS} = \sqrt{\frac{1}{T}} \int_{0}^{T} I_{Q1}^{2} * d_{t} \approx \sqrt{\frac{1}{T}} * \int_{0}^{D_{max}*T} (I_{IN,max} + I_{OUT})^{2} * d_{t} \approx (I_{IN,max} + I_{OUT}) * \sqrt{D_{max}}$$

$$Eq. 32$$

$$I_{Q,RMS} \approx (I_{IN,max} + I_{OUT}) * \sqrt{D_{max}} = (3.57 + 0.9) * \sqrt{0.771} = 3.92 A$$

The conduction losses can be calculated using Eq. 33.

$$P_{O,C} = I_{O,RMS}^2 * R_{DS(on),max} = 3.92^2 * 0.02 = 307 \text{ mW}$$

Eq. 33

The total losses found by analytical calculation can then be calculated using Eq. 34:

$$P_{O,total} = P_{O,C} + P_{O,SW} = 0.307 + 1.36 = 1.67 W$$

Eq. 34

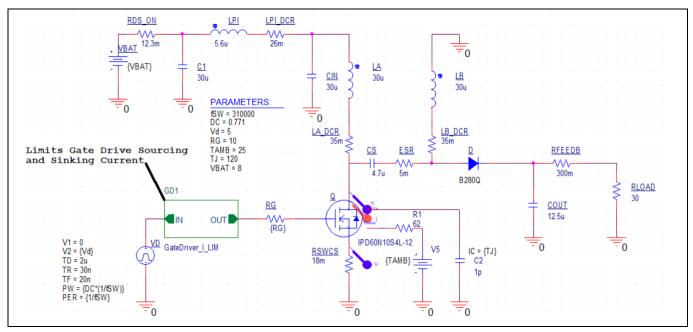

#### 2.2.2.3 Simulated losses

It can be concluded that the switching losses dominate the conduction losses. The calculations in Chapter 2.2.2.2 give an estimation of the total losses and show their influencing parameters. However, a practical approach would be to simulate the losses using SPICE simulation and the MOSFET simulation models provided by Infineon. Furthermore, here also reverse recovery losses can be included. Figure 21 shows the setup to simulate the losses in the switching MOSFET. The main components of the SEPIC power stage are modeled. The simulated circuit operates at following operating conditions:

- · Approximately output power of 25 W

- Duty cycle of 77.1%

- Input voltage of 8 V

- Gate drive voltage of 5 V

- Gate drive sourcing current limited to 380 mA

- Gate drive sinking current limited to 550 mA

- Junction temperature of 120°C

These operating conditions represent a worst-case scenario. Furthermore, the current capability of the gate driver implemented in the TLD5099EP is also modeled.

# Automotive front light LED reference design with SEPIC topology

#### System design

Figure 21 SPICE simulation setup for total losses in switching MOSFET

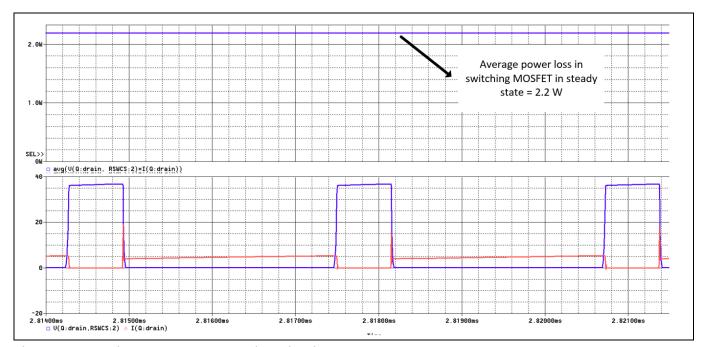

Figure 22 Simulated total losses in switching MOSFET

#### Automotive front light LED reference design with SEPIC topology

#### System design

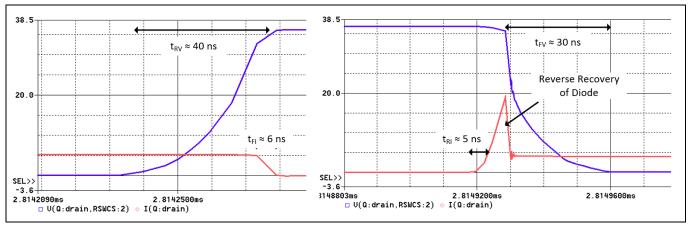

Figure 23 Simulated turn off and turn on transitions

It can be observed in Figure 22 that the simulated total losses are around 2.2 W which is around 0.5 W higher than the analytic calculated results.

This can be mainly explained due to:

- the nonlinear voltage slopes during transition which are due to the nonlinearity of the reverse transfer capacitance, which are assumed to be linear in the analytic switching losses calculation. This results in lower simulated losses than analytic calculated losses

- the included reverse recovery losses generated during turn-on of the MOSFET ( $t_{FV}$ ) which can be clearly seen in Figure 23. These losses increase the simulated losses compared to the analytic calculation

- the difference in analytic and simulated switching times

#### 2.2.2.4 Thermal considerations

To give a prediction of the thermal performance of the switching MOSFET one can monitor the junction temperature of the switching MOSFET in the simulation. However, this would lead to very long simulation times because the time constant of the thermal circuit is much greater than the switching activities. Another approach would be to use the average power dissipation in the device and use the thermal resistance parameters given in the datasheet to calculate a prediction of the temperature of the device. Thermal resistance in the system depends on a number of circumstances such as PCB layout, stackup, amongst others are namely, nearby components, ambient temperature however, it is still possible to do an estimation.

Usually derating strategies are applied when the input voltage or ambient temperature deviate from typical operating conditions of the module. Therefore, the total losses in the switching MOSFET for  $V_{\rm IN,typ}$  will be used for thermal calculations. Following the same approach for the simulations as depicted in Figure 21 the losses in the switching MOSFET for  $V_{\rm IN,typ}$  can be found to be 1.5 W. With a thermal resistance of 62 K/W, which is the maximum value for minimal footprint attachment to the PCB, an ambient temperature of 75°C, where typically derating starts to apply, the following junction temperature can be estimated.

$$T_{J,Q} = T_{AMB} + P_{Q,total} * R_{TH,JA,max} = 75 °C + 1.5 W * 62 \frac{K}{W} = 168 °C$$

Eq. 35

Although the calculated maximum junction is near the maximum junction temperature of the MOSFET which is 175°C, this is with worst-case thermal resistance without any additional cooling elements. Usually this application uses heatsinks thus will improve the thermal behavior.

### Automotive front light LED reference design with SEPIC topology

System design

# 2.2.3 Switching diode

The switching diode in the SEPIC topology faces high current and voltage stress as can be seen in the current and voltage waveforms in Figure 13. Peak current and voltage requirements can be calculated using equation Eq. 36.

$$I_{D,peak} = I_{IN,max} + I_{OUT} + \Delta I_L = 3.57 A + 0.9 A + 0.66 A = 5.13 A$$

$$V_{D,peak} = -(V_{IN,max} + V_{OUT,max}) = -(16 V + 27 V) = -43 V$$

$$V_{D,peak,Trans} = -(V_{IN,Trans,max} + V_{OUT,max}) = -(35 V + 27 V) = -62 V$$

For this design the high voltage switching Schottky diode B280Q from Diodes Incorporated was selected which comprises the following key parameters:

Table 7 B280Q high voltage Schottky diode parameters

| Parameter      | Min.  | Тур. | Max.   | Comment                          |

|----------------|-------|------|--------|----------------------------------|

| $V_{R}$        | -     | 80 V | _      | Working peak reverse voltage     |

| Io             | _     | _    | 2.0 A  | Average rectified output current |

| $V_{F}$        | -     | _    | 0.79 V | Forward voltage drop             |

| T <sub>J</sub> | -65°C | _    | 150°C  | Operating temperature range      |

The average rectified forward current in the switching diode can be found by using Eq. 37.

$$I_{DAVG} = \frac{1}{T} * \int_{D_{max}}^{T} (I_{IN,max} + I_{OUT}) * d_t = \frac{1}{T} * (I_{IN,max} + I_{OUT}) * T * (1 - D_{max})$$

$$I_{D,AVG} = (I_{IN,max} + I_{OUT}) * (1 - D_{max}) = (3.57 + 0.9) * (1 - 0.771) = 1.024 A$$

The worst-case power loss in the diode can be calculated using the average rectified forward current times the maximum forward voltage drop of the diode:

$$P_D = I_{D,AVG} * V_D = 1.024 A * 0.8 V = 819 mW$$

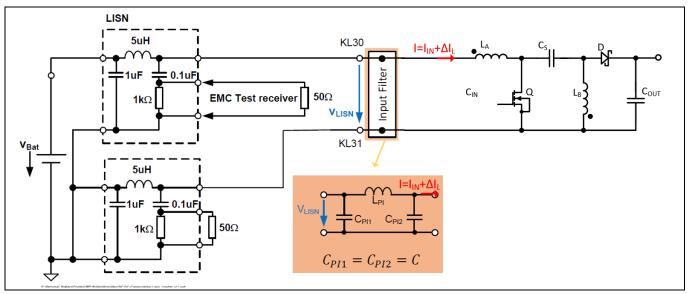

### 2.2.4 Input filter

The input filter in a switched mode power supply is usually required to pass EMC requirements, e.g. CISPR25 Class V limits, and is designed mainly to damp noise in the lower frequency range. The input filter design must already provide enough damping at the first harmonic of the switching frequency. As filter topology, the PI-filter structure is selected. To achieve best performance, the capacitance on each side of the filter structure should be distributed equally, which results in wider low impedant frequency range. The output capacitors of the PI-filter serves as input capacitors to the SEPIC power stage.

#### Automotive front light LED reference design with SEPIC topology

#### System design

Figure 24 EMC measurement setup with input filter and LISN

|                |                  |      |           |         |         |           | ı       | _evel | s in d    | Β(μV    | )    |           |         |      |           |         |

|----------------|------------------|------|-----------|---------|---------|-----------|---------|-------|-----------|---------|------|-----------|---------|------|-----------|---------|

|                |                  | C    | lass      | 5       | Class 4 |           | Class 3 |       | Class 2   |         | 2    | Class 1   |         |      |           |         |

| Service / Band | Frequency<br>MHz | Peak | Quasipeak | Average | Peak    | Quasipeak | Average | Peak  | Quasipeak | Average | Peak | Quasipeak | Average | Peak | Quasipeak | Average |

| BROADC         | AST              |      |           |         |         |           |         |       |           |         |      |           |         |      |           |         |

| LW             | 0,15 to 0,30     | 70   | 57        | 50      | 80      | 67        | 60      | 90    | 77        | 70      | 100  | 87        | 80      | 110  | 97        | 90      |

| MW             | 0,53 to 1,8      | 54   | 41        | 34      | 62      | 49        | 42      | 70    | 57        | 50      | 78   | 65        | 58      | 86   | 73        | 66      |

| SW             | 5,9 to 6,2       | 53   | 40        | 33      | 59      | 46        | 39      | 65    | 52        | 45      | 71   | 58        | 51      | 77   | 64        | 57      |

| FM             | 76 to 108        | 38   | 25        | 18      | 44      | 31        | 24      | 50    | 37        | 30      | 56   | 43        | 36      | 62   | 49        | 42      |

| TV Band I      | 41 to 88         | 34   | _         | 24      | 40      | _         | 30      | 46    | _         | 36      | 52   | _         | 42      | 58   | -         | 48      |

Figure 25 Limits conducted emissions CISPR25

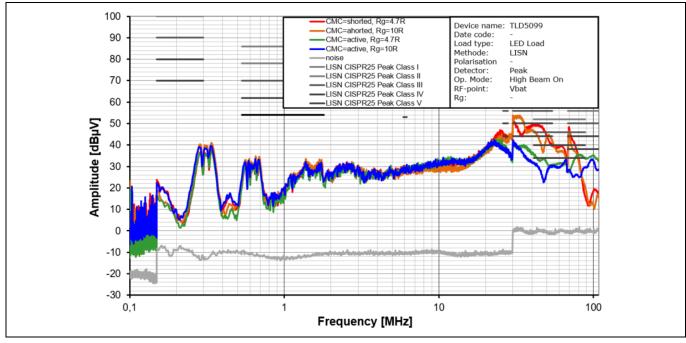

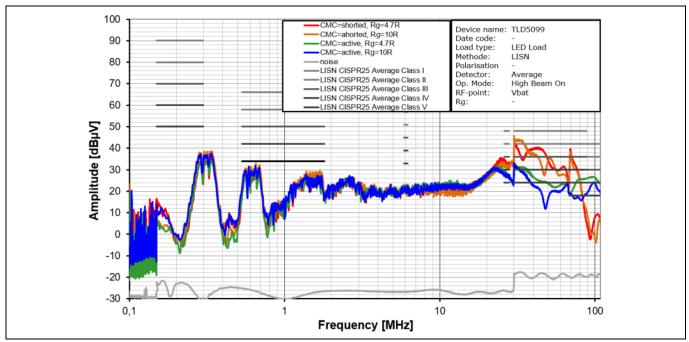

Figure 24 depicts EMC measurement setup with input filter and LISN. The AC part of the input current of the converter, which is the inductor current ripple  $\Delta I_{\rm L}$ , can be related to a voltage variation on the supply side of the PI-filter. This voltage variation is called  $V_{\rm LISN}$ . This voltage variation is directly measured by the EMC receiver via the Line Impedance Stabilization Network (LISN). The relation between ripple current  $\Delta I_{\rm L}$  and the voltage variation at the EMC receiver  $V_{\rm LISN}$  can be found by the filter impedance. The value  $V_{\rm LISN}$  represents the limit at the first harmonic and must not be exceeded. In this design the specific standard CISPR25 is used. The limits for conducted emissions from components and modules are depicted in Figure 25. Since a switched mode power supply is a continuous and small band disturber the average and peak detector will measure approximately the same amplitude, thus the average limit must be applied since this is the lower limit. At the MW band starting at 530 kHz the limit for the average detector is 34 dB $\mu$ V which is 50  $\mu$ V which can be used as  $V_{\rm LISN}$  for the calculations.

#### Automotive front light LED reference design with SEPIC topology

#### System design

A step by step instruction for calculating the PI-filter elements is given:

- 1) Calculate input current ripple:  $\rightarrow \Delta I_L = 0.93 A (@V_{IN,typ})$

- 2) Select value for PI-filter inductor, for example:  $\rightarrow L_{PI} = 5.6 \mu H$

3) Calculate required minimum capacitance:

$$C = \sqrt{\frac{\Delta I_L}{V_{LISN}} * \frac{1}{\omega^3 * L_{PI}}} = \sqrt{\frac{0.93}{50\mu} * \frac{1}{(2*\pi*310000)^3*10\mu}} = 15.9 \ \mu F$$

- 4) Select next available capacitor:  $\rightarrow C_{PI} \ge C \rightarrow C_{PI} = 3x10\mu F \approx 30\mu F$

- 5) Calculate PI-filter resonance frequency:  $f_{PI,res} = \frac{1}{2*\pi*\sqrt{\frac{L_{PI}*C_{PI}}{2}}} = \frac{1}{2*\pi*\sqrt{\frac{5.6\mu*30\mu}{2}}} = 17.3~kHz$

- 6) Check that the resonance frequency of the PI-filter is at least 1 decade lower than the switching frequency:  $\frac{f_{SW}}{f_{PI,res}} \ge 10 \rightarrow \frac{300k}{17.3k} \approx 17$

- 7) Verify filter behavior by emission test. If emission is above the limit line increase capacitor or inductor:  $\rightarrow L_{needed} = L_{existing} * 10^{\frac{\Delta dB}{20}} \rightarrow C_{needed} = C_{existing} * 10^{\frac{\Delta dB}{40}}$

$$Z_{Filter} = \frac{V_{LISN}}{\Delta I_L} \approx \frac{1}{-j\omega^3 C^2 L} \rightarrow C \approx \frac{1}{\sqrt{-j\omega^3 L * Z_{Filter}}} \approx \sqrt{\frac{\Delta I_L}{V_{LISN}} * \frac{1}{\omega^3 * L}}$$

Eq. 39

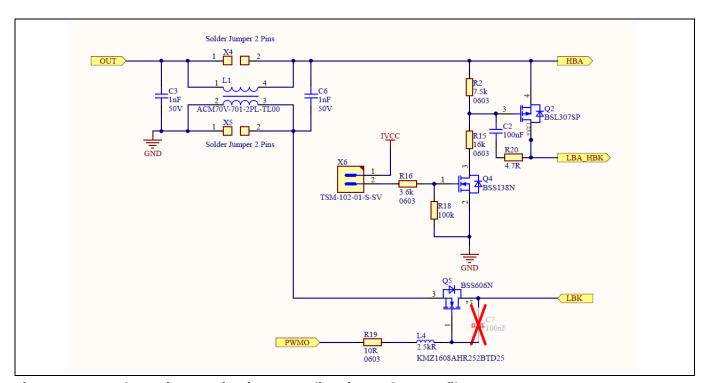

# 2.3 High beam activation, PWM dimming and output filter

Figure 26 Schematic HB activation, PWM dimming and output filter

As already discussed, one DC-DC channel should drive two light functions, the HB and the LB. In a normal driving situation only the LB would be active. In certain situations, the HB is activated additionally. The activation is accomplished using a circuit given in Figure 26. When jumper X6 is open the small signal p-channel MOSFET BSL307SP Q2 is off since Q4 is not conducting, thus the high beam is activated because it is not

#### Automotive front light LED reference design with SEPIC topology

#### System design

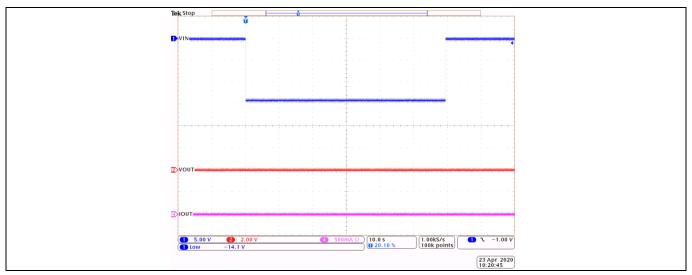

shorted by Q2. Vice versa, when the jumper X6 is closed, the HB turns off accordingly. The reverse transfer capacitance  $C_{rss}$  of Q2 is increased by placing an additional capacitor C2 between the gate and the drain of the device. This will increase the voltage rise and fall times to a couple of milliseconds to decrease current overshoot during the transient between activating and deactivating the high beam, see Figure 44. Q5 is used as PWM dimming MOSFET and is controlled by the TLD5099EP.

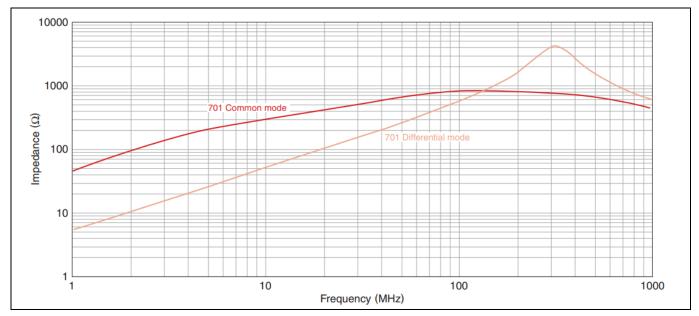

Furthermore, a CMC is used at the output to damp common mode noise originating mainly by capacitive coupling with the reference plane. The CMC is placed at the output since a lower current rating is required and therefore saves cost. The common mode and differential mode impedance of the CMC is depicted in Figure 27.

Figure 27 Common mode and differential mode impedance vs. frequency for ACM70V-701-2PL-TL00 [5]

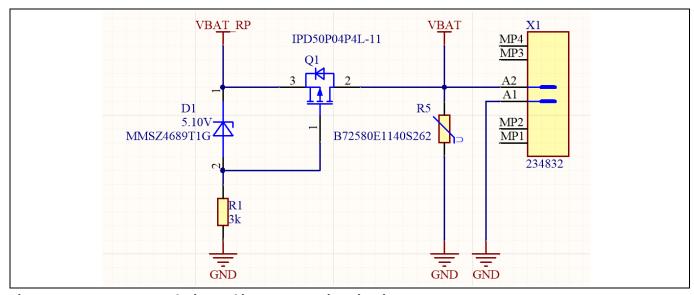

# 2.4 Reverse polarity and input protection

Figure 28 Reverse polarity and input protection circuit

#### Automotive front light LED reference design with SEPIC topology

#### System design

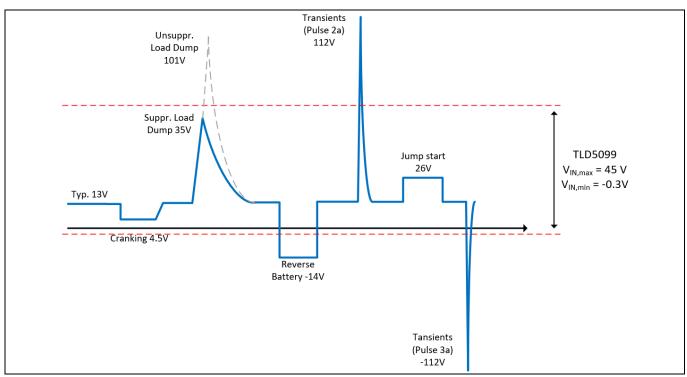

Systems in the automotive environment face challenging requirements. Several international or OEM specific standards are in place, with which the system design needs to comply. The reverse polarity and input protection circuit protects the downstream electronics mainly against transients along the supply line. Figure 29 depicts some possible transients along the battery supply line. Depending on the specific standard or requirements of the OEM the size and shape of these transients vary.

Figure 29 Transients along the supply line in an automotive battery supply

As an example, the maximum input voltage range of the TLD5099EP is marked. It can be seen that for reverse polarity; unsuppressed load dump and transients originating from inductive switching, that additional protection circuitry is necessary. However, the input filter will also damp these pulses to a certain degree. It can be concluded that for the reverse polarity case a protection circuit must be implemented, since this is a static case. For a possible unsuppressed load dump and transients due to inductive switching a TVS diode is typically used. The input protection therefore should ensure a maximum voltage present for the downstream electronics ranging from 0 V up to 40 V. The protection level of 0 V to 40 V originates from the present downstream electronic components' ratings with a safety margin. However, devices like the TLD5099EP can also withstand certain pulses without any additional protection.

# 2.4.1 Ceramic transient voltage suppressor

As input protection a CTVS from TDK (CT1812S14BAUTOG) got selected. These devices are voltage dependent resistors with a symmetrical V/I characteristic whose resistance decreases with increasing voltage. Connected in parallel with the electronic circuit that is to be guarded, the CTVS threshold value prevent any further rise in the transient overvoltage. The main advantages of CTVS are:

- No temperature derating up to 150°C

- Excellent surge current handling capability

- · Low response time

- Bidirectional characteristic

#### Automotive front light LED reference design with SEPIC topology

#### System design

Table 8 Important parameters CTVS CT1812S14BAUTOG

| $V_{RMS,max}$ | V <sub>DC,max</sub> | <b>W</b> <sub>max</sub> | W <sub>LD</sub> (10 pulses) | P <sub>diss,max</sub> | V <sub>clamp,max</sub> |

|---------------|---------------------|-------------------------|-----------------------------|-----------------------|------------------------|

| 14 V          | 16 V                | 2400 mJ                 | 6000 mJ                     | 15 mW                 | 40 V                   |

Table 8 summarizes the most important parameters of the CTVS CT1812S14BAUTOG. A step by step explanation how to select the right CTVS is given in the following section based on a load dump pulse with a peak voltage of 35 V and a source impedance of 1  $\Omega$ .

#### Step 1) Maximum operating voltage $V_{RMS,max}$ and $V_{DC,max}$

To obtain a low protection level (clamping voltage), an operating voltage  $V_{DC,max}$  close to the maximum operating voltage should be selected. Maximum DC operating voltage for this design is 16 V.

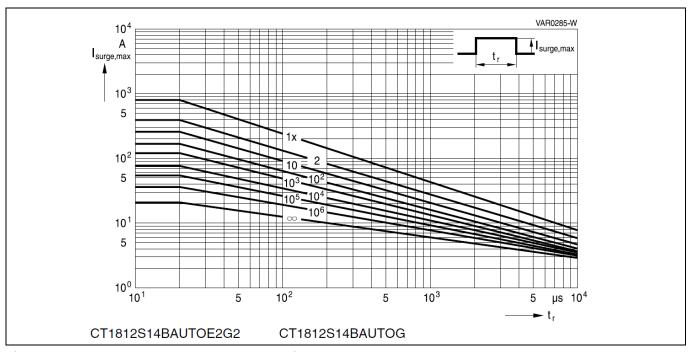

#### Step 2) Maximum surge current I<sub>Surge,max</sub>

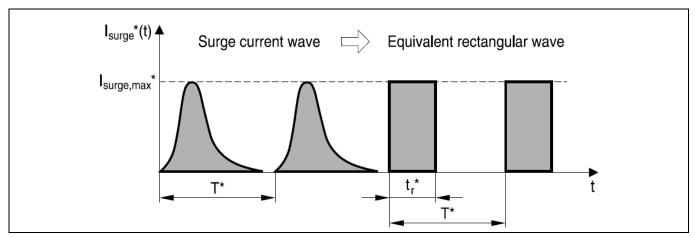

The maximum surge current in the device is dependent on the applied test pulse and the source impedance. Figure 30 depicts the transformation of the surge pulse.

Figure 30 Equivalent rectangular surge current

A practical approach to determine the equivalent rectangular wave for a specific transient pulse would be a SPICE simulation, where TDK provides simulation models for the CTVS.

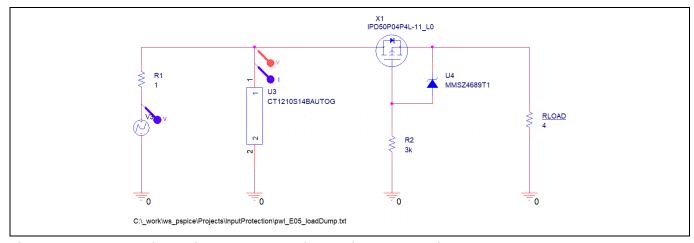

Figure 31 SPICE simulation reverse polarity and input protection

### Automotive front light LED reference design with SEPIC topology

#### System design

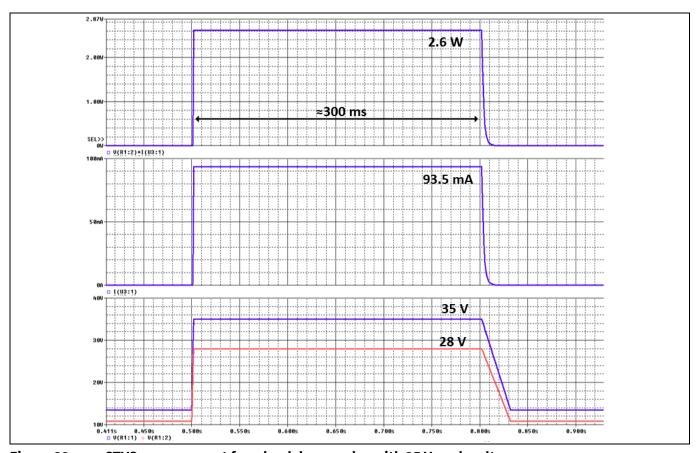

Figure 32 CTVS surge current for a load dump pulse with 35 V peak voltage

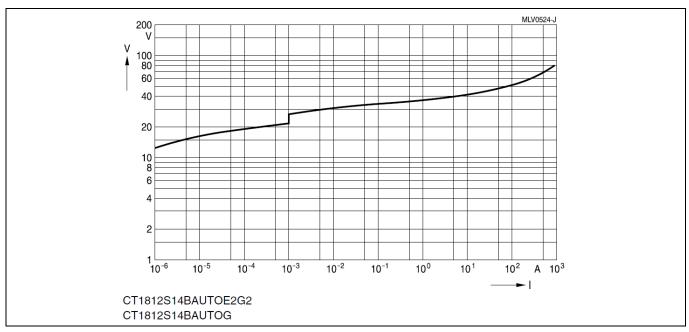

Figure 32 depicts the simulation results for the surge current of a load dump pulse with a peak voltage of 35 V and a source impedance of 1  $\Omega$  for the chosen CTVS (CT1812S14BAUTOG). It can be seen that for this test pulse the surge current is approximately in a rectangular shape and therefore needs no transformation. From the simulation  $I_{\text{Surge,max}} = 93.5 \text{ mA}$  and  $t_r = 300 \text{ ms}$  can be determined.

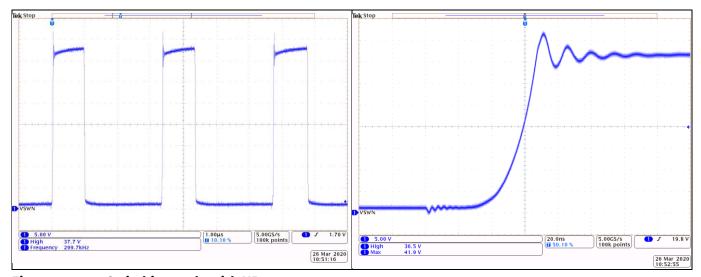

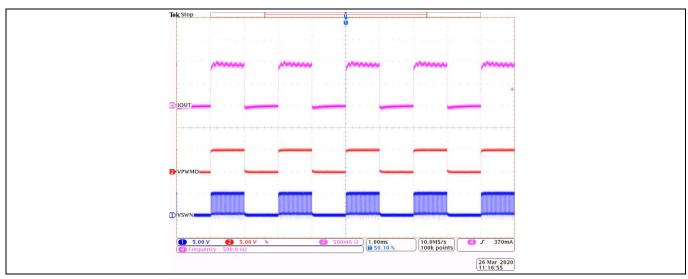

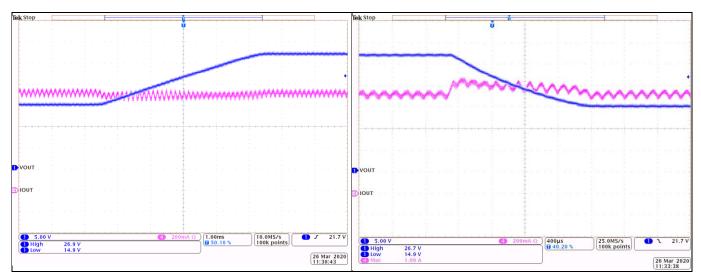

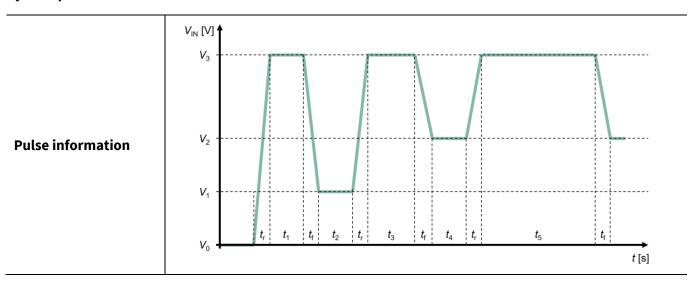

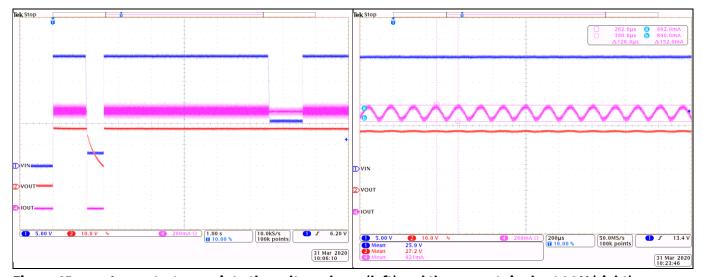

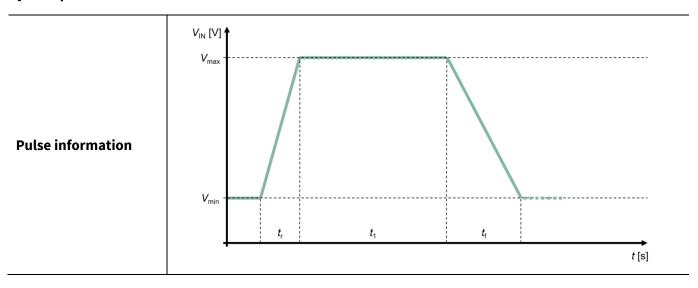

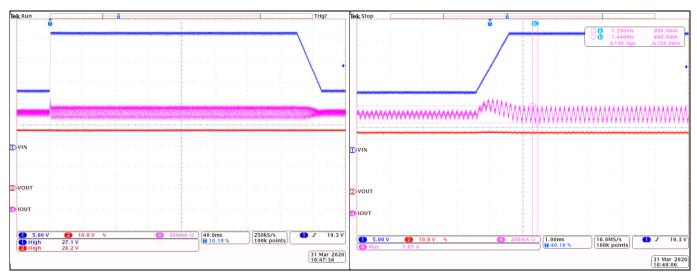

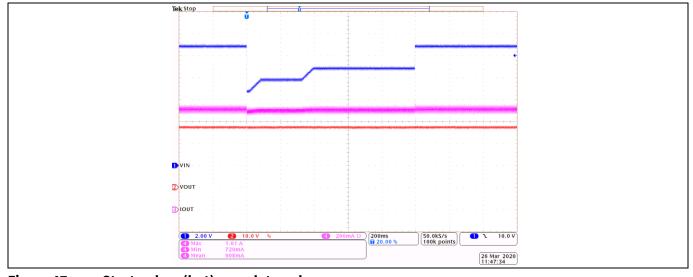

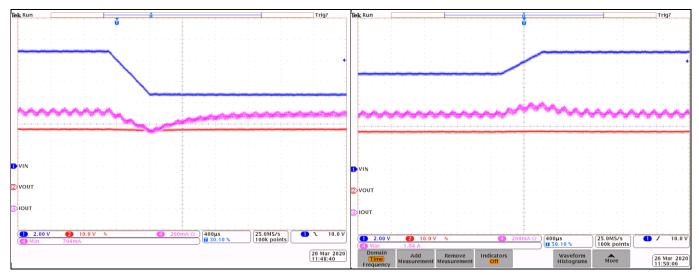

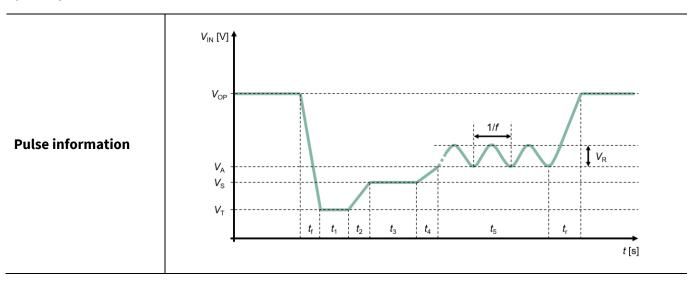

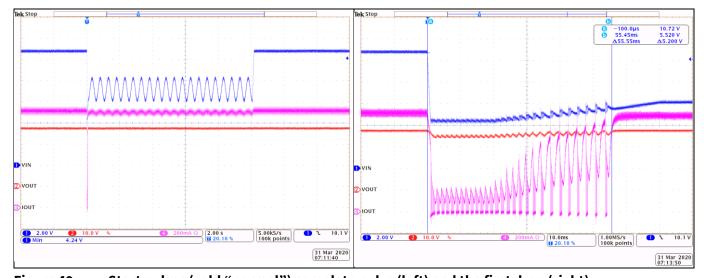

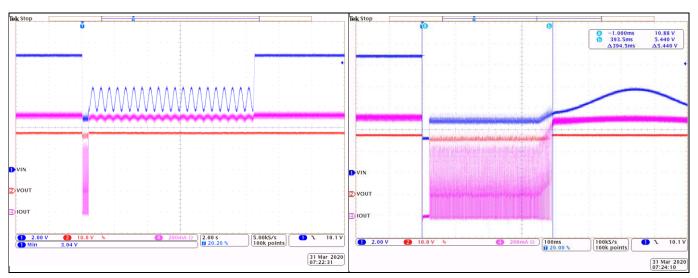

When the equivalent rectangular wave is known ( $t_r$  and  $I_{surge,max}$ ) a graph is given from which the maximum ratings can be seen which is shown for the chosen CTVS (CT1812S14BAUTOG) in Table 8. Although the time scale ends at 10 ms one can interpolate up to 300 ms and conclude that 93.5 mA will be below the maximum rating.