TLE94x1_DEFINES.h File Reference

Main header declaration file for TLE94x1 SBC family device. More...

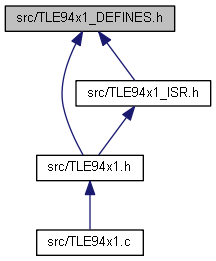

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | SBC_M_S_CTRL (0b00000001U) |

| Control register address. | |

| #define | SBC_HW_CTRL_0 (0b00000010U) |

| Control register address. | |

| #define | SBC_WD_CTRL (0b00000011U) |

| Control register address. | |

| #define | SBC_BUS_CTRL_0 (0b00000100U) |

| Control register address. | |

| #define | SBC_WK_CTRL_0 (0b00000110U) |

| Control register address. | |

| #define | SBC_WK_CTRL_1 (0b00000111U) |

| Control register address. | |

| #define | SBC_WK_PUPD_CTRL (0b00001000U) |

| Control register address. | |

| #define | SBC_BUS_CTRL_3 (0b00001011U) |

| Control register address. | |

| #define | SBC_TIMER_CTRL (0b00001100U) |

| Control register address. | |

| #define | SBC_HW_CTRL_1 (0b00001110U) |

| Control register address. | |

| #define | SBC_HW_CTRL_2 (0b00001111U) |

| Control register address. | |

| #define | SBC_GPIO_CTRL (0b00010111U) |

| Control register address. | |

| #define | SBC_PWM_CTRL (0b00011000U) |

| Control register address. | |

| #define | SBC_PWM_FREQ_CTRL (0b00011100U) |

| Control register address. | |

| #define | SBC_HW_CTRL_3 (0b00011101U) |

| Control register address. | |

| #define | SBC_SYS_STATUS_CTRL_0 (0b00011110U) |

| Control register address. | |

| #define | SBC_SYS_STATUS_CTRL_1 (0b00011111U) |

| Control register address. | |

| #define | SBC_SWK_CTRL (0b00100000U) |

| Selective wake register address. | |

| #define | SBC_SWK_BTL0_CTRL (0b00100001U) |

| Selective wake register address. | |

| #define | SBC_SWK_BTL1_CTRL (0b00100010U) |

| Selective wake register address. | |

| #define | SBC_SWK_ID3_CTRL (0b00100011U) |

| Selective wake register address. | |

| #define | SBC_SWK_ID2_CTRL (0b00100100U) |

| Selective wake register address. | |

| #define | SBC_SWK_ID1_CTRL (0b00100101U) |

| Selective wake register address. | |

| #define | SBC_SWK_ID0_CTRL (0b00100110U) |

| Selective wake register address. | |

| #define | SBC_SWK_MASK_ID3_CTRL (0b00100111U) |

| Selective wake register address. | |

| #define | SBC_SWK_MASK_ID2_CTRL (0b00101000U) |

| Selective wake register address. | |

| #define | SBC_SWK_MASK_ID1_CTRL (0b00101001U) |

| Selective wake register address. | |

| #define | SBC_SWK_MASK_ID0_CTRL (0b00101010U) |

| Selective wake register address. | |

| #define | SBC_SWK_DLC_CTRL (0b00101011U) |

| Selective wake register address. | |

| #define | SBC_SWK_DATA7_CTRL (0b00101100U) |

| Selective wake register address. | |

| #define | SBC_SWK_DATA6_CTRL (0b00101101U) |

| Selective wake register address. | |

| #define | SBC_SWK_DATA5_CTRL (0b00101110U) |

| Selective wake register address. | |

| #define | SBC_SWK_DATA4_CTRL (0b00101111U) |

| Selective wake register address. | |

| #define | SBC_SWK_DATA3_CTRL (0b00110000U) |

| Selective wake register address. | |

| #define | SBC_SWK_DATA2_CTRL (0b00110001U) |

| Selective wake register address. | |

| #define | SBC_SWK_DATA1_CTRL (0b00110010U) |

| Selective wake register address. | |

| #define | SBC_SWK_DATA0_CTRL (0b00110011U) |

| Selective wake register address. | |

| #define | SBC_SWK_CAN_FD_CTRL (0b00110100U) |

| Selective wake register address. | |

| #define | SBC_SWK_OSC_TRIM_CTRL (0b00111000U) |

| Selective wake register address. | |

| #define | SBC_SWK_OPT_CTRL (0b00111001U) |

| Selective wake register address. | |

| #define | SBC_SWK_OSC_CAL_H_STAT (0b00111010U) |

| Selective wake register address. | |

| #define | SBC_SWK_OSC_CAL_L_STAT (0b00111011U) |

| Selective wake register address. | |

| #define | SBC_SWK_CDR_CTRL1 (0b00111100U) |

| Selective wake register address. | |

| #define | SBC_SWK_CDR_CTRL2 (0b00111101U) |

| Selective wake register address. | |

| #define | SBC_SWK_CDR_LIMIT_HIGH_CTRL (0b00111110U) |

| Selective wake register address. | |

| #define | SBC_SWK_CDR_LIMIT_LOW_CTRL (0b00111111U) |

| Selective wake register address. | |

| #define | SBC_SUP_STAT_1 (0b01000000U) |

| Status register address. | |

| #define | SBC_SUP_STAT_0 (0b01000001U) |

| Status register address. | |

| #define | SBC_THERM_STAT (0b01000010U) |

| Status register address. | |

| #define | SBC_DEV_STAT (0b01000011U) |

| Status register address. | |

| #define | SBC_BUS_STAT (0b01000100U) |

| Status register address. | |

| #define | SBC_WK_STAT_0 (0b01000110U) |

| Status register address. | |

| #define | SBC_WK_STAT_1 (0b01000111U) |

| Status register address. | |

| #define | SBC_WK_LVL_STAT (0b01001000U) |

| Status register address. | |

| #define | SBC_GPIO_OC_STAT (0b01010100U) |

| Status register address. | |

| #define | SBC_GPIO_OL_STAT (0b01010101U) |

| Status register address. | |

| #define | SBC_SWK_STAT (0b01110000U) |

| Selective wake status register address. | |

| #define | SBC_SWK_ECNT_STAT (0b01110001U) |

| Selective wake status register address. | |

| #define | SBC_SWK_CDR_STAT1 (0b01110010U) |

| Selective wake status register address. | |

| #define | SBC_SWK_CDR_STAT2 (0b01110011U) |

| Selective wake status register address. | |

| #define | SBC_FAM_PROD_STAT (0b01111110U) |

| Selective wake status register address. | |

| #define | SBC_M_S_CTRL_MODE_Pos (6U) |

| Control register bit position. | |

| #define | SBC_M_S_CTRL_MODE_Msk (0b11000000U) |

| Control register bit mask. | |

| #define | SBC_M_S_CTRL_VCC2_ON_Pos (3U) |

| Control register bit position. | |

| #define | SBC_M_S_CTRL_VCC2_ON_Msk (0b00011000U) |

| Control register bit mask. | |

| #define | SBC_M_S_CTRL_VCC1_OV_RST_Pos (2U) |

| Control register bit position. | |

| #define | SBC_M_S_CTRL_VCC1_OV_RST_Msk (0b00000100U) |

| Control register bit mask. | |

| #define | SBC_M_S_CTRL_VCC1_RT_Pos (0U) |

| Control register bit position. | |

| #define | SBC_M_S_CTRL_VCC1_RT_Msk (0b00000011U) |

| Control register bit mask. | |

| #define | SBC_HW_CTRL_0_SOFT_RESET_RST_Pos (6U) |

| Control register bit position. | |

| #define | SBC_HW_CTRL_0_SOFT_RESET_RST_Msk (0b01000000U) |

| Control register bit mask. | |

| #define | SBC_HW_CTRL_0_FO_ON_Pos (5U) |

| Control register bit position. | |

| #define | SBC_HW_CTRL_0_FO_ON_Msk (0b00100000U) |

| Control register bit mask. | |

| #define | SBC_HW_CTRL_0_CP_EN_Pos (2U) |

| Control register bit position. | |

| #define | SBC_HW_CTRL_0_CP_EN_Msk (0b00000100U) |

| Control register bit mask. | |

| #define | SBC_HW_CTRL_0_CFG1_Pos (0U) |

| Control register bit position. | |

| #define | SBC_HW_CTRL_0_CFG1_Msk (0b00000001U) |

| Control register bit mask. | |

| #define | SBC_WD_CTRL_CHECKSUM_Pos (7U) |

| Control register bit position. | |

| #define | SBC_WD_CTRL_CHECKSUM_Msk (0b10000000U) |

| Control register bit mask. | |

| #define | SBC_WD_CTRL_WD_STM_EN_0_Pos (6U) |

| Control register bit position. | |

| #define | SBC_WD_CTRL_WD_STM_EN_0_Msk (0b01000000U) |

| Control register bit mask. | |

| #define | SBC_WD_CTRL_WD_WIN_Pos (5U) |

| Control register bit position. | |

| #define | SBC_WD_CTRL_WD_WIN_Msk (0b00100000U) |

| Control register bit mask. | |

| #define | SBC_WD_CTRL_WD_EN_WK_BUS_Pos (4U) |

| Control register bit position. | |

| #define | SBC_WD_CTRL_WD_EN_WK_BUS_Msk (0b00010000U) |

| Control register bit mask. | |

| #define | SBC_WD_CTRL_WD_TIMER_Pos (0U) |

| Control register bit position. | |

| #define | SBC_WD_CTRL_WD_TIMER_Msk (0b00000111U) |

| Control register bit mask. | |

| #define | SBC_BUS_CTRL_0_CAN_Pos (0U) |

| Control register bit position. | |

| #define | SBC_BUS_CTRL_0_CAN_Msk (0b00000111U) |

| Control register bit mask. | |

| #define | SBC_WK_CTRL_0_TIMER_WK_EN_Pos (6U) |

| Control register bit position. | |

| #define | SBC_WK_CTRL_0_TIMER_WK_EN_Msk (0b01000000U) |

| Control register bit mask. | |

| #define | SBC_WK_CTRL_0_WD_STM_EN_1_Pos (2U) |

| Control register bit position. | |

| #define | SBC_WK_CTRL_0_WD_STM_EN_1_Msk (0b00000100U) |

| Control register bit mask. | |

| #define | SBC_WK_CTRL_1_INT_GLOBAL_Pos (7U) |

| Control register bit position. | |

| #define | SBC_WK_CTRL_1_INT_GLOBAL_Msk (0b10000000U) |

| Control register bit mask. | |

| #define | SBC_WK_CTRL_1_WK_MEAS_Pos (5U) |

| Control register bit position. | |

| #define | SBC_WK_CTRL_1_WK_MEAS_Msk (0b00100000U) |

| Control register bit mask. | |

| #define | SBC_WK_CTRL_1_WK_EN_Pos (0U) |

| Control register bit position. | |

| #define | SBC_WK_CTRL_1_WK_EN_Msk (0b00000001U) |

| Control register bit mask. | |

| #define | SBC_WK_PUPD_CTRL_GPIO_WK_PUPD_Pos (6U) |

| Control register bit position. | |

| #define | SBC_WK_PUPD_CTRL_GPIO_WK_PUPD_Msk (0b11000000U) |

| Control register bit mask. | |

| #define | SBC_WK_PUPD_CTRL_WK_PUPD_Pos (0U) |

| Control register bit position. | |

| #define | SBC_WK_PUPD_CTRL_WK_PUPD_Msk (0b00000011U) |

| Control register bit mask. | |

| #define | SBC_BUS_CTRL_3_CAN_FLASH_Pos (4U) |

| Control register bit position. | |

| #define | SBC_BUS_CTRL_3_CAN_FLASH_Msk (0b00010000U) |

| Control register bit mask. | |

| #define | SBC_TIMER_CTRL_TIMER_ON_Pos (4U) |

| Control register bit position. | |

| #define | SBC_TIMER_CTRL_TIMER_ON_Msk (0b01110000U) |

| Control register bit mask. | |

| #define | SBC_TIMER_CTRL_TIMER_PER_Pos (0U) |

| Control register bit position. | |

| #define | SBC_TIMER_CTRL_TIMER_PER_Msk (0b00001111U) |

| Control register bit mask. | |

| #define | SBC_HW_CTRL_1_RSTN_HYS_Pos (7U) |

| Control register bit position. | |

| #define | SBC_HW_CTRL_1_RSTN_HYS_Msk (0b10000000U) |

| Control register bit mask. | |

| #define | SBC_HW_CTRL_1_TSD2_DEL_Pos (5U) |

| Control register bit position. | |

| #define | SBC_HW_CTRL_1_TSD2_DEL_Msk (0b00100000U) |

| Control register bit mask. | |

| #define | SBC_HW_CTRL_1_RSTN_DEL_Pos (4U) |

| Control register bit position. | |

| #define | SBC_HW_CTRL_1_RSTN_DEL_Msk (0b00010000U) |

| Control register bit mask. | |

| #define | SBC_HW_CTRL_1_CFG_LOCK_0_Pos (3U) |

| Control register bit position. | |

| #define | SBC_HW_CTRL_1_CFG_LOCK_0_Msk (0b00001000U) |

| Control register bit mask. | |

| #define | SBC_HW_CTRL_2_2MHZ_FREQ_Pos (5U) |

| Control register bit position. | |

| #define | SBC_HW_CTRL_2_2MHZ_FREQ_Msk (0b11100000U) |

| Control register bit mask. | |

| #define | SBC_HW_CTRL_2_I_PEAK_TH_Pos (4U) |

| Control register bit position. | |

| #define | SBC_HW_CTRL_2_I_PEAK_TH_Msk (0b00010000U) |

| Control register bit mask. | |

| #define | SBC_HW_CTRL_2_SS_MOD_FR_Pos (2U) |

| Control register bit position. | |

| #define | SBC_HW_CTRL_2_SS_MOD_FR_Msk (0b00001100U) |

| Control register bit mask. | |

| #define | SBC_HW_CTRL_2_CFG_LOCK_1_Pos (0U) |

| Control register bit position. | |

| #define | SBC_HW_CTRL_2_CFG_LOCK_1_Msk (0b00000001U) |

| Control register bit mask. | |

| #define | SBC_GPIO_CTRL_GPIO_Pos (0U) |

| Control register bit position. | |

| #define | SBC_GPIO_CTRL_GPIO_Msk (0b00000111U) |

| Control register bit mask. | |

| #define | SBC_PWM_CTRL_PWM_DC_Pos (0U) |

| #define | SBC_PWM_CTRL_PWM_DC_Msk (0b11111111U) |

| #define | SBC_PWM_FREQ_CTRL_PWM_FREQ_Pos (0U) |

| Control register bit position. | |

| #define | SBC_PWM_FREQ_CTRL_PWM_FREQ_Msk (0b00000011U) |

| Control register bit mask. | |

| #define | SBC_HW_CTRL_3_TSD_THR_Pos (2U) |

| Control register bit position. | |

| #define | SBC_HW_CTRL_3_TSD_THR_Msk (0b00000100U) |

| Control register bit mask. | |

| #define | SBC_HW_CTRL_3_ICC1_LIM_ADJ_Pos (0U) |

| Control register bit position. | |

| #define | SBC_HW_CTRL_3_ICC1_LIM_ADJ_Msk (0b00000011U) |

| Control register bit mask. | |

| #define | SBC_SYS_STATUS_CTRL_0_SYS_STAT_L_Pos (0U) |

| Control register bit position. | |

| #define | SBC_SYS_STATUS_CTRL_0_SYS_STAT_L_Msk (0b11111111U) |

| Control register bit mask. | |

| #define | SBC_SYS_STATUS_CTRL_0_SYS_STAT_H_Pos (0U) |

| Control register bit position. | |

| #define | SBC_SYS_STATUS_CTRL_0_SYS_STAT_H_Msk (0b11111111U) |

| Control register bit mask. | |

| #define | SBC_SWK_CTRL_OSC_CAL_Pos (7U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_CTRL_OSC_CAL_Msk (0b10000000U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_CTRL_TRIM_EN_Pos (5U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_CTRL_TRIM_EN_Msk (0b01100000U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_CTRL_CANTO_MASK_Pos (4U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_CTRL_CANTO_MASK_Msk (0b00010000U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_CTRL_CFG_VAL_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_CTRL_CFG_VAL_Msk (0b00000001U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_BTL0_CTRL_TBIT_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_BTL0_CTRL_TBIT_Msk (0b11111111U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_BTL1_CTRL_SP_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_BTL1_CTRL_SP_Msk (0b00111111U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_ID3_CTRL_ID28_21_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_ID3_CTRL_ID28_21_Msk (0b11111111U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_ID2_CTRL_ID20_13_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_ID2_CTRL_ID20_13_Msk (0b11111111U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_ID1_CTRL_ID12_5_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_ID1_CTRL_ID12_5_Msk (0b11111111U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_ID0_CTRL_ID4_0_Pos (2U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_ID0_CTRL_ID4_0_Msk (0b01111100U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_ID0_CTRL_RTR_Pos (1U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_ID0_CTRL_RTR_Msk (0b00000010U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_ID0_CTRL_IDE_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_ID0_CTRL_IDE_Msk (0b00000001U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_MASK_ID3_CTRL_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_MASK_ID3_CTRL_Msk (0b11111111U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_MASK_ID2_CTRL_MASK_ID20_13_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_MASK_ID2_CTRL_MASK_ID20_13_Msk (0b11111111U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_MASK_ID1_CTRL_MASK_ID12_5_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_MASK_ID1_CTRL_MASK_ID12_5_Msk (0b11111111U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_MASK_ID0_CTRL_MASK_ID4_0_Pos (2U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_MASK_ID0_CTRL_MASK_ID4_0_Msk (0b01111100U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_DLC_CTRL_DLC_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_DLC_CTRL_DLC_Msk (0b00001111U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_DATA7_CTRL_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_DATA7_CTRL_Msk (0b11111111U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_DATA6_CTRL_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_DATA6_CTRL_Msk (0b11111111U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_DATA5_CTRL_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_DATA5_CTRL_Msk (0b11111111U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_DATA4_CTRL_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_DATA4_CTRL_Msk (0b11111111U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_DATA3_CTRL_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_DATA3_CTRL_Msk (0b11111111U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_DATA2_CTRL_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_DATA2_CTRL_Msk (0b11111111U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_DATA1_CTRL_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_DATA1_CTRL_Msk (0b11111111U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_DATA0_CTRL_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_DATA0_CTRL_Msk (0b11111111U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_CAN_FD_CTRL_DIS_ERR_CNT_Pos (5U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_CAN_FD_CTRL_DIS_ERR_CNT_Msk (0b00100000U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_CAN_FD_CTRL_RX_FILT_BYP_Pos (4U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_CAN_FD_CTRL_RX_FILT_BYP_Msk (0b00010000U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_CAN_FD_CTRL_FD_FILTER_Pos (1U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_CAN_FD_CTRL_FD_FILTER_Msk (0b00001110U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_CAN_FD_CTRL_CAN_FD_EN_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_CAN_FD_CTRL_CAN_FD_EN_Msk (0b00000001U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_OSC_TRIM_CTRL_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_OSC_TRIM_CTRL_Msk (0b01111111U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_OPT_CTRL_RX_WK_SEL_Pos (7U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_OPT_CTRL_RX_WK_SEL_Msk (0b10000000U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_OSC_CAL_H_STAT_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_OSC_CAL_H_STAT_Msk (0b11111111U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_OPT_CAL_L_STAT_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_OPT_CAL_L_STAT_Msk (0b11111111U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_CDR_CTRL1_SEL_FILT_Pos (2U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_CDR_CTRL1_SEL_FILT_Msk (0b00001100U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_CDR_CTRL1_CDR_EN_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_CDR_CTRL1_CDR_EN_Msk (0b00000001U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_CDR_CTRL2_SEL_OSC_CLK_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_CDR_CTRL2_SEL_OSC_CLK_Msk (0b00000011U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_CDR_LIMIT_HIGH_CTRL_CDR_LIM_H_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_CDR_LIMIT_HIGH_CTRL_CDR_LIM_H_Msk (0b11111111U) |

| Selective wake register bit mask. | |

| #define | SBC_SWK_CDR_LIMIT_LOW_CTRL_CDR_LIM_L_Pos (0U) |

| Selective wake register bit position. | |

| #define | SBC_SWK_CDR_LIMIT_LOW_CTRL_CDR_LIM_L_Msk (0b11111111U) |

| Selective wake register bit mask. | |

| #define | SBC_SUP_STAT_1_VS_UV_Pos (6U) |

| General status register bit position. | |

| #define | SBC_SUP_STAT_1_VS_UV_Msk (0b01000000U) |

| General status register bit mask. | |

| #define | SBC_SUP_STAT_1_VS_OV_Pos (5U) |

| General status register bit position. | |

| #define | SBC_SUP_STAT_1_VS_OV_Msk (0b00100000U) |

| General status register bit mask. | |

| #define | SBC_SUP_STAT_1_VCC1_OV_Pos (1U) |

| General status register bit position. | |

| #define | SBC_SUP_STAT_1_VCC1_OV_Msk (0b00000010U) |

| General status register bit mask. | |

| #define | SBC_SUP_STAT_1_VCC1_WARN_Pos (0U) |

| General status register bit position. | |

| #define | SBC_SUP_STAT_1_VCC1_WARN_Msk (0b00000001U) |

| General status register bit mask. | |

| #define | SBC_SUP_STAT_0_POR_Pos (7U) |

| General status register bit position. | |

| #define | SBC_SUP_STAT_0_POR_Msk (0b10000000U) |

| General status register bit mask. | |

| #define | SBC_SUP_STAT_0_VCC2_OT_Pos (4U) |

| General status register bit position. | |

| #define | SBC_SUP_STAT_0_VCC2_OT_Msk (0b00010000U) |

| General status register bit mask. | |

| #define | SBC_SUP_STAT_0_VCC2_UV_Pos (3U) |

| General status register bit position. | |

| #define | SBC_SUP_STAT_0_VCC2_UV_Msk (0b00001000U) |

| General status register bit mask. | |

| #define | SBC_SUP_STAT_0_VCC1_SC_Pos (2U) |

| General status register bit position. | |

| #define | SBC_SUP_STAT_0_VCC1_SC_Msk (0b00000100U) |

| General status register bit mask. | |

| #define | SBC_SUP_STAT_0_VCC1_UV_Pos (0U) |

| General status register bit position. | |

| #define | SBC_SUP_STAT_0_VCC1_UV_Msk (0b00000001U) |

| General status register bit mask. | |

| #define | SBC_THERM_STAT_TSD2_SAFE_Pos (3U) |

| General status register bit position. | |

| #define | SBC_THERM_STAT_TSD2_SAFE_Msk (0b00001000U) |

| General status register bit mask. | |

| #define | SBC_THERM_STAT_TSD2_Pos (2U) |

| General status register bit position. | |

| #define | SBC_THERM_STAT_TSD2_Msk (0b00000100U) |

| General status register bit mask. | |

| #define | SBC_THERM_STAT_TSD1_Pos (1U) |

| General status register bit position. | |

| #define | SBC_THERM_STAT_TSD1_Msk (0b00000010U) |

| General status register bit mask. | |

| #define | SBC_THERM_STAT_TPW_Pos (0U) |

| General status register bit position. | |

| #define | SBC_THERM_STAT_TPW_Msk (0b00000001U) |

| General status register bit mask. | |

| #define | SBC_DEV_STAT_DEV_STAT_Pos (6U) |

| General status register bit position. | |

| #define | SBC_DEV_STAT_DEV_STAT_Msk (0b11000000U) |

| General status register bit mask. | |

| #define | SBC_DEV_STAT_WD_FAIL_Pos (2U) |

| General status register bit position. | |

| #define | SBC_DEV_STAT_WD_FAIL_Msk (0b00001100U) |

| General status register bit mask. | |

| #define | SBC_DEV_STAT_SPI_FAIL_Pos (1U) |

| General status register bit position. | |

| #define | SBC_DEV_STAT_SPI_FAIL_Msk (0b00000010U) |

| General status register bit mask. | |

| #define | SBC_DEV_STAT_FAILURE_Pos (0U) |

| General status register bit position. | |

| #define | SBC_DEV_STAT_FAILURE_Msk (0b00000001U) |

| General status register bit mask. | |

| #define | SBC_BUS_STAT_CANTO_Pos (4U) |

| General status register bit position. | |

| #define | SBC_BUS_STAT_CANTO_Msk (0b00010000U) |

| General status register bit mask. | |

| #define | SBC_BUS_STAT_SYSERR_Pos (3U) |

| General status register bit position. | |

| #define | SBC_BUS_STAT_SYSERR_Msk (0b00001000U) |

| General status register bit mask. | |

| #define | SBC_BUS_STAT_CAN_FAIL_Pos (1U) |

| General status register bit position. | |

| #define | SBC_BUS_STAT_CAN_FAIL_Msk (0b00000110U) |

| General status register bit mask. | |

| #define | SBC_BUS_STAT_VCAN_UV_Pos (0U) |

| General status register bit position. | |

| #define | SBC_BUS_STAT_VCAN_UV_Msk (0b00000001U) |

| General status register bit mask. | |

| #define | SBC_WK_STAT_0_CAN_WU_Pos (5U) |

| General status register bit position. | |

| #define | SBC_WK_STAT_0_CAN_WU_Msk (0b00100000U) |

| General status register bit mask. | |

| #define | SBC_WK_STAT_0_TIMER_WU_Pos (4U) |

| General status register bit position. | |

| #define | SBC_WK_STAT_0_TIMER_WU_Msk (0b00010000U) |

| General status register bit mask. | |

| #define | SBC_WK_STAT_0_WK_WU_Pos (0U) |

| General status register bit position. | |

| #define | SBC_WK_STAT_0_WK_WU_Msk (0b00000001U) |

| General status register bit mask. | |

| #define | SBC_WK_STAT_1_GPIO_WK_WU_Pos (4U) |

| General status register bit position. | |

| #define | SBC_WK_STAT_1_GPIO_WK_WU_Msk (0b00010000U) |

| General status register bit mask. | |

| #define | SBC_WK_LVL_STAT_SBC_DEV_LVL_Pos (7U) |

| General status register bit position. | |

| #define | SBC_WK_LVL_STAT_SBC_DEV_LVL_Msk (0b10000000U) |

| General status register bit mask. | |

| #define | SBC_WK_LVL_STAT_CFG0_STATE_Pos (6U) |

| General status register bit position. | |

| #define | SBC_WK_LVL_STAT_CFG0_STATE_Msk (0b01000000U) |

| General status register bit mask. | |

| #define | SBC_WK_LVL_STAT_GPIO_LVL_Pos (4U) |

| General status register bit position. | |

| #define | SBC_WK_LVL_STAT_GPIO_LVL_Msk (0b00010000U) |

| General status register bit mask. | |

| #define | SBC_WK_LVL_STAT_WK_LVL_Pos (0U) |

| General status register bit position. | |

| #define | SBC_WK_LVL_STAT_WK_LVL_Msk (0b00000001U) |

| General status register bit mask. | |

| #define | SBC_GPIO_OC_STAT_GPIO_OC_Pos (6U) |

| General status register bit position. | |

| #define | SBC_GPIO_OC_STAT_GPIO_OC_Msk (0b01000000U) |

| General status register bit mask. | |

| #define | SBC_GPIO_OL_STAT_GPIO_OL_Pos (6U) |

| General status register bit position. | |

| #define | SBC_GPIO_OL_STAT_GPIO_OL_Msk (0b01000000U) |

| General status register bit mask. | |

| #define | SBC_SWK_STAT_SYNC_Pos (6U) |

| Selective wake status register bit position. | |

| #define | SBC_SWK_STAT_SYNC_Msk (0b01000000U) |

| Selective wake status register bit mask. | |

| #define | SBC_SWK_STAT_CANSIL_Pos (3U) |

| Selective wake status register bit position. | |

| #define | SBC_SWK_STAT_CANSIL_Msk (0b00001000U) |

| Selective wake status register bit mask. | |

| #define | SBC_SWK_STAT_SWK_SET_Pos (2U) |

| Selective wake status register bit position. | |

| #define | SBC_SWK_STAT_SWK_SET_Msk (0b00000100U) |

| Selective wake status register bit mask. | |

| #define | SBC_SWK_STAT_WUP_Pos (1U) |

| Selective wake status register bit position. | |

| #define | SBC_SWK_STAT_WUP_Msk (0b00000010U) |

| Selective wake status register bit mask. | |

| #define | SBC_SWK_STAT_WUF_Pos (0U) |

| Selective wake status register bit position. | |

| #define | SBC_SWK_STAT_WUF_Msk (0b00000001U) |

| Selective wake status register bit mask. | |

| #define | SBC_SWK_ECNT_STAT_ECNT_Pos (0U) |

| Selective wake status register bit position. | |

| #define | SBC_SWK_ECNT_STAT_ECNT_Msk (0b00111111U) |

| Selective wake status register bit mask. | |

| #define | SBC_SWK_CDR_STAT1_NAVG_SAT_Pos (0U) |

| Selective wake status register bit position. | |

| #define | SBC_SWK_CDR_STAT1_NAVG_SAT_Msk (0b11111111U) |

| Selective wake status register bit mask. | |

| #define | SBC_SWK_CDR_STAT2_NAVG_SAT_Pos (4U) |

| Selective wake status register bit position. | |

| #define | SBC_SWK_CDR_STAT2_NAVG_SAT_Msk (0b11110000U) |

| Selective wake status register bit mask. | |

| #define | SBC_FAM_PROD_STAT_FAM_Pos (4U) |

| Family and product register bit position. | |

| #define | SBC_FAM_PROD_STAT_FAM_Msk (0b11110000U) |

| Family and product register bit mask. | |

| #define | SBC_FAM_PROD_STAT_PROD_Pos (0U) |

| Family and product register bit position. | |

| #define | SBC_FAM_PROD_STAT_PROD_Msk (0b00001111U) |

| Family and product register bit mask. | |

Detailed Description

Main header declaration file for TLE94x1 SBC family device.

- Version

- V1.0.0

- Date

- 15. April 2019