|

| #define | SBC_ISR_VECTOR(REG, MASK, POS, COMPARE) ((((uint32_t)REG) << 24) | (((uint32_t)MASK) << 16) | (((uint32_t)POS) << 8) | ((uint32_t)COMPARE)) |

| | Vector defining the handling of interrupts. More...

|

| |

|

#define | SBC_ISR_CAN_WU SBC_ISR_VECTOR(SBC_WK_STAT_0, SBC_WK_STAT_0_CAN_WU_Msk, SBC_WK_STAT_0_CAN_WU_Pos, SBC_CAN_WU_EVENT) |

| |

|

#define | SBC_ISR_TIMER_WU SBC_ISR_VECTOR(SBC_WK_STAT_0, SBC_WK_STAT_0_TIMER_WU_Msk, SBC_WK_STAT_0_TIMER_WU_Pos, SBC_TIMER_WU_EVENT) |

| |

|

#define | SBC_ISR_WK_WU SBC_ISR_VECTOR(SBC_WK_STAT_0, SBC_WK_STAT_0_WK_WU_Msk, SBC_WK_STAT_0_WK_WU_Pos, SBC_WK_WU_EVENT) |

| |

|

#define | SBC_ISR_GPIO_WK_WU SBC_ISR_VECTOR(SBC_WK_STAT_1, SBC_WK_STAT_1_GPIO_WK_WU_Msk, SBC_WK_STAT_1_GPIO_WK_WU_Pos, SBC_GPIO_WK_WU_EVENT) |

| |

|

#define | SBC_ISR_VS_UV SBC_ISR_VECTOR(SBC_SUP_STAT_1, SBC_SUP_STAT_1_VS_UV_Msk, SBC_SUP_STAT_1_VS_UV_Pos, SBC_VS_UV_EVENT) |

| |

|

#define | SBC_ISR_VS_OV SBC_ISR_VECTOR(SBC_SUP_STAT_1, SBC_SUP_STAT_1_VS_OV_Msk, SBC_SUP_STAT_1_VS_OV_Pos, SBC_VS_OV_EVENT) |

| |

|

#define | SBC_ISR_VCC1_OV SBC_ISR_VECTOR(SBC_SUP_STAT_1, SBC_SUP_STAT_1_VCC1_OV_Msk, SBC_SUP_STAT_1_VCC1_OV_Pos, SBC_VCC1_OV_EVENT) |

| |

|

#define | SBC_ISR_VCC1_UV_PREWARN SBC_ISR_VECTOR(SBC_SUP_STAT_1, SBC_SUP_STAT_1_VCC1_WARN_Msk, SBC_SUP_STAT_1_VCC1_WARN_Pos, SBC_VCC1_UV_PREWARN_EVENT) |

| |

|

#define | SBC_ISR_VCC2_OT SBC_ISR_VECTOR(SBC_SUP_STAT_0, SBC_SUP_STAT_0_VCC2_OT_Msk, SBC_SUP_STAT_0_VCC2_OT_Pos, SBC_VCC2_OT_EVENT) |

| |

|

#define | SBC_ISR_VCC2_UV SBC_ISR_VECTOR(SBC_SUP_STAT_0, SBC_SUP_STAT_0_VCC2_UV_Msk, SBC_SUP_STAT_0_VCC2_UV_Pos, SBC_VCC2_UV_EVENT) |

| |

|

#define | SBC_ISR_VCC1_UV SBC_ISR_VECTOR(SBC_SUP_STAT_0, SBC_SUP_STAT_0_VCC1_UV_Msk, SBC_SUP_STAT_0_VCC1_UV_Pos, SBC_VCC1_UV_EVENT) |

| |

|

#define | SBC_ISR_TSD2_SAFESTATE SBC_ISR_VECTOR(SBC_THERM_STAT, SBC_THERM_STAT_TSD2_SAFE_Msk, SBC_THERM_STAT_TSD2_SAFE_Pos, SBC_TSD2_SAFE_SAFESTATE_DETECTED) |

| |

|

#define | SBC_ISR_TSD1 SBC_ISR_VECTOR(SBC_THERM_STAT, SBC_THERM_STAT_TSD1_Msk, SBC_THERM_STAT_TSD1_Pos, SBC_TSD1_EVENT) |

| |

|

#define | SBC_ISR_TPW SBC_ISR_VECTOR(SBC_THERM_STAT, SBC_THERM_STAT_TPW_Msk, SBC_THERM_STAT_TPW_Pos, SBC_TPW_EVENT) |

| |

|

#define | SBC_ISR_RESTART_AFTER_FAIL SBC_ISR_VECTOR(SBC_DEV_STAT, SBC_DEV_STAT_DEV_STAT_Msk, SBC_DEV_STAT_DEV_STAT_Pos, SBC_DEV_STAT_RESTART_AFTER_FAIL) |

| |

|

#define | SBC_ISR_FROM_SLEEPMODE SBC_ISR_VECTOR(SBC_DEV_STAT, SBC_DEV_STAT_DEV_STAT_Msk, SBC_DEV_STAT_DEV_STAT_Pos, SBC_DEV_STAT_SLEEP_MODE) |

| |

|

#define | SBC_ISR_WD_FAIL_1 SBC_ISR_VECTOR(SBC_DEV_STAT, SBC_DEV_STAT_WD_FAIL_Msk, SBC_DEV_STAT_WD_FAIL_Pos, SBC_WD_FAIL_1FAIL) |

| |

|

#define | SBC_ISR_WD_FAIL_2 SBC_ISR_VECTOR(SBC_DEV_STAT, SBC_DEV_STAT_WD_FAIL_Msk, SBC_DEV_STAT_WD_FAIL_Pos, SBC_WD_FAIL_2FAIL) |

| |

|

#define | SBC_ISR_FAILURE SBC_ISR_VECTOR(SBC_DEV_STAT, SBC_DEV_STAT_FAILURE_Msk, SBC_DEV_STAT_FAILURE_Pos, SBC_FAILURE_EVENT) |

| |

|

#define | SBC_ISR_CAN_TSD SBC_ISR_VECTOR(SBC_BUS_STAT, SBC_BUS_STAT_CAN_FAIL_Msk, SBC_BUS_STAT_CAN_FAIL_Pos, SBC_CAN_FAIL_TSD) |

| |

|

#define | SBC_ISR_CAN_TXD_DOM_TO SBC_ISR_VECTOR(SBC_BUS_STAT, SBC_BUS_STAT_CAN_FAIL_Msk, SBC_BUS_STAT_CAN_FAIL_Pos, SBC_CAN_FAIL_TXD_DOM_TO) |

| |

|

#define | SBC_ISR_CAN_BUS_DOM_TO SBC_ISR_VECTOR(SBC_BUS_STAT, SBC_BUS_STAT_CAN_FAIL_Msk, SBC_BUS_STAT_CAN_FAIL_Pos, SBC_CAN_FAIL_BUS_DOM_TO) |

| |

|

#define | SBC_ISR_VCAN_UV SBC_ISR_VECTOR(SBC_BUS_STAT, SBC_BUS_STAT_VCAN_UV_Msk, SBC_BUS_STAT_VCAN_UV_Pos, SBC_VCAN_UV_EVENT) |

| |

|

#define | SBC_ISR_GPIO_OC SBC_ISR_VECTOR(SBC_GPIO_OC_STAT, SBC_GPIO_OC_STAT_GPIO_OC_Msk, SBC_GPIO_OC_STAT_GPIO_OC_Pos, SBC_GPIO_OC_EVENT) |

| |

|

#define | SBC_ISR_GPIO_OL SBC_ISR_VECTOR(SBC_GPIO_OL_STAT, SBC_GPIO_OL_STAT_GPIO_OL_Msk, SBC_GPIO_OL_STAT_GPIO_OL_Pos, SBC_GPIO_OL_EVENT) |

| |

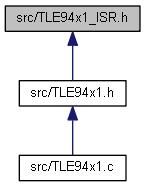

Declaration file for ISR-Vectors and ISR related functions.

- Version

- V1.0.0

- Date

- 15. April 2019

- Author

- Markus Noll / marku.nosp@m.s.no.nosp@m.ll@in.nosp@m.fine.nosp@m.on.co.nosp@m.m

-

Yannek Micha Rixen / Yanne.nosp@m.k.Ri.nosp@m.xen@i.nosp@m.nfin.nosp@m.eon.c.nosp@m.om